將圖像處理的算法轉(zhuǎn)換為FPGA系統(tǒng)設(shè)計(jì)的過程稱為算法映射,CPU并行算法的實(shí)現(xiàn)與FPGA并行算法的實(shí)現(xiàn)是有一定區(qū)別的。1.算法系統(tǒng)結(jié)構(gòu)

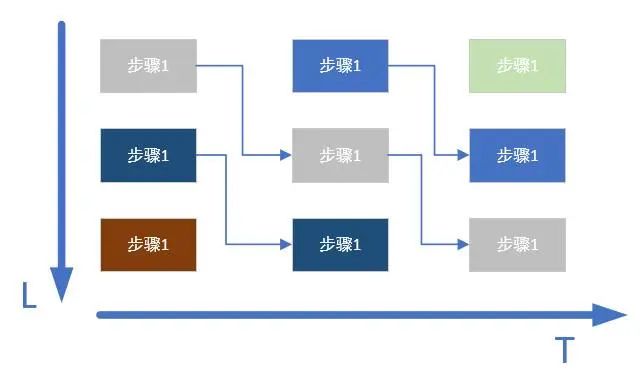

圖像處理算法主要有兩種設(shè)計(jì)結(jié)構(gòu):流水線結(jié)構(gòu)和并行陣列結(jié)構(gòu)。

1.1 流水線結(jié)構(gòu)

在我看來,流水線結(jié)構(gòu)和我們之前所理解的CPU的串行結(jié)構(gòu)還是有一定區(qū)別的。相反,它與處理器的流水線結(jié)構(gòu)很相似,都是依照時(shí)鐘來進(jìn)行流水層級(jí)的同步。

1.2并行陣列結(jié)構(gòu) |--Data1--->Data1-->Data1

|

InputData------Data2--->Data2-->Data2

|

|--Data3--->Data3-->Data32.算法轉(zhuǎn)換2.1 定常數(shù)轉(zhuǎn)換

對(duì)于FPGA而言,做加法與移位較為簡(jiǎn)單,而涉及到乘法與除法時(shí)需要調(diào)用到乘法器或除法器,這在FPGA中是較為寶貴的資源,所以作為定常數(shù),我們盡量轉(zhuǎn)換為移位和加法運(yùn)算,如:

ex1:

dout = din * 255

轉(zhuǎn)換后

dout = ( din << 8 ) - din

ex2:

dout = din * 11

轉(zhuǎn)換后:

dout = din * 2^2 + din * 2^3 - din * 2^0

= din * (2^2 + 2^3 - 2^0)

上式中的255 和 11就是定常數(shù)

2.2 不等式等效轉(zhuǎn)換

進(jìn)行轉(zhuǎn)換的目的也是為了在FPGA實(shí)現(xiàn)后能夠更加節(jié)省資源。如:

ex1:

√a ̄ < b, a > 0

轉(zhuǎn)換后:

b^2 > a

ex2:

a/b > c/b (b > 0, d > 0)

轉(zhuǎn)換后

a * d > b * c2.3 取近似值

最簡(jiǎn)單的近似值莫過于四舍五入,假如某數(shù)據(jù)D[-1~4]為整數(shù)部分,D[3~0]為小數(shù)部分,那么四舍五入可為:

assign dout = din[3]?(dout[-1~4] + 1) : (dout[-1~4])

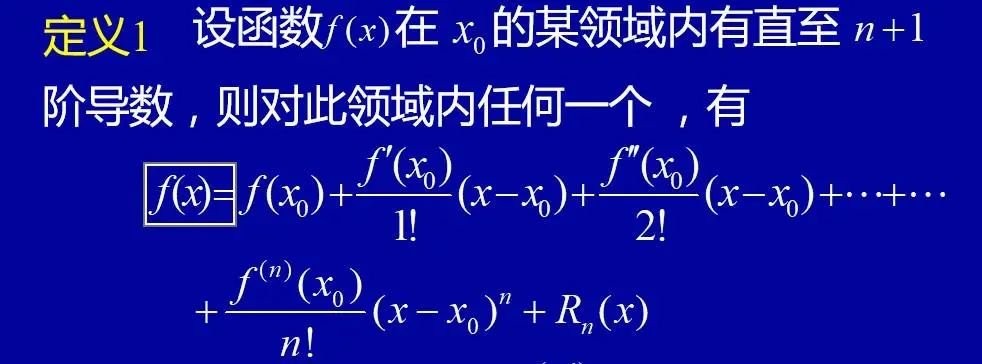

泰勒公式定義

那么就可以有如下近似轉(zhuǎn)換:

1/3 = 1/4 * (1 + 1/4 + 1/16 + 1/64 + 1/256) 3.構(gòu)造查找表

查找表是使用簡(jiǎn)單的查詢操作代替運(yùn)行時(shí)的實(shí)時(shí)計(jì)算,使用查找表代替那些運(yùn)行時(shí)經(jīng)常需要用到的運(yùn)算能夠極大的減少時(shí)間復(fù)雜度,如我們經(jīng)常用到的三角函數(shù)就應(yīng)該使用查找表替換實(shí)時(shí)計(jì)算。

有你想看的精彩 至芯科技FPGA就業(yè)培訓(xùn)班——助你步入成功之路、9月23號(hào)北京中心開課、歡迎咨詢! 為什么要使用格雷碼? 簡(jiǎn)述基于EDA技術(shù)的FPGA設(shè)計(jì)

掃碼加微信邀請(qǐng)您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:FPGA算法映射要點(diǎn)

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613940

原文標(biāo)題:FPGA算法映射要點(diǎn)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Profibus DP主站網(wǎng)關(guān)數(shù)據(jù)映射全解析!

FPGA算法映射要點(diǎn)

FPGA算法映射要點(diǎn)

評(píng)論