本文開源一個FPGA項目:UDP萬兆光通信。該項目實現了萬兆光纖以太網數據回環傳輸功能。Vivado工程代碼結構和之前開源的《UDP RGMII千兆以太網》類似,只不過萬兆以太網是調用了Xilinx的10G Ethernet Subsystem IP核實現。由于該IP核需要付費使用,本文提供完整工程源碼。

下面圍繞該IP核的使用、用戶接口,以及數據傳輸方案展開介紹。

01軟硬件平臺

- 軟件平臺:Vivado 2017.4;

- 硬件平臺:XC7Z035FFG676-2;

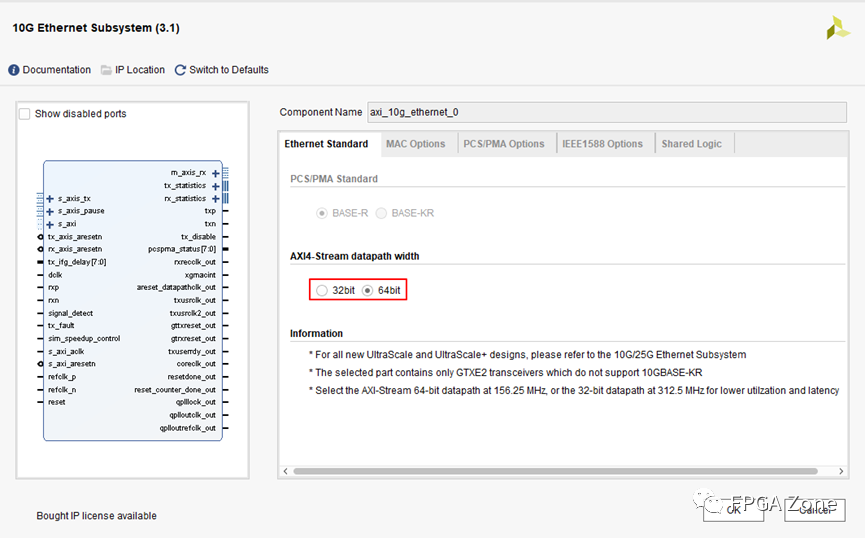

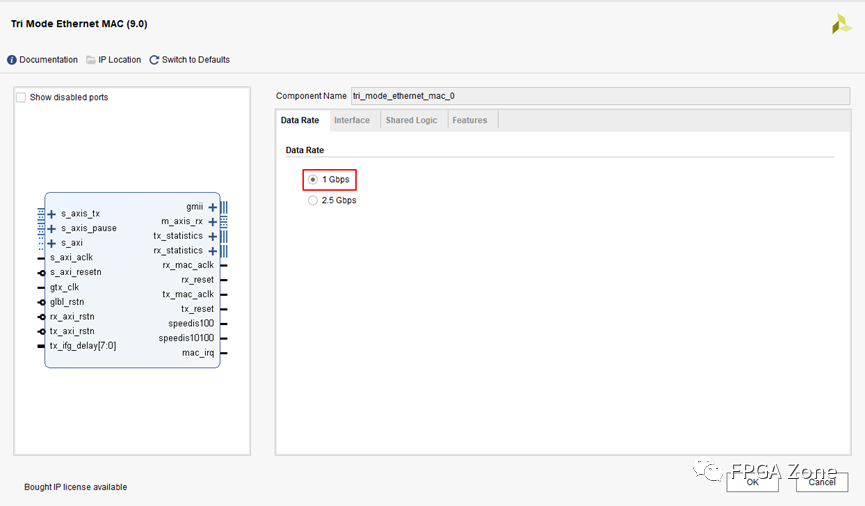

02IP核參數配置

AXI4-Stream數據位寬 : 選擇64bits。對應的用戶接口時鐘頻率為156.25MHZ。

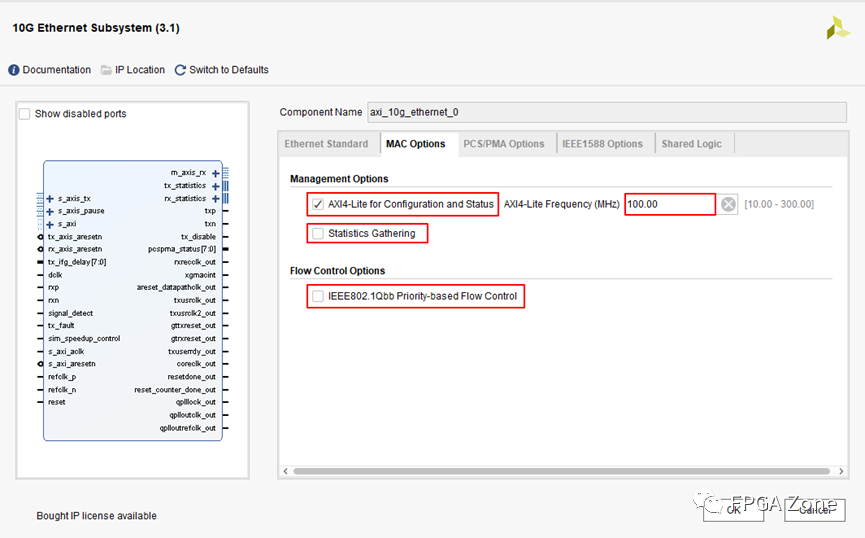

MAC Options : 選擇使用AXI-Lite接口對IP核寄存器進行配置,同時需要設置時鐘頻率,這里設置為100MHZ(該設置僅對IP核out-of-context模式的綜合有效);不使用參數統計和優先級流量控制功能。

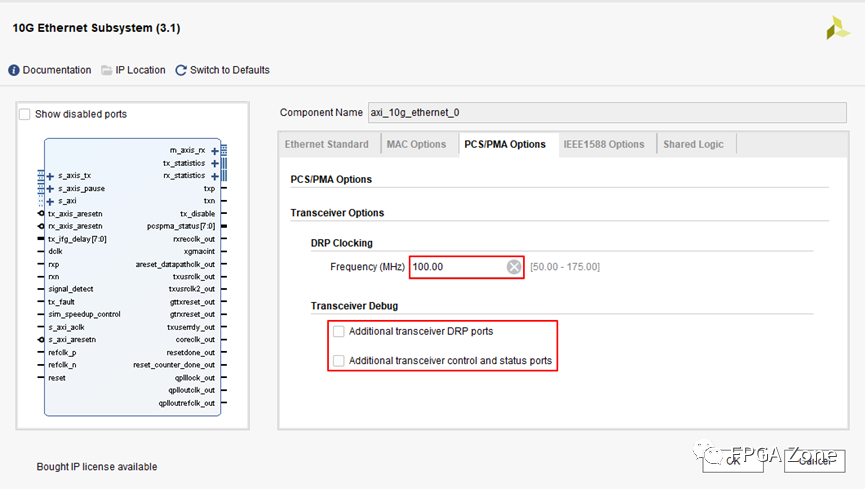

PCS/PMA Options: 配置GTX動態重配置端口DRP時鐘為100MHZ(該設置同樣僅對IP核out-of-context模式的綜合有效);不使用Transceiver Debug功能。

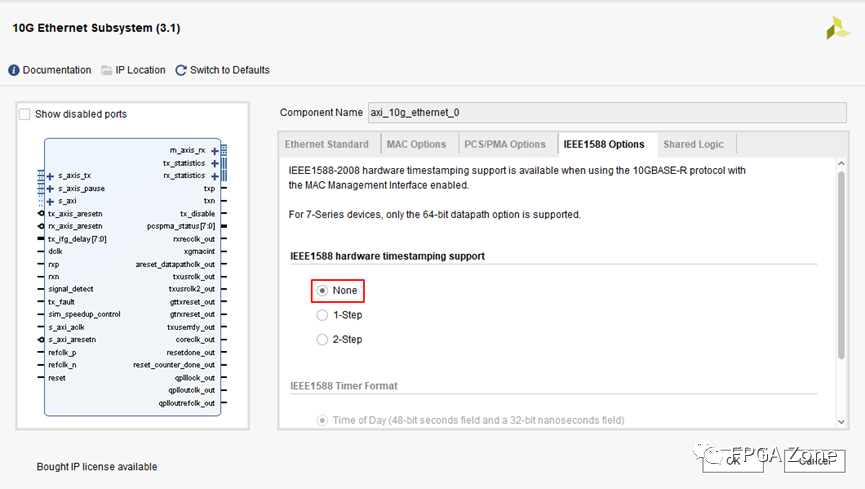

IEEE1588 Options: IEEE1588功能一般用于某些需要進行網絡時間同步的場合,例如音(視)頻傳輸。在本項目中只是進行數據傳輸,因此可以不選擇使用。

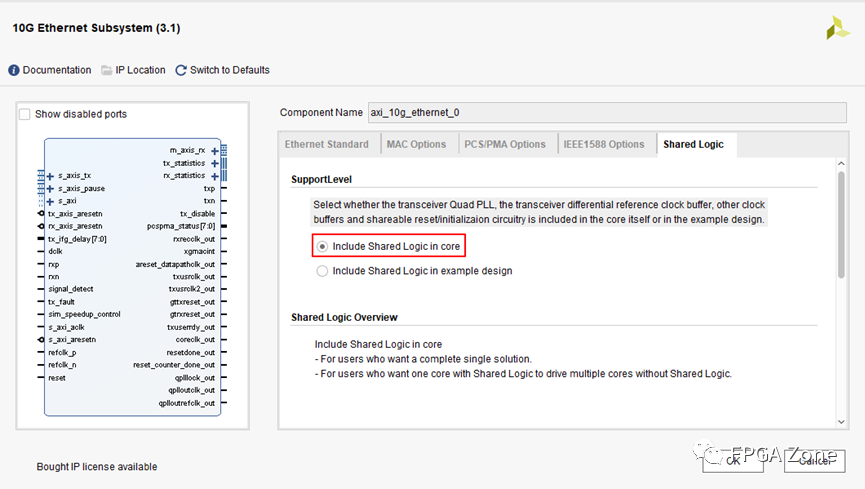

Shared Logic: 由于在此項目Vivado工程中只需例化一個該IP核,因此這里選擇Include Shared Logic in core,將共享資源包含在IP內部即可。如果需要例化多個該IP核,只需將其中一個IP核配置為Include Shared Logic in core,其余的都配置為Include Shared Logic in example design。

03用戶接口

- AXI-Stream發送接口

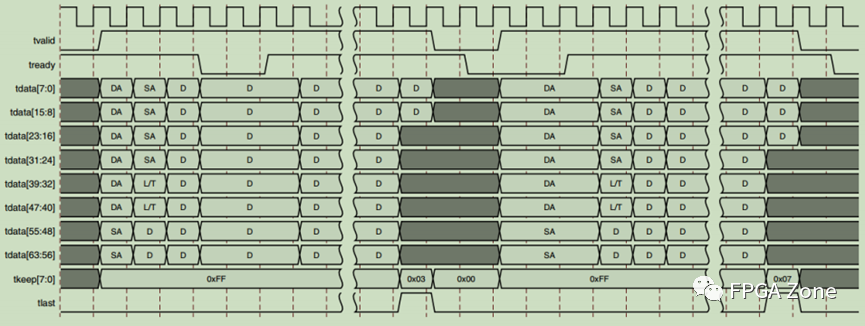

用戶通過該接口將要發送的以太網數據包寫入IP核。另外,由tx_ifg_delay接口控制發送間隔,將其配置為0即可。AXI-Stream發送接口時序如下圖所示。

- AXI-Stream接收接口

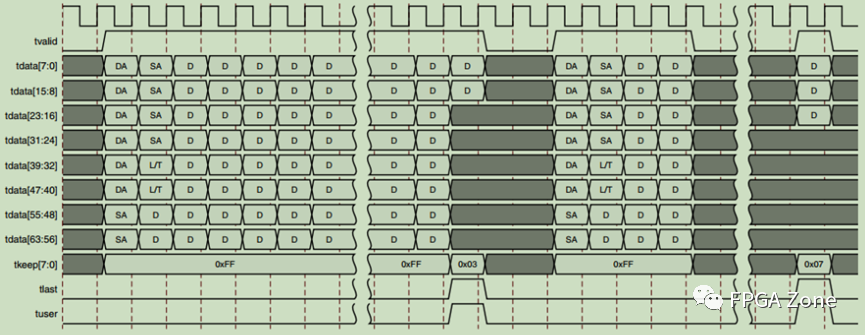

用戶通過該接口讀取IP核輸出的以太網數據包。AXI-Stream接收接口時序如下圖所示。

- Pcspma-Status接口

該接口用于輸出IP核內部PCS PMA部分工作狀態,在該工程中只有第0bit有效,用于指示PCS Block Lock。

- Sim-Speed-Up接口

該接口只在仿真時會用到,用于加快仿真速度,在該工程中將其設置為0即可。

- Optical模塊接口

signal_detect:光模塊狀態指示信號,配置為1;

tx_fault:光模塊狀態指示信號,配置為0;

tx_disable:輸出光模塊控制信號。

- Flow-Control接口

在高帶寬、大負荷傳輸場合,一般需要流量控制功能。在該工程不需要發送暫停幀,因此將以下兩個信號設置為0。

s_axis_pause_tvalid & s_axis_pause_tdata。

- AXI-Lite接口

該接口用于讀寫IP核內部寄存器,通過對IP核各參數進行配置,以實現基本的以太網數據包收發功能。

04數據傳輸方案及測試

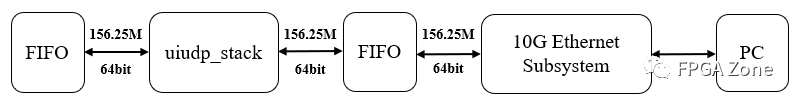

該項目的功能主要用于實現萬兆以太網光纖數據回環傳輸,在電腦端通過網絡調試助手向FPGA發送數據包,FPGA端接收、緩存數據包后回傳給上位機。以太網數據回環傳輸方案如下圖所示。

其中,時鐘為156.25MHZ,數據位寬為64bits。在UDP IP核和10G Ethernet Subsystem IP核之間,通過插入FIFO實現對每包以太網數據流的緩存功能。

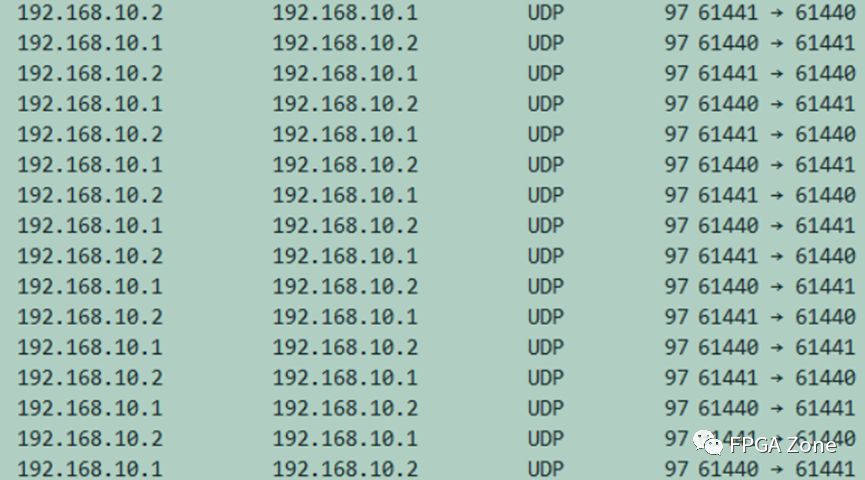

利用wireshark軟件抓取PC端和FPGA端之間以太網雙向傳輸數據包,結果如下圖所示。

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613986 -

以太網

+關注

關注

40文章

5582瀏覽量

174757 -

UDP

+關注

關注

0文章

330瀏覽量

34474 -

光通信

+關注

關注

20文章

920瀏覽量

34425 -

IP核

+關注

關注

4文章

338瀏覽量

50449

發布評論請先 登錄

把握光通信行業演變脈動 CIOE2012光通信展即將起航!

FPGA在光通信中的應用

淺析紫外光通信技術

可見光通信 調制解調技術 家庭機器人 可見光通信應用 原理及硬件方案 精選資料分享

無線光通信

無線光通信(FSO),無線光通信(FSO)的特點及原理/前景

光通信芯片的概念以及我國在光通信行業的地位

激光通信原理_激光通信的優缺點

光通信的概念 光通信優點與不足

光通信技術應用 光通信的意義

10g gtx光纖通信測試_S03-CH05_UDP萬兆光通信

基于FPGA的UDP萬兆光通信測試

基于FPGA的UDP萬兆光通信測試

評論