景芯SoC用always on的power domain電壓域的pwrdown_mux信號作為power switch cell的switch控制信號,但是設計里面有個小問題,不太算bug的bug,但對upf低功耗flow而言,毫無疑問就是bug!

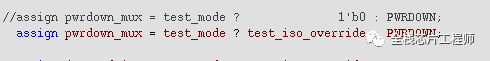

請登陸服務器追蹤一下pwrdown信號,注意其負載情況,RTL代碼如下:

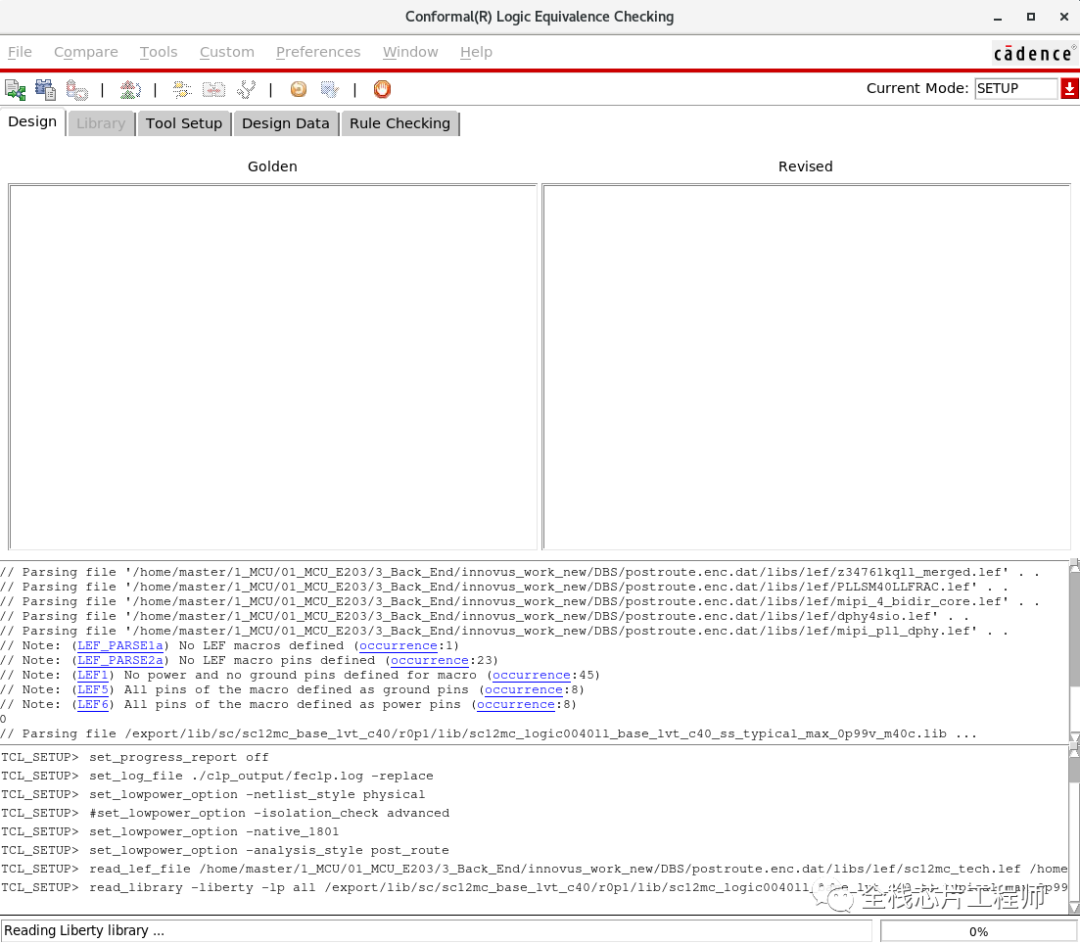

結合PR輸出的netlist, 我們做個clp低功耗檢查,腳本參見服務器。

可以發現,clp報錯說power switch的switch控制信號找不到。不得不說,clp檢查對低功耗而言多么重要,對芯片設計而言多重要!景芯SoC的價值就在把芯片設計全流程的這些細小的知識點,全部串接起來!猶豫啥?抓緊報名加入吧!

在芯片設計中端流程時,景芯SoC會插入UPF約束中的isolation等cell,但是無法插入power switch等cell,因此,作為power switch cell的控制信號pwrdown_mux在沒有負載的情況下,會被裁員掉(優化掉),因此需要設置上面MUX器件為dont_touch或者使pwrdown_mux成為module的port并禁止auto_ungroup(并設置no_boundary_optimization),這樣這個信號才能保留給后端,供后端實現power switch控制。

請學員完成代碼修改,基于全套flow環境完成如下任務:

lint檢查、前端仿真,

完成中端、后端flow,

完成clp檢查,完成后仿真

審核編輯:劉清

-

控制器

+關注

關注

114文章

16933瀏覽量

182727 -

芯片設計

+關注

關注

15文章

1059瀏覽量

55441 -

RTL

+關注

關注

1文章

388瀏覽量

60609 -

CLP

+關注

關注

0文章

5瀏覽量

7208 -

UPF

+關注

關注

0文章

50瀏覽量

13763

原文標題:UPF設計的debug過程

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

淺析UPF設計的debug過程

淺析UPF設計的debug過程

評論