ttl電路中輸入端懸空代表什么

在TTL(Transistor-Transistor Logic,晶體管-晶體管邏輯)電路中,輸入端懸空意味著輸入端沒有連接到高電平(Vcc)或低電平(地/0V)。懸空輸入可能導(dǎo)致不確定的電平狀態(tài),因此是不推薦的。

在TTL電路中,通常會將輸入端連接到確定的電平,以確保電路的可靠性。連接到高電平(Vcc)時,表示為邏輯高(1),連接到低電平(地/0V)時,表示為邏輯低(0)。如果輸入端懸空,它可能容易受到電磁干擾或漂移,導(dǎo)致電路的功能不穩(wěn)定或未定義。

為了防止輸入端懸空,可以使用電阻或其他電路來將輸入端連接到一個確定的電平。這樣可以保證輸入信號的穩(wěn)定性,并確保電路的正確操作。

ttl門電路輸入狀態(tài)怎么判斷

在TTL門電路中,輸入狀態(tài)可以通過輸入電平來判斷。根據(jù)TTL的定義,當輸入電壓低于輸入低電平(通常為0.8V)時,被視為邏輯低(0),當輸入電壓高于輸入高電平(通常為2V至5V之間)時,被視為邏輯高(1)。

要判斷輸入狀態(tài),可以使用示波器或邏輯分析儀來測量輸入引腳的電壓。如果輸入電壓高于輸入高電平,則表明輸入狀態(tài)為邏輯高;如果輸入電壓低于輸入低電平,則表明輸入狀態(tài)為邏輯低。

另外,TTL門電路還具有一些傳輸特性,比如輸入輸出轉(zhuǎn)換延遲和噪聲容限等,可以對輸入狀態(tài)做出影響。因此,在實際應(yīng)用中,需要考慮這些因素來確保正確判斷輸入狀態(tài)。

ttl電路正確接線圖圖解

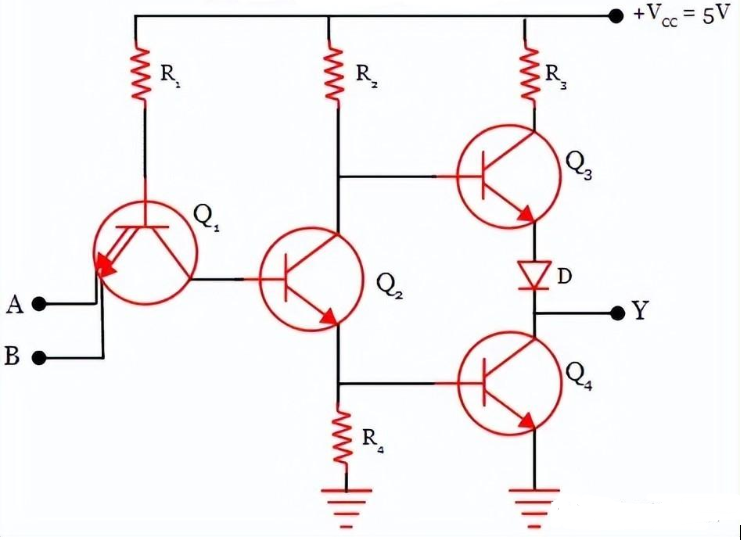

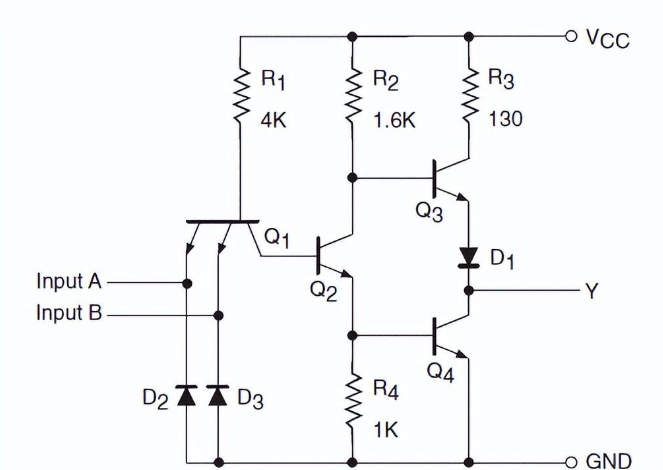

1、標準2輸入TTL電路

下圖為2輸入TTL與非門的電路圖。它有四個晶體管Q 1、Q 2、Q 3和Q 4。晶體管 Q 1在發(fā)射極側(cè)有兩個輸入端。三極管Q 3和Q 4組成輸出端,稱為圖騰柱輸出。

標準2輸入TTL電路

2 輸入 TTL 與非門的電路可能看起來很復(fù)雜。我們可以通過考慮 2 輸入 NPN 晶體管的二極管等效來簡化其操作,如下圖所示。

標準2輸入TTL電路

在圖中,二極管DA和DB代表晶體管Q 1的2輸入發(fā)射極結(jié)。二極管 DC代表晶體管 Q2的集電極-基極結(jié)。

當輸入 A 和 B 均為低電平時,兩個二極管均正向偏置。因此,由于電源電壓 +V CC = 5 V 而產(chǎn)生的電流將通過 R 1 和兩個二極管 D A 和 D B 流向地面。

電源電壓在電阻 R 1中下降 ,不足以導(dǎo)通晶體管 Q 2。隨著 Q 2打開,晶體管 Q 4也將截止。但是晶體管Q 3被拉高。由于 Q 3是射極跟隨器,因此端子的輸出也將為高電平,即邏輯 1。

當任何一個輸入(A 或 B)為低時,具有低輸入的二極管將正向偏置。將發(fā)生與上述相同的操作,在這種情況下,輸出將為高電平。

當輸入 A 和 B 均為高電平時,發(fā)射極-基極結(jié)處的兩個二極管都將反向偏置。集電極-基極結(jié)處的二極管 D C正向偏置。它將打開晶體管 Q 2。隨著Q 2導(dǎo)通,晶體管Q 4也將導(dǎo)通。

輸出端的兩個晶體管都將導(dǎo)通,因此終端輸出將具有低電平,這被視為邏輯 0。

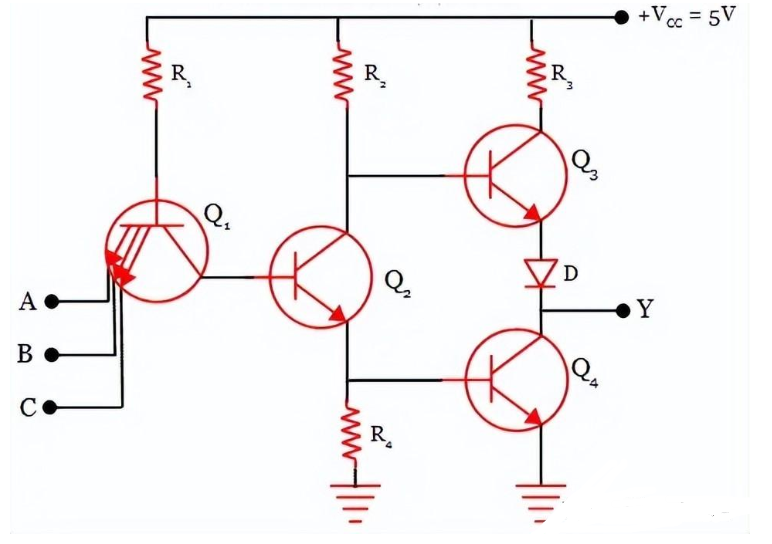

2、標準3輸入TTL與非門電路

下圖為標準3輸入TTL與非門電路。這與我們在2輸入TTL與非門電路中差不多,只是這里輸入晶體管Q 1具有三個發(fā)射極而不是兩個。工作原理與 2 輸入 TTL 與非門相同。

、標準3輸入TTL與非門電路

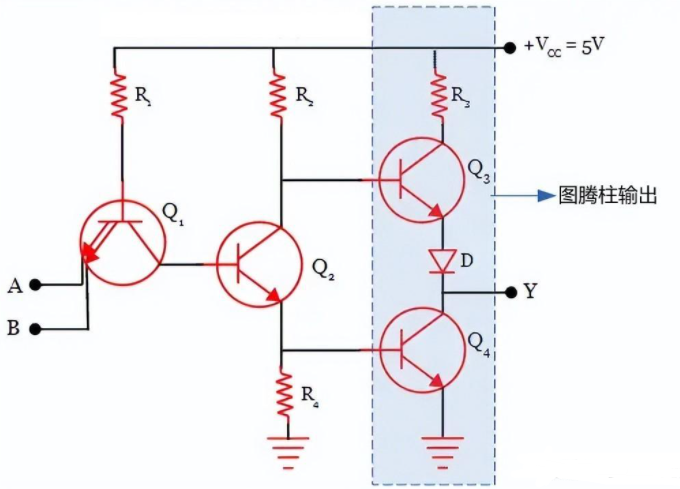

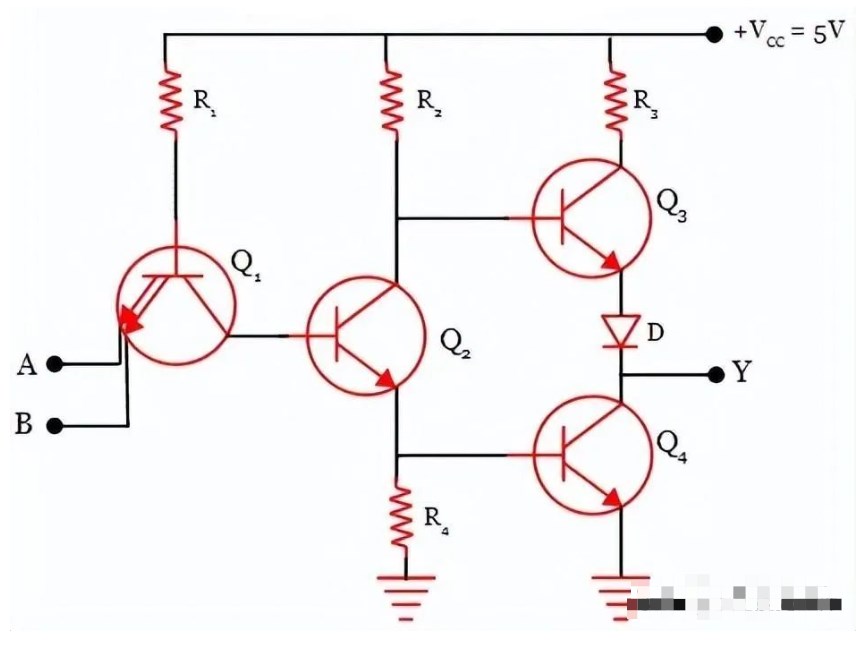

3、TTL圖騰柱輸出電路

在下圖所示的電路中,陰影部分表示圖騰柱輸出。三極管Q 3、Q 4、二極管D和限流電阻R 3構(gòu)成TTL的圖騰柱輸出結(jié)構(gòu)。

標準圖騰柱輸出,TTL電路具有以下特點和優(yōu)勢:

1、由于延遲時間短,與 DTL 相比,它們的運行速度相當高

2、抗噪性低(0.4V)

3、每個門的平均傳播延遲為 10 納秒 (ns)

4、平均功耗為 10mW

5、它的最大扇出為10,這意味著一個輸出可以驅(qū)動另外10個TTL輸入

7、與二極管相比,其中應(yīng)用的多發(fā)射極晶體管占用的空間相對較小

8、該系列價格相對便宜,市場上大量供應(yīng)

9、應(yīng)用簡單易行

10、圖騰柱晶體管在二進制 1(高)狀態(tài)下提供非常低的輸出阻抗

11、TTL 設(shè)備是兼容的(即一個 TTL 設(shè)備的輸出可以作為輸入提供給另一個 TTL 設(shè)備。在這種情況下,第一個設(shè)備稱為驅(qū)動器,而第二個稱為負載)

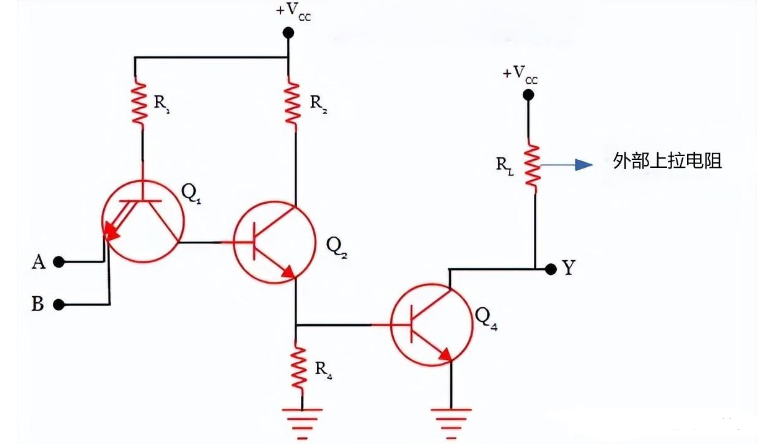

4、TTL集電極開路輸出電路

TTL邏輯的集電極開路輸出配置如下圖所示。在此配置中,取消了晶體管 Q 3和上拉電阻。取而代之的是外部上拉電阻以確保正常運行,如圖所示。

TTL集電極開路輸出

輸出取自 Q 4的集電極開路端子。當晶體管 Q 4關(guān)閉時,輸出 Y 將為高電平,而當 Q 4導(dǎo)通時,輸出將為低電平。

5、TTL三態(tài)門輸出電路

在這種輸出配置下操作晶體管時,可以獲得高阻抗。三種輸出狀態(tài)是:高、低和高阻抗。

三態(tài)邏輯電路利用圖騰柱排列的高速運行,同時允許輸出進行線與運算(連接在一起)。Hi-Z 狀態(tài)是圖騰柱排列中的兩個晶體管都關(guān)閉的狀態(tài),因此輸出端對地和 V CC為高阻抗。換句話說,輸出是一個開路或浮動終端,既不是低電平也不是高電平。實際上,輸出端并不是完全開路,而是相對于地和 V CC具有幾 MΩ 或更高的高電阻。

TTL三態(tài)門輸出電路

上圖顯示了三態(tài)逆變器的電路,該電路有兩個輸入:A 是正常邏輯輸入,F(xiàn) 是能夠產(chǎn)生 Hi-Z 狀態(tài)的啟用輸入。

當 F = 0 時,無論邏輯輸入 A 的狀態(tài)如何,電路都會進入其高阻抗狀態(tài)。F 處的低電平正向偏置晶體管 Q 1 的發(fā)射極-基極結(jié),并使電阻 R1 的電流從晶體管Q分流2使 Q 2關(guān)斷,從而使晶體管 Q 4關(guān)斷。E 處的低電平還正向偏置二極管 D 2以從晶體管 Q 3的基極分流電流,因此 Q 3也關(guān)閉。由于兩個圖騰柱晶體管都處于截止狀態(tài),因此輸出端基本上是開路。

具體的可以看如下真值表:F = 1 時,電路作為正常逆變器運行,因為 F 處的高輸入對晶體管 Q 1或二極管 D 2沒有影響。在此啟用條件下,輸出只是邏輯輸入的反相。

TTL三態(tài)門輸出電路真值表

TTL三態(tài)門輸出電路優(yōu)點:

高速運轉(zhuǎn),傳播延遲大約為 10 毫秒,與DTL和RTL邏輯器件相比更快。

與 DTL 和 RTL 相比功耗更低。

低成本。

更好的扇出。

噪聲可靠運行。

編輯:黃飛

-

二極管

+關(guān)注

關(guān)注

148文章

10038瀏覽量

170277 -

TTL電路

+關(guān)注

關(guān)注

2文章

65瀏覽量

15328 -

逆變器

+關(guān)注

關(guān)注

293文章

4857瀏覽量

210029 -

晶體管

+關(guān)注

關(guān)注

77文章

9977瀏覽量

140628 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2378瀏覽量

106296

發(fā)布評論請先 登錄

CMOS和TTL集成門電路多余輸入端的處理方法

CMOS和TTL集成門電路多余輸入端如何處理?

CMOS和TTL集成門電路多余輸入端如何處理?

關(guān)于TTL和CMOS門電路的邏輯輸入端輸入關(guān)系的區(qū)別/總結(jié)

ttl電路的應(yīng)用 常見的ttl電路

ttl電路中輸入端懸空代表什么 ttl電路正確接線圖圖解

ttl電路中輸入端懸空代表什么 ttl電路正確接線圖圖解

評論