vivado開發(fā)軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學者進行仿真實驗。

1、前期準備工作

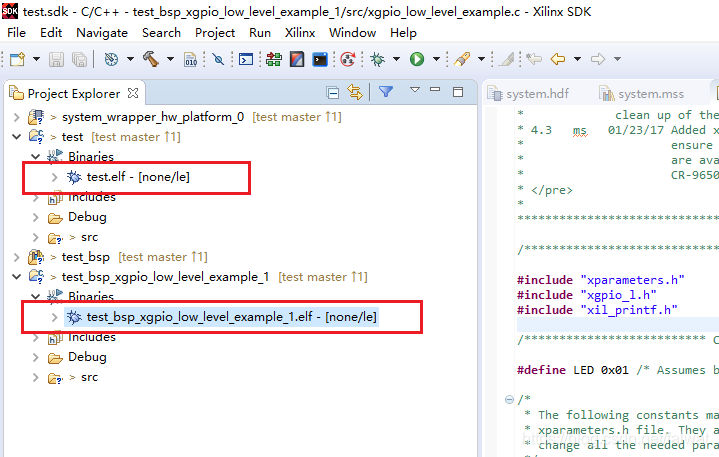

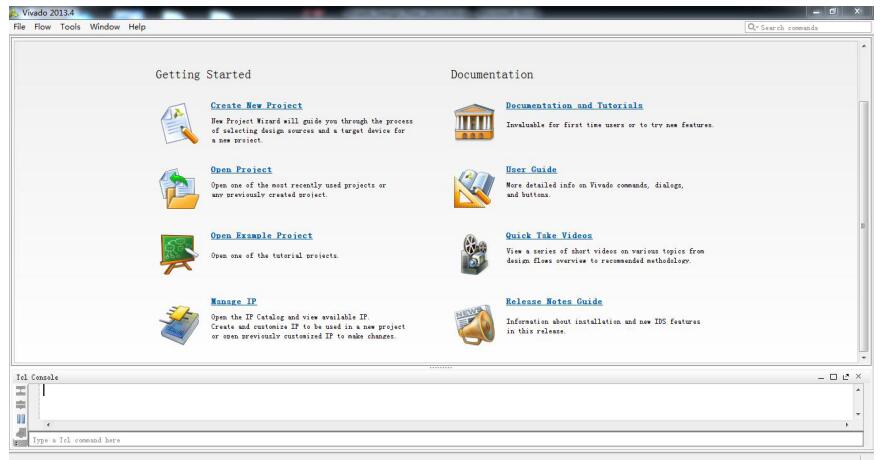

在上一篇博客中我們已經(jīng)詳細介紹了vivado建立工程的流程,有需要的朋友可以移步http://www.asorrir.com/d/2179253.html進行查看;本次我們在建立的工程基礎(chǔ)上進行仿真文件的添加和仿真演示。

2、添加仿真文件

第一步點擊Add Sources添加仿真文件,具體步驟如下:

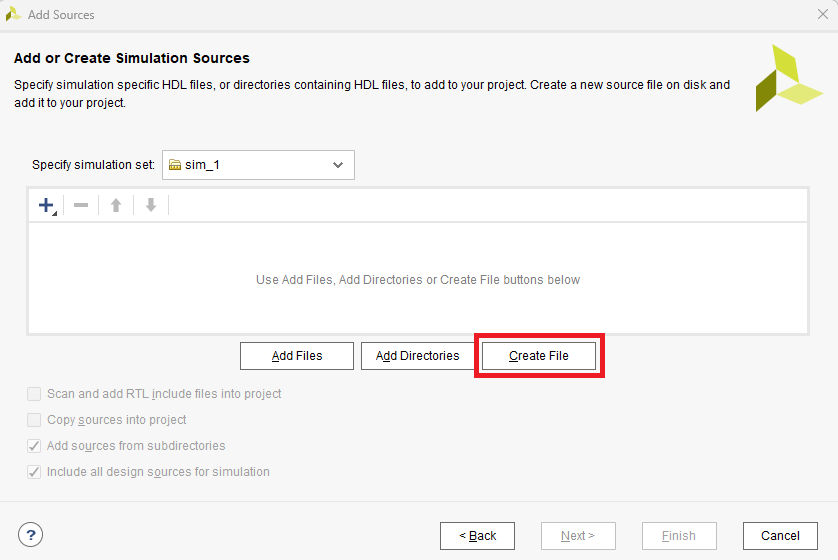

接下來點擊Add or create simulation sources,再點擊Next

點擊Create File創(chuàng)建文件

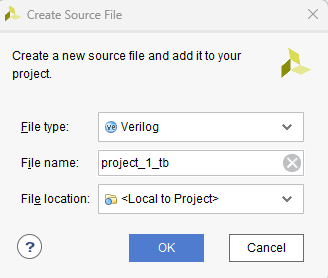

一般將其命名為文件名_tb,其中tb為testbench的縮寫,一般為仿真測試文件,再點擊OK

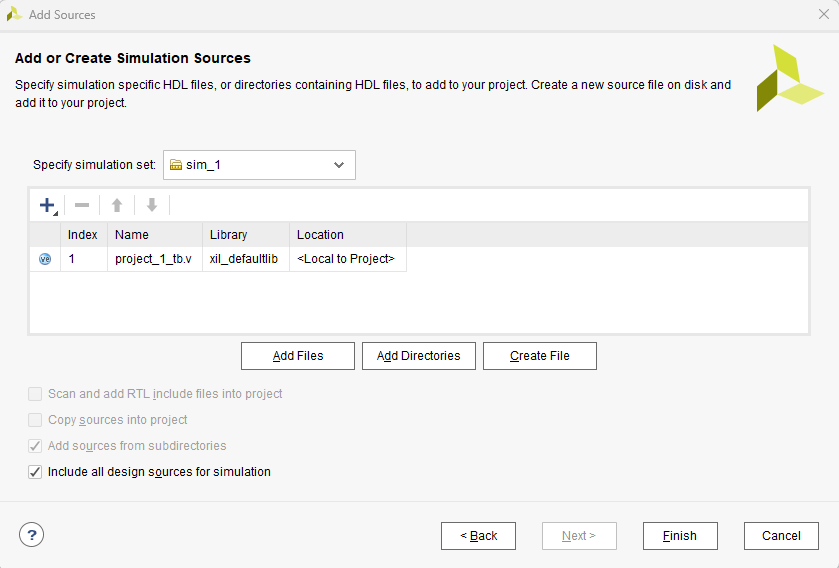

最后點擊Finish完成文件創(chuàng)建

3、編寫仿真文件代碼

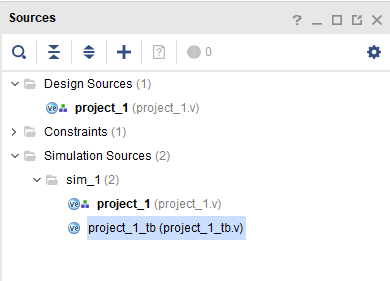

之后在sim_1文件夾下可以找到創(chuàng)建的文件

在上述部分完成仿真代碼的編寫之后點擊保存按鈕

4、進行仿真設置

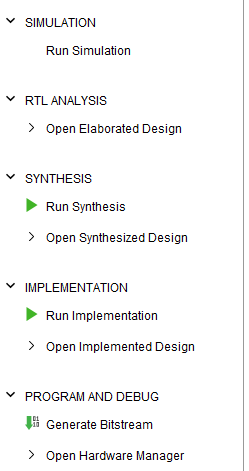

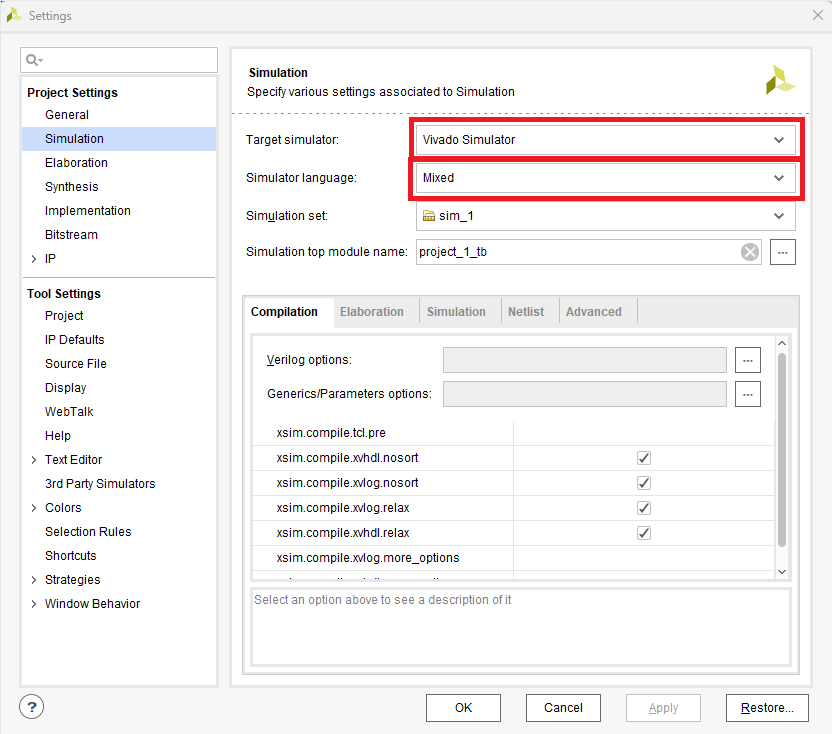

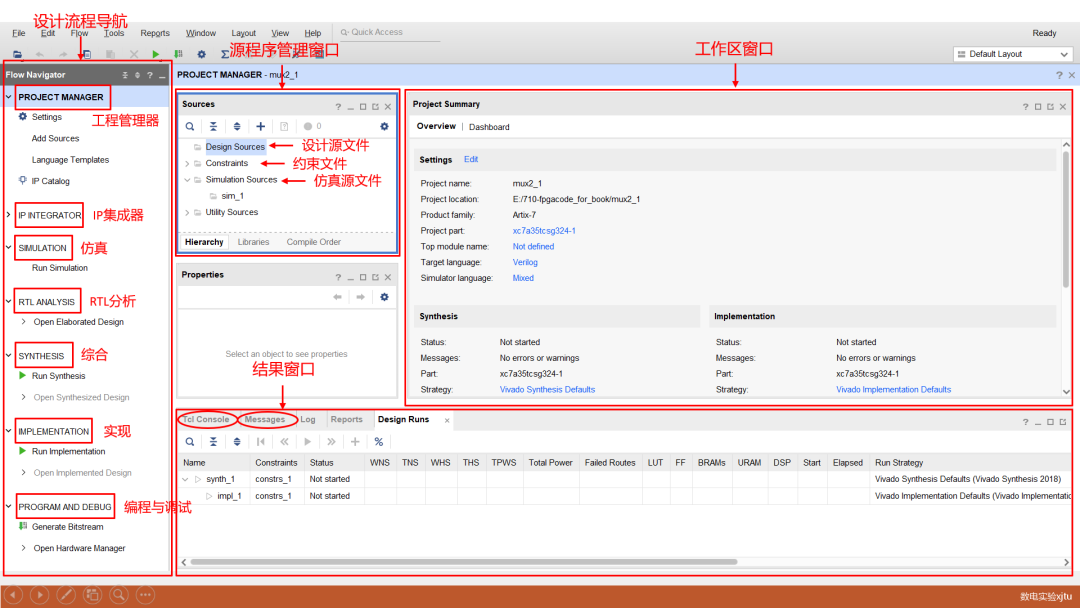

鼠標右鍵點擊SIMULATION,之后再點擊Simulation Settings

上方紅框為仿真軟件,我們選擇Vivado Simulator也即vivado自帶的仿真軟件;下方為仿真語言類型我們選擇Mixed也即混合型

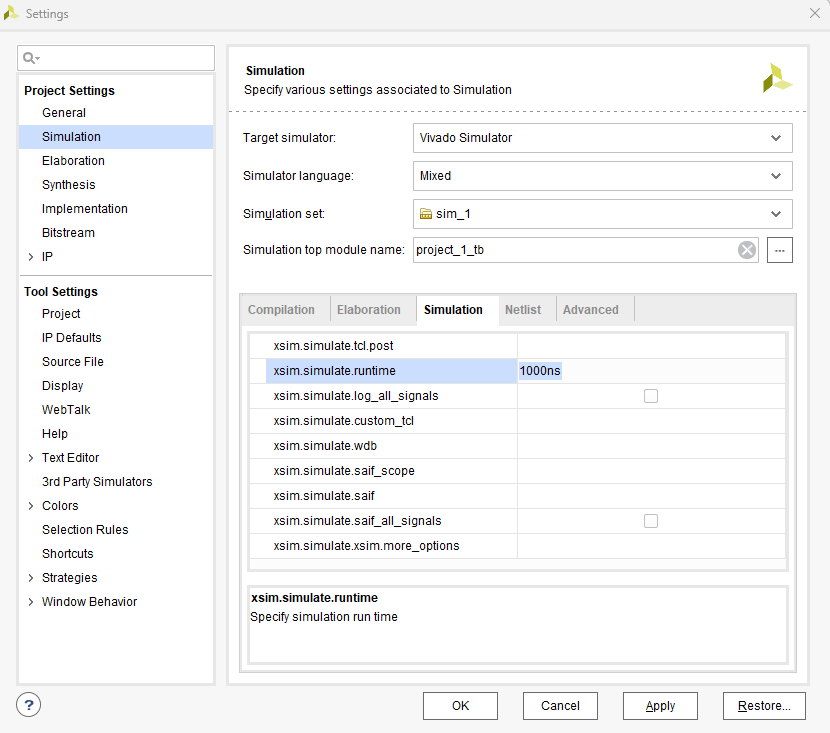

在Simulation中所示位置可以調(diào)節(jié)仿真的步進時長,此處設置為10ms;之后點擊OK完成設置

5、功能仿真

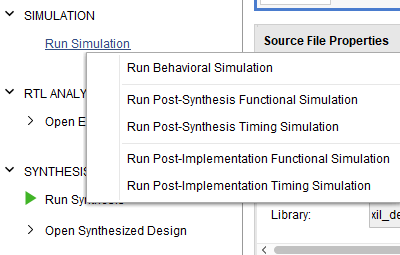

點擊Run Simulation 之后點擊第一個Run Behavioral Simulation 進行功能仿真

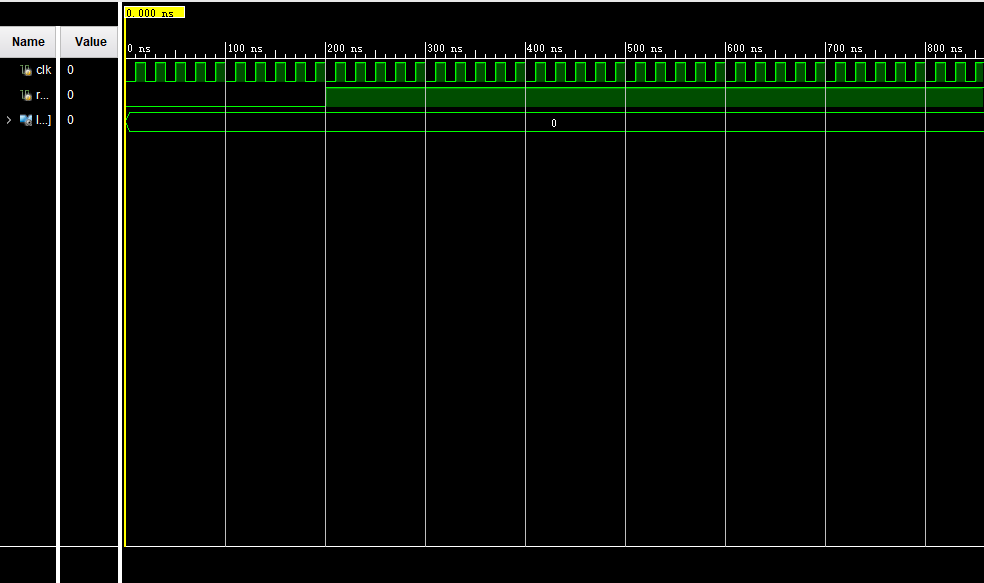

運行結(jié)束后即可查看仿真結(jié)果并且進行相應的調(diào)節(jié)觀察仿真波形圖

-

仿真

+關(guān)注

關(guān)注

51文章

4234瀏覽量

135293 -

文件

+關(guān)注

關(guān)注

1文章

578瀏覽量

25195 -

開發(fā)軟件

+關(guān)注

關(guān)注

1文章

25瀏覽量

13114 -

Vivado

+關(guān)注

關(guān)注

19文章

828瀏覽量

68205

發(fā)布評論請先 登錄

FPGA開發(fā)Vivado的仿真設計案例分析

基于microblaze的vivado開發(fā)流程

基于linux系統(tǒng)實現(xiàn)的vivado調(diào)用VCS仿真教程

Vivado設計之Tcl定制化的實現(xiàn)流程

Vivado綜合引擎的增量綜合流程

Vivado 開發(fā)教程(四) 行為仿真

Vivado設計流程指導手冊

Vivado設計流程指導說明

Vivado調(diào)用Questa Sim或ModelSim仿真小技巧

Xilinx FPGA Vivado開發(fā)流程介紹

vivado創(chuàng)建工程流程

Vivado調(diào)用Modelsim仿真

Vivado設計套件用戶指南(設計流程概述)

vivado主界面及設計流程

vivado仿真流程

vivado仿真流程

評論