最近買(mǎi)了很多的ADS1115.感覺(jué)是個(gè)好玩的芯片。主要吸引力在于該 ADC 具有差分輸入。這對(duì)于惠斯通電橋布置尤其有用。典型的組合是兩個(gè)元件變化電橋和廉價(jià)的電壓基準(zhǔn).與大多數(shù) ADC 不同的是, 通過(guò)增益設(shè)置的“每比特伏特”與為芯片供電的軌電壓無(wú)關(guān)。這意味著ADS1115 可以測(cè)量自己的電源使用不帶分頻器的內(nèi)部參考。

就像這樣

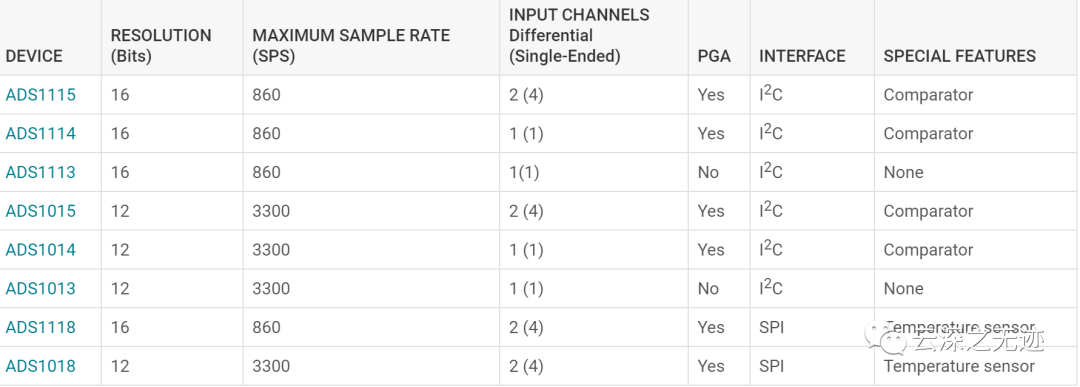

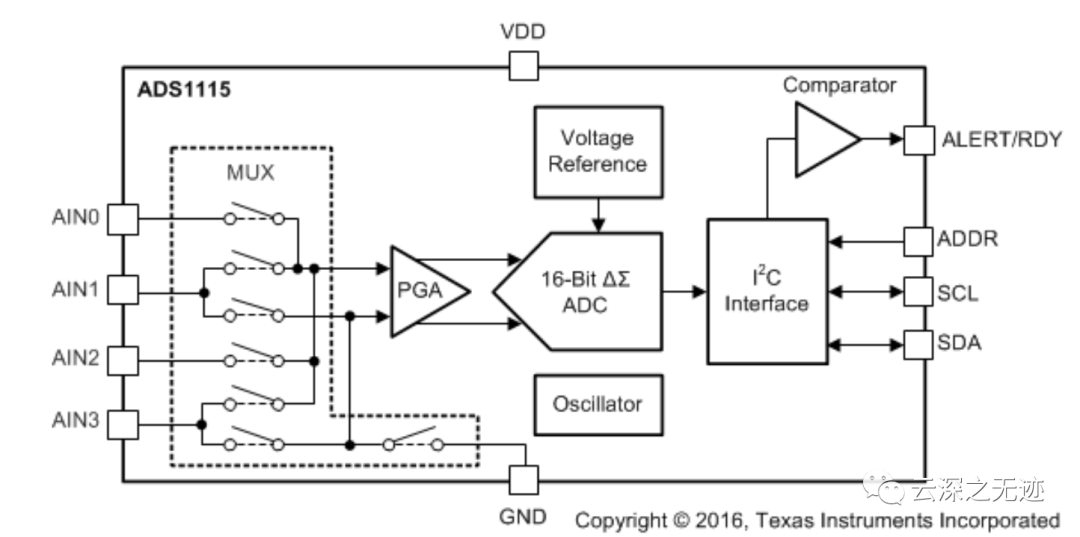

1115是頂級(jí)型號(hào)

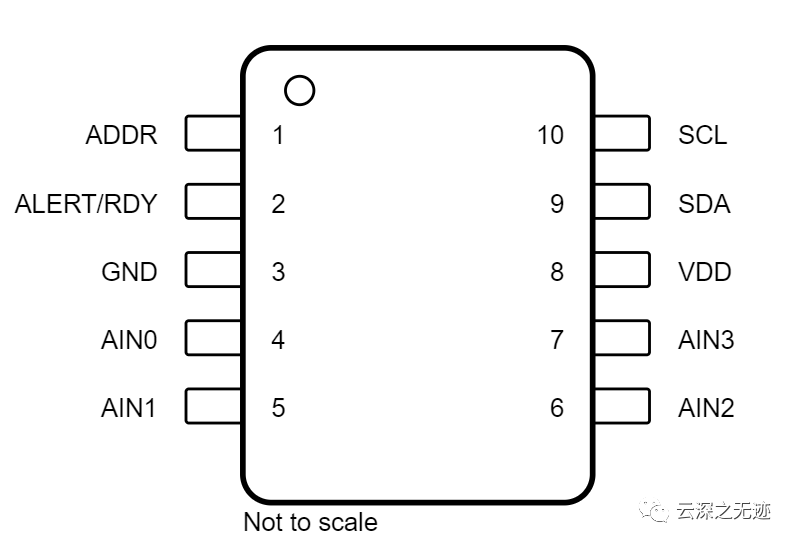

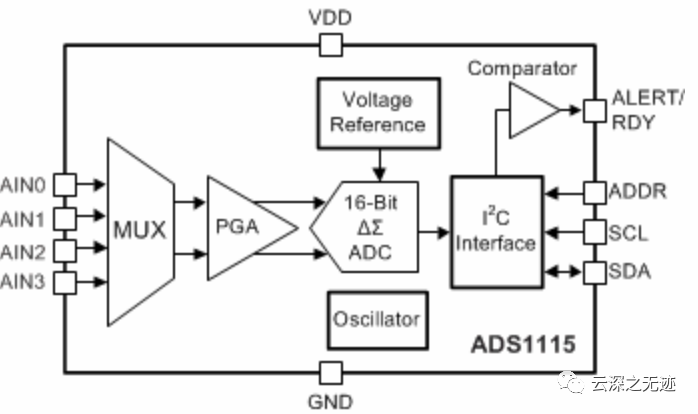

該芯片可配置為4個(gè)單端輸入通道,或兩個(gè)差分通道。包括一個(gè)高達(dá)x16的可編程增益放大器,以幫助將較小的單/差分信號(hào)提升到全范圍。

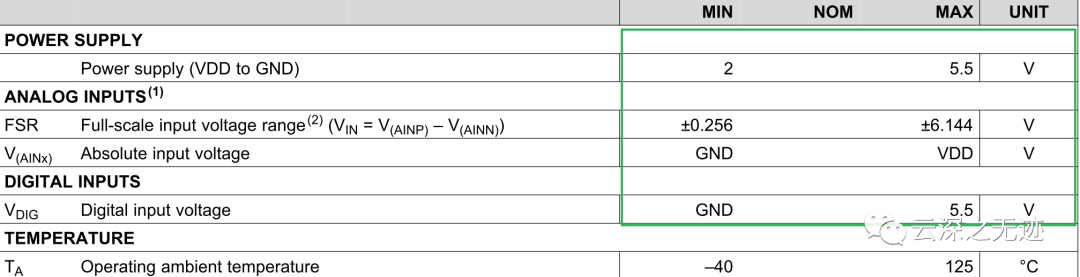

我喜歡這個(gè)ADC,因?yàn)樗梢詮?V到5V電源/邏輯運(yùn)行可以測(cè)量大范圍的信號(hào)。

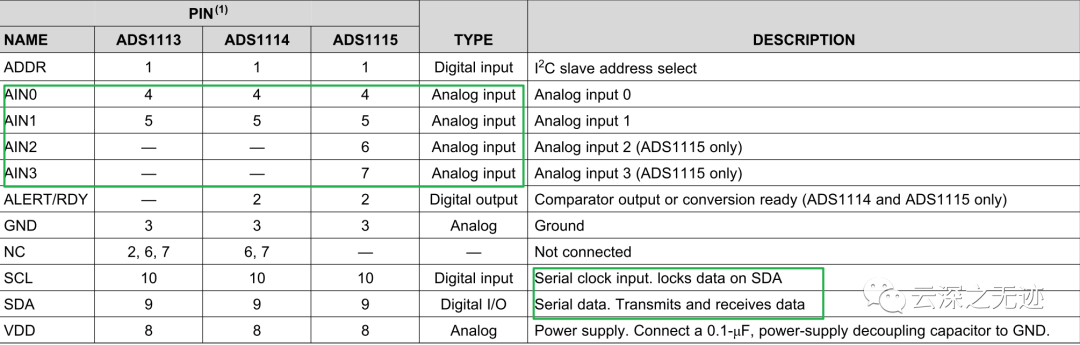

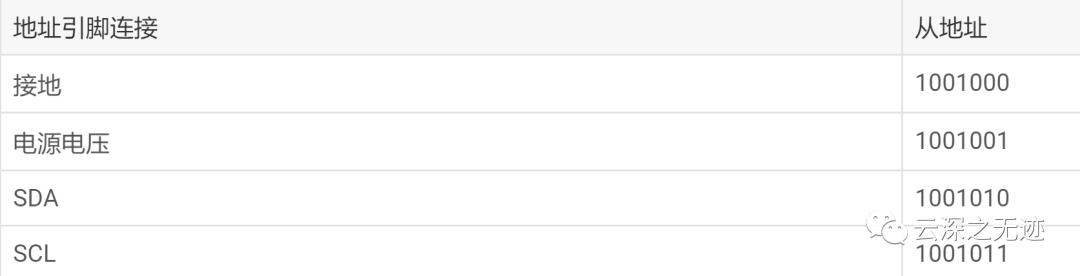

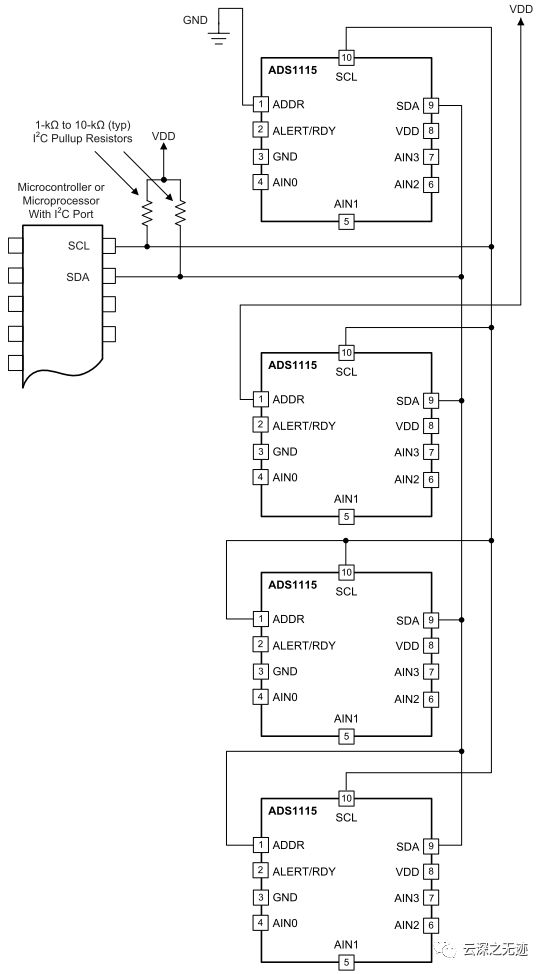

該芯片相當(dāng)小,因此它帶有一個(gè)帶有鐵氧體的分線板,以保持AVDD和AGND安靜。接口是通過(guò)12C完成的。地址可以更改為四個(gè)選項(xiàng)之一,因此您可以在單個(gè)2線12C總線上連接多達(dá)4個(gè)ADS1115.用于16個(gè)單端輸入。

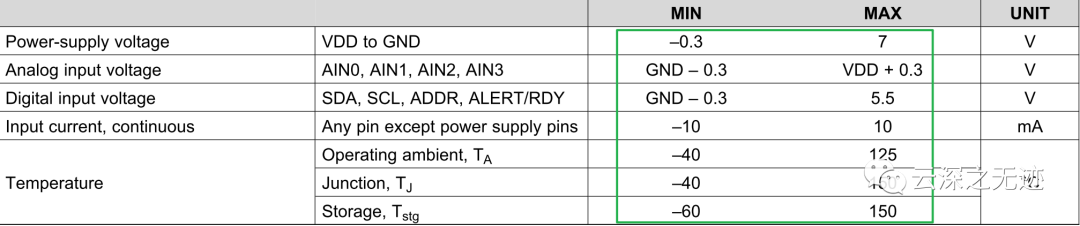

最大可以支持到7V

這個(gè)是推薦的參數(shù):對(duì)器件的模擬輸入施加的電壓不得超過(guò) VDD + 0.3 V,以及電源的輸入控制。

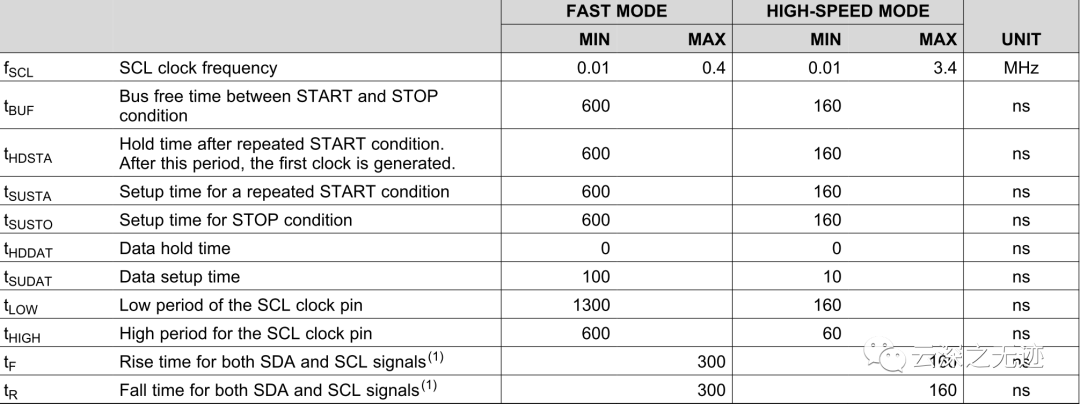

IIC的電氣控制,最大的速度是3.4MHz

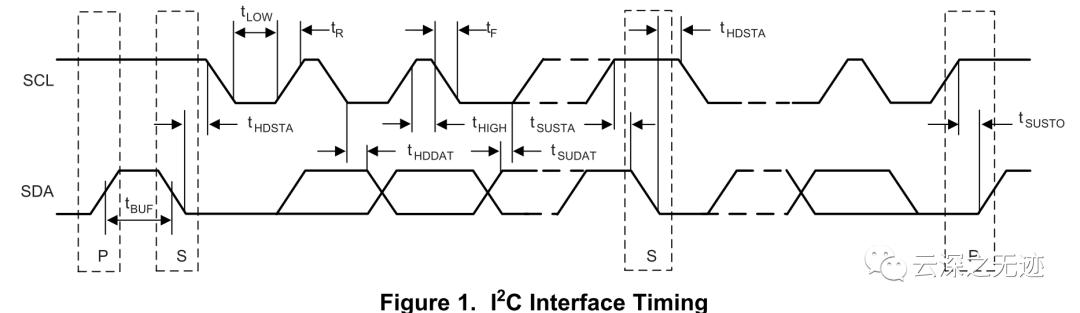

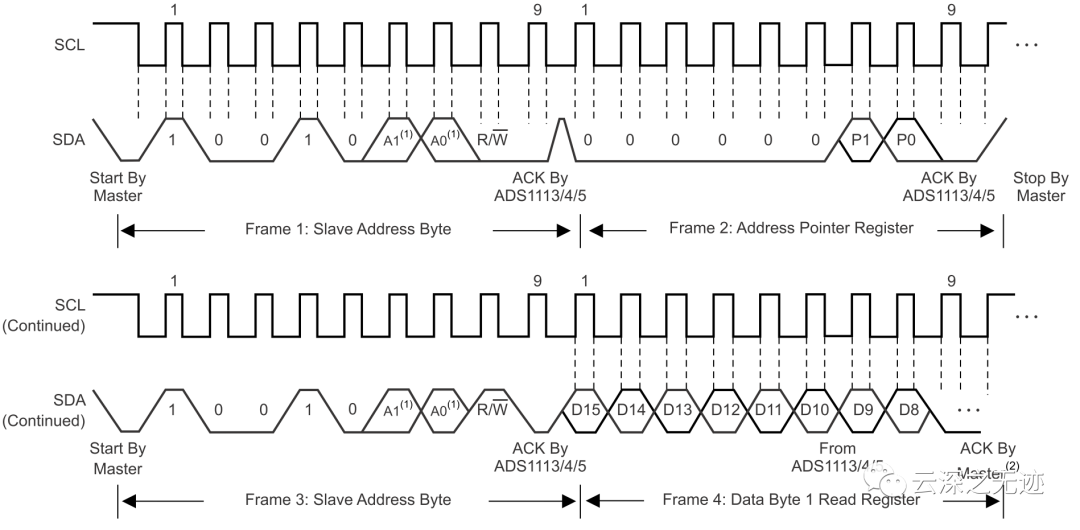

這個(gè)是時(shí)序

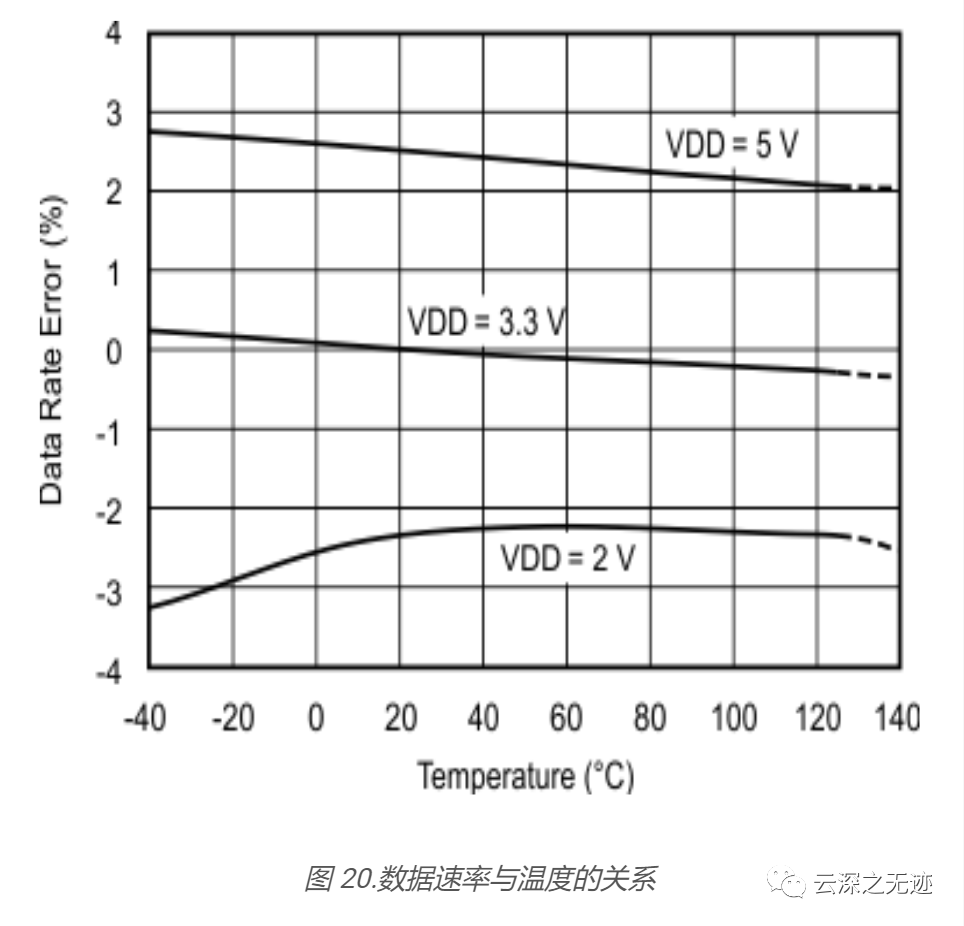

因?yàn)槲业膽?yīng)用條件有點(diǎn)熱,但是沒(méi)有熱到數(shù)據(jù)手冊(cè)里面的這個(gè)溫度,3.3V的錯(cuò)誤是最少的。

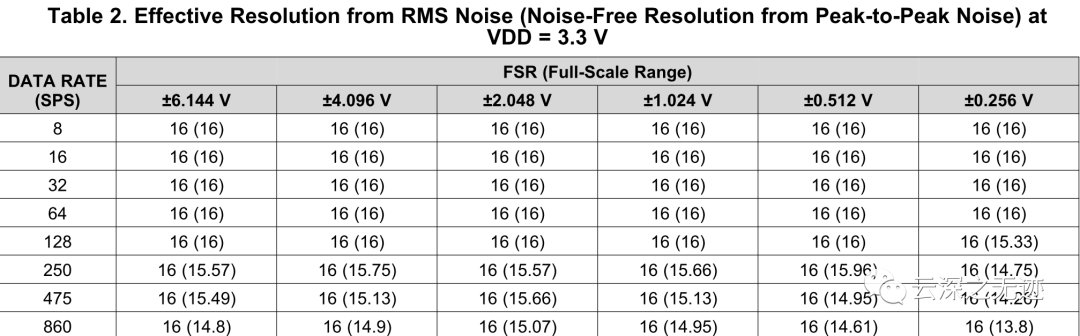

Delta-sigma (ΔΣ) 模數(shù)轉(zhuǎn)換器 (ADC) 基于過(guò)采樣原理。ΔΣ ADC 的輸入信號(hào)以高頻(調(diào)制器頻率)進(jìn)行采樣,隨后在數(shù)字域中進(jìn)行濾波和抽取,以在相應(yīng)的輸出數(shù)據(jù)速率下產(chǎn)生轉(zhuǎn)換結(jié)果。

調(diào)制器頻率與輸出數(shù)據(jù)速率之間的比率稱(chēng)為過(guò)采樣率(OSR)。通過(guò)增加 OSR,從而降低輸出數(shù)據(jù)速率,可以優(yōu)化 ADC 的噪聲性能。換句話說(shuō),當(dāng)降低輸出數(shù)據(jù)速率時(shí),輸入?yún)⒖荚肼晻?huì)下降,因?yàn)閮?nèi)部調(diào)制器的更多樣本被平均以產(chǎn)生一個(gè)轉(zhuǎn)換結(jié)果。增加增益還可以降低輸入?yún)⒖荚肼暎@在測(cè)量低電平信號(hào)時(shí)特別有用。

對(duì)于RMS噪聲,其對(duì)信號(hào)量化分辨率的影響可以概括為:

1. 噪聲會(huì)對(duì)量化過(guò)程產(chǎn)生誤差,降低轉(zhuǎn)換精度。

2. RMS噪聲水平與量化器的分辨率相關(guān)。

3. 當(dāng)RMS噪聲高于量化間隔的1/2時(shí),量化誤差明顯增加。

4. 為保證量化精度,有效分辨率需要高于RMS噪聲的2倍。

5. 例如,對(duì)于10比特量化器,量化間隔約為10mV。

6. 當(dāng)輸入RMS噪聲≥5mV時(shí),量化誤差劇增。

7. 為使噪聲引起的誤差小于1/2量化間隔,RMS噪聲需要<2.5mV。

8. 此時(shí),有效分辨率只有8比特左右。

9. 通過(guò)濾波及硬件設(shè)計(jì)減小噪聲,可提高有效分辨率。

10. 過(guò)采樣和噪聲整形也可以降低噪聲影響,提高分辨率。

一般都不說(shuō)這個(gè)參數(shù),因?yàn)樗麄儾桓?a target="_blank">高精度采集。

在以下情況下關(guān)注信號(hào)的 RMS 噪聲水平及其對(duì)量化分辨率的影響:

1. 設(shè)計(jì)數(shù)據(jù)采集系統(tǒng)時(shí),確定量化器比特?cái)?shù)。RMS 噪聲決定了真正有效的分辨率。

2. 低噪聲設(shè)計(jì)時(shí),RMS 噪聲是重要指標(biāo)。控制在量化間隔的1/2以下。

3. 評(píng)估現(xiàn)有系統(tǒng)量化誤差源時(shí),需要分析噪聲分布及 RMS 值。

4. 比較不同模數(shù)轉(zhuǎn)換器(ADC)時(shí),評(píng)估噪聲指標(biāo)。

5. 優(yōu)化信號(hào)回路時(shí),通過(guò)降低噪聲提高分辨率。

6. 計(jì)算信號(hào)動(dòng)態(tài)范圍時(shí),RMS 噪聲與峰值信號(hào)共同決定。

7. 模型預(yù)測(cè)控制系統(tǒng)中的狀態(tài)觀測(cè)器,噪聲會(huì)影響觀測(cè)精度。

8. 設(shè)計(jì)濾波器和數(shù)字信號(hào)處理算法時(shí),考慮抑制噪聲,提高精度。

9. 量化誤差分析優(yōu)化信號(hào)質(zhì)量時(shí),都需要考量噪聲的量化效應(yīng)。

RMS噪聲水平?jīng)Q定了量化過(guò)程的有效分辨率。控制噪聲在量化間隔的1/2以下,有效分辨率才可達(dá)到理論值。

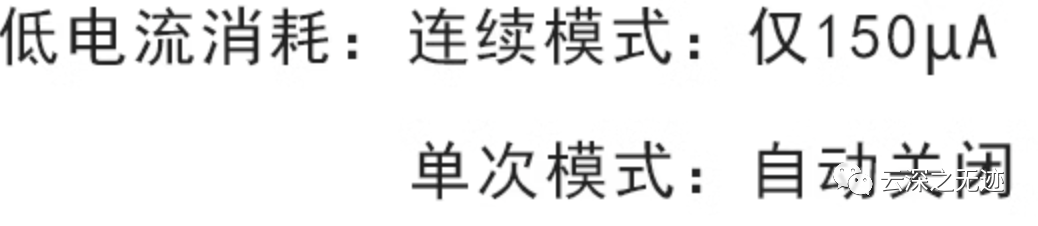

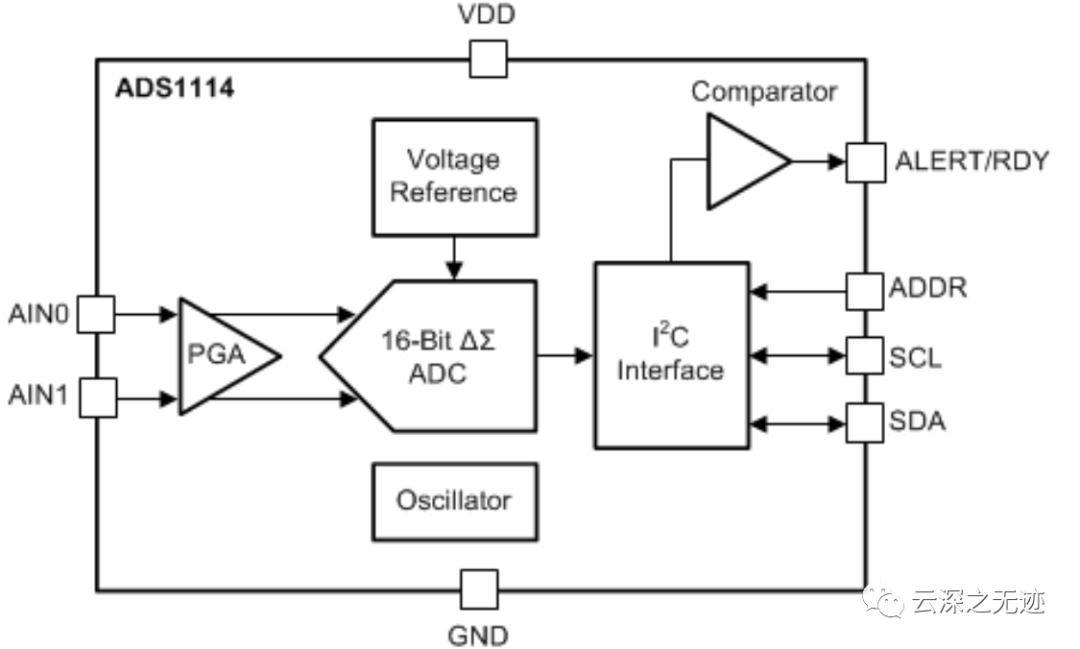

ADS111x 是非常小型、低功耗、16 位 Delta-Sigma (ΔΣ) 模數(shù)轉(zhuǎn)換器 (ADC)。ADS1114 和 ADS1115 還集成了可編程增益放大器 (PGA) 和可編程數(shù)字比較器。 ADS111x ADC 內(nèi)核測(cè)量差分信號(hào) V IN ,即 V (AINP)和 V (AINN)之差。該轉(zhuǎn)換器核心由一個(gè)差分開(kāi)關(guān)電容器 ΔΣ 調(diào)制器和一個(gè)數(shù)字濾波器組成。這種架構(gòu)會(huì)導(dǎo)致任何共模信號(hào)的強(qiáng)烈衰減。輸入信號(hào)與內(nèi)部參考電壓進(jìn)行比較。數(shù)字濾波器接收來(lái)自調(diào)制器的高速比特流并輸出與輸入電壓成比例的代碼。 ADS111x 有兩種可用的轉(zhuǎn)換模式:?jiǎn)未无D(zhuǎn)換和連續(xù)轉(zhuǎn)換。 在單次模式下,ADC 根據(jù)請(qǐng)求對(duì)輸入信號(hào)執(zhí)行一次轉(zhuǎn)換,將轉(zhuǎn)換值存儲(chǔ)到內(nèi)部轉(zhuǎn)換寄存器,然后進(jìn)入斷電狀態(tài)。此模式旨在為僅需要定期轉(zhuǎn)換或轉(zhuǎn)換之間有較長(zhǎng)空閑期的系統(tǒng)提供顯著的節(jié)能效果。 在連續(xù)轉(zhuǎn)換模式下,ADC 在上一次轉(zhuǎn)換完成后立即自動(dòng)開(kāi)始輸入信號(hào)的轉(zhuǎn)換。連續(xù)轉(zhuǎn)換速率等于編程的數(shù)據(jù)速率。數(shù)據(jù)可以隨時(shí)讀取,并且始終反映最近完成的轉(zhuǎn)換。

當(dāng)降低輸出數(shù)據(jù)速率時(shí),ΔΣ ADC 的噪聲性能通常會(huì)提高,因?yàn)閮?nèi)部調(diào)制器的更多樣本會(huì)被平均以產(chǎn)生一個(gè)轉(zhuǎn)換結(jié)果。在功耗至關(guān)重要的應(yīng)用中,可能不需要在低數(shù)據(jù)速率下改進(jìn)噪聲性能。

對(duì)于這些應(yīng)用,ADS111x 支持占空比,通過(guò)以有效較低的數(shù)據(jù)速率定期請(qǐng)求高數(shù)據(jù)速率讀數(shù),從而顯著節(jié)省功耗。

例如,處于斷電狀態(tài)且數(shù)據(jù)速率設(shè)置為 860 SPS 的 ADS111x 可由微控制器操作,該微控制器指示每 125 ms (8 SPS) 進(jìn)行一次單次轉(zhuǎn)換。860 SPS 的轉(zhuǎn)換僅需要大約 1.2 ms,因此 ADS111x 在剩余的 123.8 ms 內(nèi)進(jìn)入斷電狀態(tài)。

在此配置中,ADS111x 消耗的功率約為連續(xù)轉(zhuǎn)換模式下消耗功率的 1/100。占空比完全是任意的,由主控制器定義。ADS111x 提供較低的數(shù)據(jù)速率,不實(shí)現(xiàn)占空比,并且如果需要的話還可以提供改進(jìn)的噪聲性能。

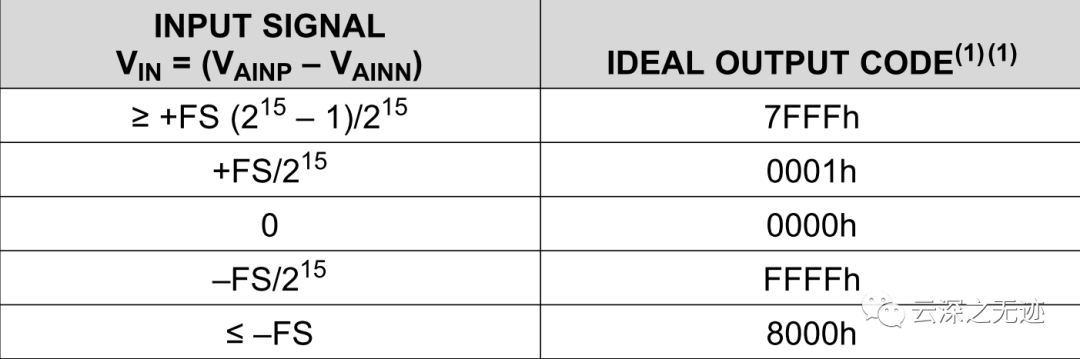

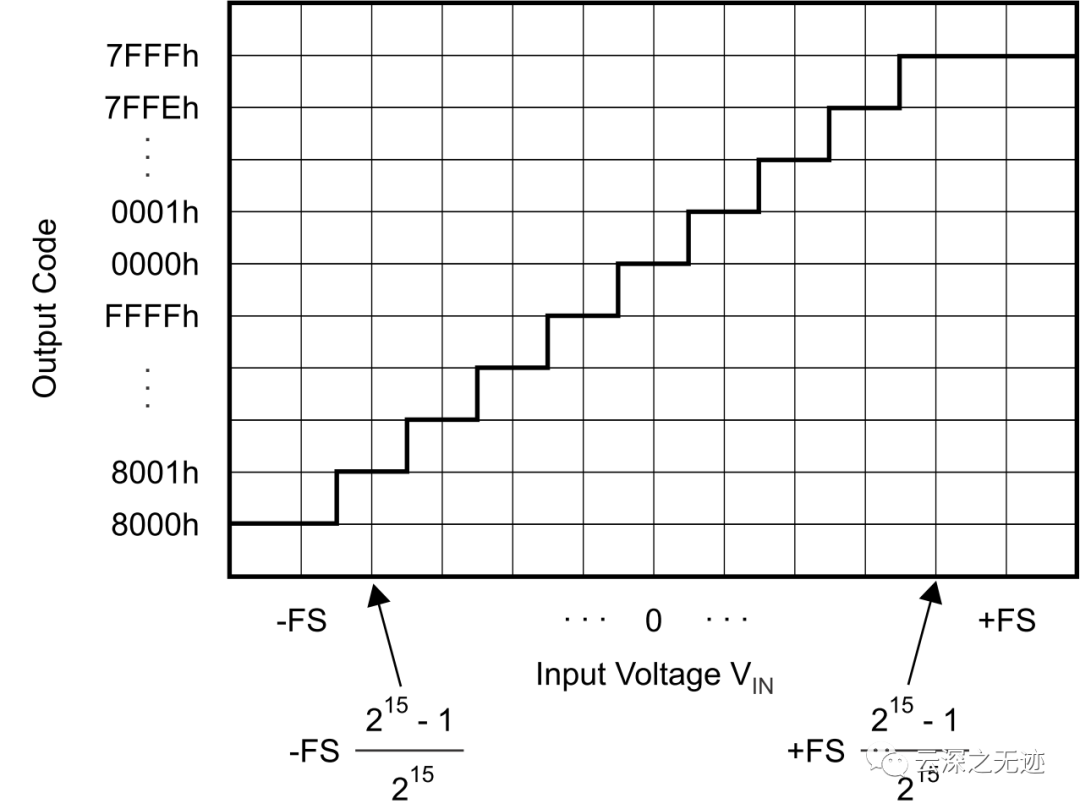

其實(shí)這個(gè)東西就是個(gè)15bit的ADC,有一位是符號(hào)位

這個(gè)前面有更好的連接圖

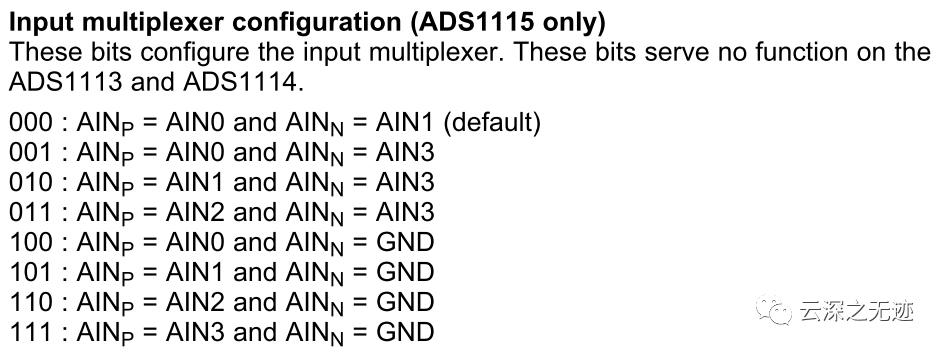

這個(gè)東西叫多路復(fù)用器

多路復(fù)用器由配置寄存器中的 MUX[2:0] 位進(jìn)行配置。測(cè)量單端信號(hào)時(shí),ADC 的負(fù)輸入通過(guò)多路復(fù)用器內(nèi)的開(kāi)關(guān)在內(nèi)部連接至 GND。

如果就一路差分,可以使用這個(gè)1114

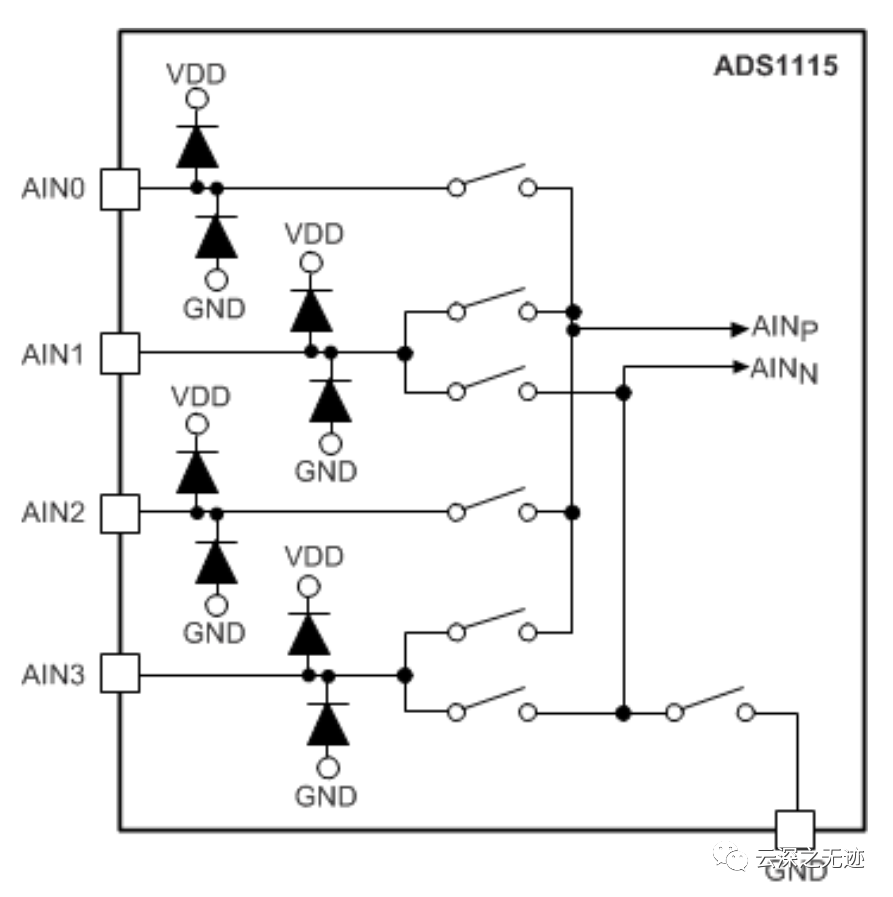

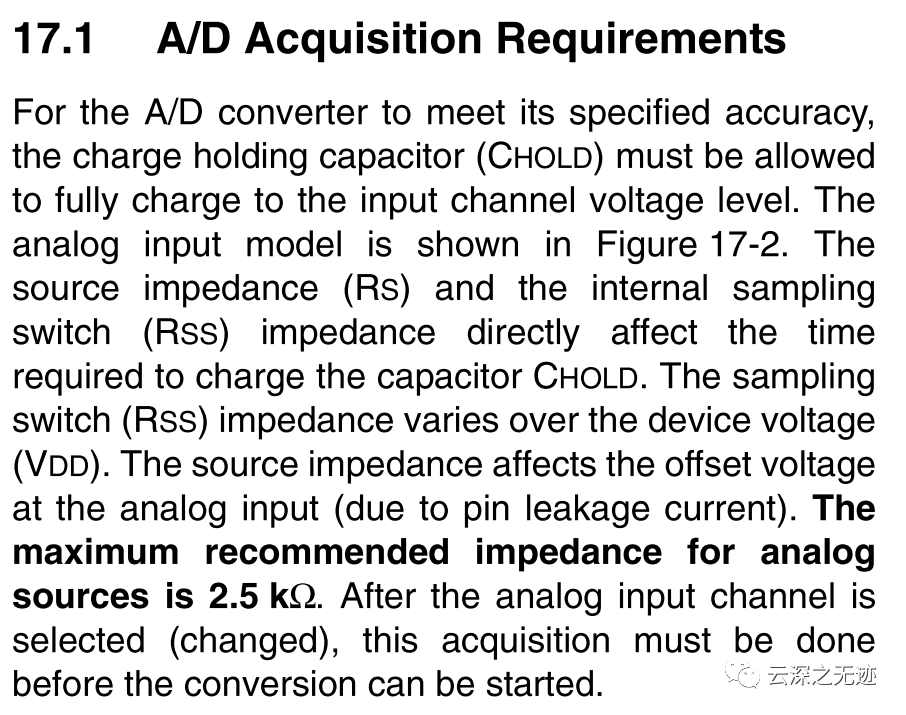

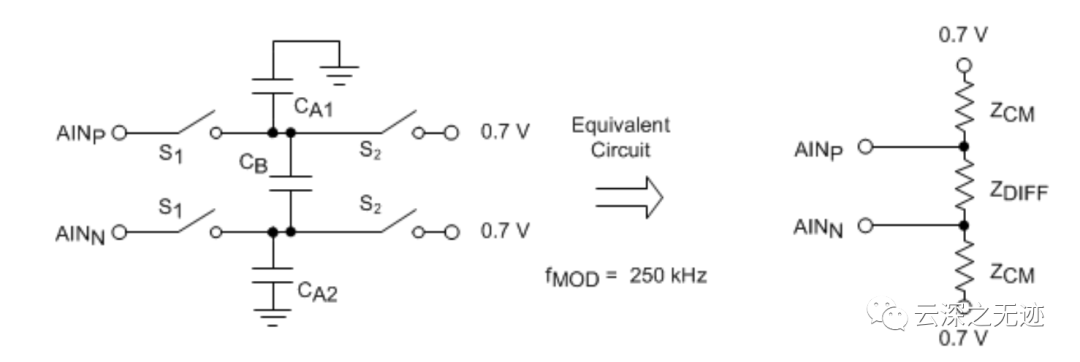

連接到 VDD 和 GND 的靜電放電 (ESD) 二極管可保護(hù) ADS111x 模擬輸入。將任何輸入的絕對(duì)電壓保持在公式所示的范圍內(nèi),以防止 ESD 二極管導(dǎo)通。公式 :GND – 0.3V < V (AINX) < VDD + 0.3V如果輸入引腳上的電壓可能違反這些條件,使用外部肖特基二極管和串聯(lián)電阻將輸入電流限制在安全值。 ADS111x 使用開(kāi)關(guān)電容器輸入級(jí),其中電容器連續(xù)充電然后放電,以測(cè)量 AIN P和 AIN N之間的電壓。對(duì)輸入信號(hào)進(jìn)行采樣的頻率稱(chēng)為采樣頻率或調(diào)制器頻率(f MOD)。 這個(gè)地方看microChip的數(shù)據(jù)手冊(cè):

PIC18也是這個(gè)ADC的方案

ADS111x 具有一個(gè) 1 MHz 內(nèi)部振蕩器,該振蕩器進(jìn)一步除以 4 倍以生成250 kHz 的f MOD 。該輸入級(jí)中使用的電容器很小,對(duì)于外部電路來(lái)說(shuō),平均負(fù)載表現(xiàn)為電阻性。

顯示了該結(jié)構(gòu)。電容器值決定電阻和開(kāi)關(guān)速率

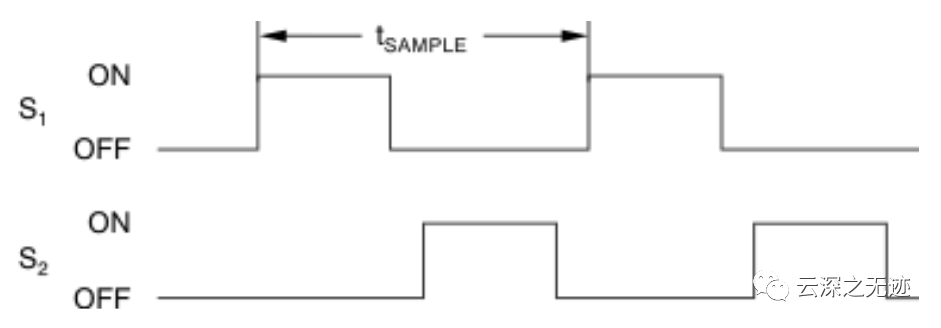

開(kāi)關(guān)時(shí)序 在采樣階段,開(kāi)關(guān)S 1閉合。該事件將CA1充電至 V (AINP)、將CA2充電至 V (AINN)、將 C B充電至 (V (AINP) – V (AINN) )。在放電階段,S 1首先打開(kāi),然后S 2關(guān)閉。 然后,CA1和CA2均放電至大約 0.7V,CB放電至 0V。此充電從驅(qū)動(dòng) ADS111x 模擬輸入的源汲取非常小的瞬態(tài)電流。該電流的平均值可用于計(jì)算有效阻抗(Z eff)。

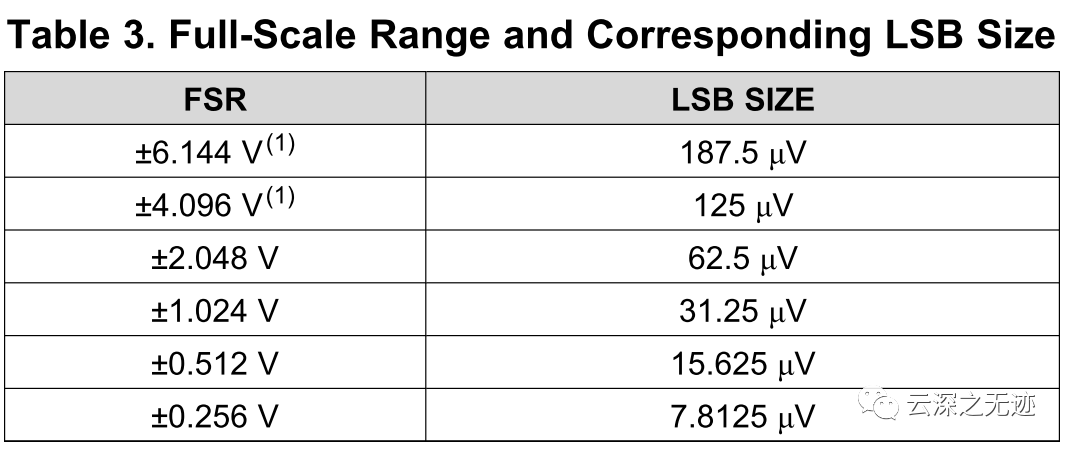

這個(gè)就是量化精度了 ADS111x 提供可編程輸出數(shù)據(jù)速率。 使用配置寄存器中的 DR[2:0] 位選擇 8 SPS、16 SPS、32 SPS、64 SPS、128 SPS、250 SPS、475 SPS 或 860 SPS 的輸出數(shù)據(jù)速率。

1. 根據(jù)奈奎斯特采樣定理,采樣率必須大于信號(hào)中最高頻率分量的兩倍,才能正確表示原始信號(hào)。SPS 決定了可以表示的最大信號(hào)頻率。

2. 采樣率越高,可以表示更寬頻段的信號(hào),重構(gòu)精度也越高。但數(shù)據(jù)量也會(huì)增加。

3. 采樣率要匹配后端信號(hào)處理算法要求。例如調(diào)制識(shí)別需要足夠高的采樣率。

4. 較高的過(guò)采樣可以提高量化精度,降低噪聲影響。

5. SPS 需要設(shè)置為對(duì)系統(tǒng)易于實(shí)現(xiàn)的數(shù)值,如 8kHz、44.1kHz等。

6. SPS 與ADC轉(zhuǎn)換速率有關(guān),高SPS需要高速ADC。7. SPS 也決定了數(shù)字信號(hào)處理算法的計(jì)算負(fù)載。

ADS111x 中的轉(zhuǎn)換在一個(gè)周期內(nèi)完成;因此,轉(zhuǎn)換時(shí)間等于 1 / DR。

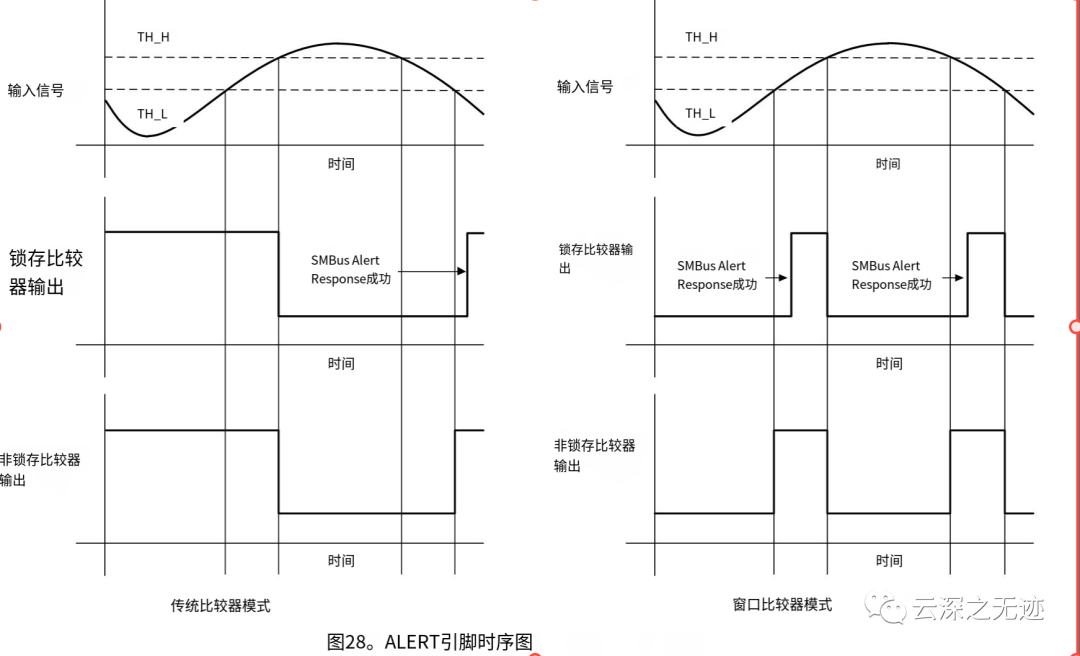

有個(gè)數(shù)字比較的功能

ADS1115 和 ADS1114 具有可編程數(shù)字比較器,可以在 ALERT/RDY 引腳上發(fā)出警報(bào)。我想不到什么場(chǎng)合可以用。

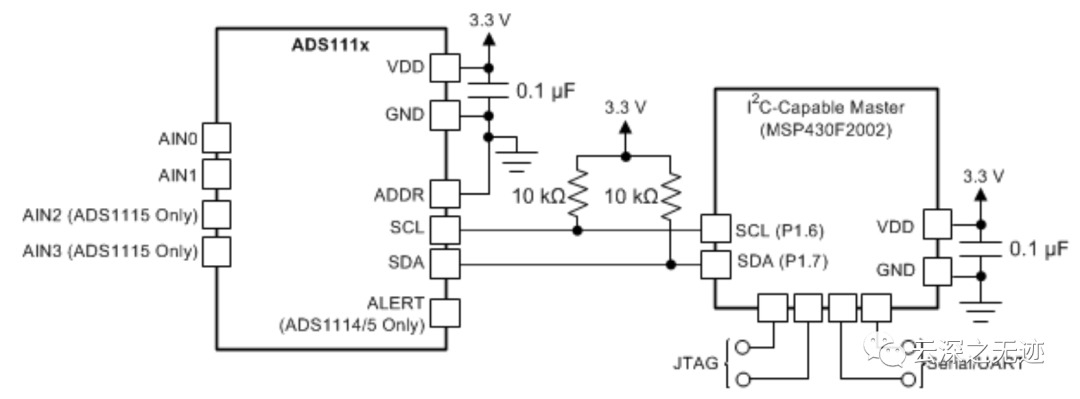

ADS111x 通過(guò) I2C 接口進(jìn)行通信。I2C 是一個(gè)兩線開(kāi)漏極接口,支持單個(gè)總線上的多個(gè)設(shè)備和主設(shè)備。

I2C 總線上的設(shè)備僅通過(guò)將總線接地來(lái)將總線驅(qū)動(dòng)為低電平;這些設(shè)備永遠(yuǎn)不會(huì)將總線驅(qū)動(dòng)為高電平。相反,總線線由上拉電阻拉高,因此當(dāng)沒(méi)有設(shè)備將總線線驅(qū)動(dòng)為低電平時(shí),總線線始終為高電平。由于此配置,兩個(gè)設(shè)備不會(huì)發(fā)生沖突。如果兩個(gè)設(shè)備同時(shí)驅(qū)動(dòng)總線,則不存在驅(qū)動(dòng)程序爭(zhēng)用。

ADS111x 有一個(gè)地址引腳 ADDR,用于配置器件的I2C地址。該引腳可連接至 GND、VDD、SDA 或 SCL,從而允許用一個(gè)引腳選擇四個(gè)不同的地址,如表 4所示。地址引腳 ADDR 的狀態(tài)被連續(xù)采樣。

首先使用 GND、VDD 和 SCL 地址。如果使用 SDA 作為器件地址,請(qǐng)?jiān)?SCL 線變低后將 SDA 線保持為低電平至少 100 ns,以確保器件在 I 2 C 通信期間正確解碼地址。

一次可以上4個(gè)1115

地址是這個(gè)

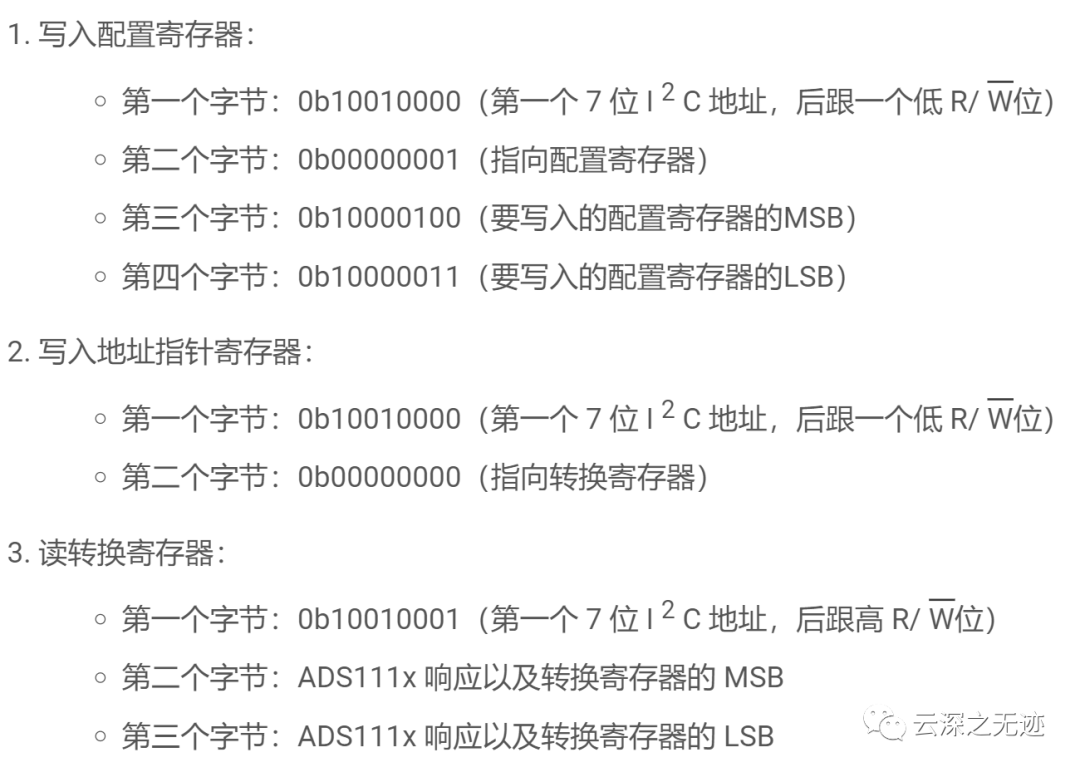

在從機(jī)接收模式下,從主機(jī)傳輸?shù)綇臋C(jī)的第一個(gè)字節(jié)包含 7 位設(shè)備地址,后跟一個(gè)低 R/ W位。主機(jī)發(fā)送的下一個(gè)字節(jié)是地址指針寄存器。然后,ADS111x 確認(rèn)收到地址指針寄存器字節(jié)。接下來(lái)的兩個(gè)字節(jié)被寫(xiě)入寄存器地址指針位 P[1:0] 指定的地址。ADS111x 確認(rèn)發(fā)送的每個(gè)字節(jié)。發(fā)送寄存器字節(jié)時(shí),首先發(fā)送最高有效字節(jié),然后發(fā)送最低有效字節(jié)。

讓我們來(lái)看看讀寄存器

明天上邏輯分析儀!

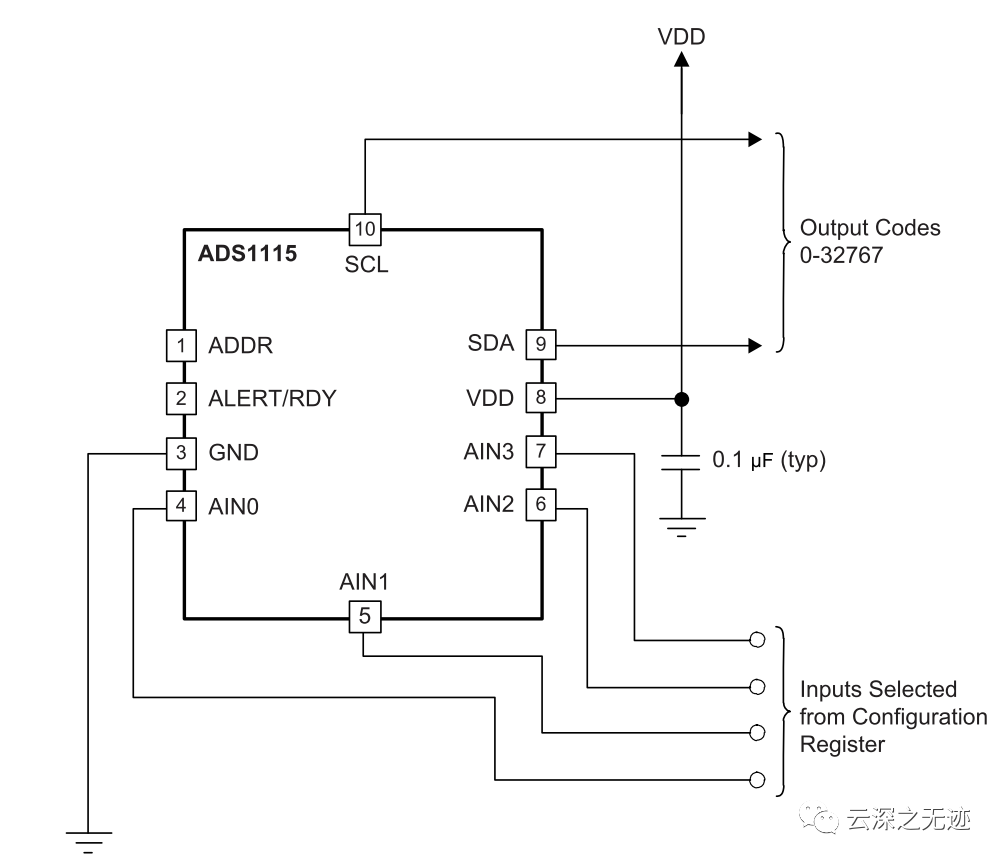

ADS111x 以二進(jìn)制補(bǔ)碼格式提供 16 位數(shù)據(jù)。正滿量程 (+FS) 輸入產(chǎn)生 7FFFh 的輸出代碼,負(fù)滿量程 (–FS) 輸入產(chǎn)生 8000h 的輸出代碼。對(duì)于超過(guò)滿量程的信號(hào),輸出會(huì)在這些代碼處進(jìn)行削波。

總結(jié)了不同輸入信號(hào)的理想輸出代碼

顯示了代碼轉(zhuǎn)換與輸入電壓的關(guān)系。

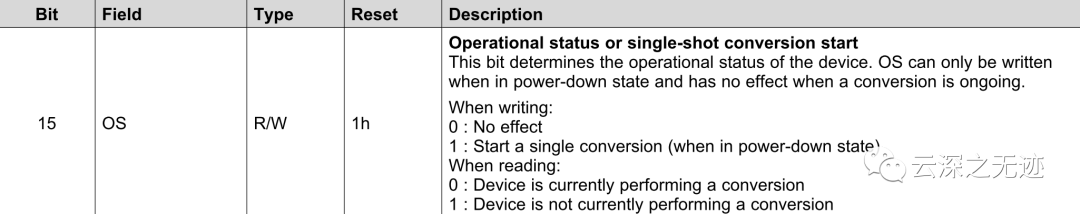

寄存器什么的,沒(méi)什么意思,編程的時(shí)候才能看見(jiàn)。

看一個(gè)就行

有IIC的MCU就行

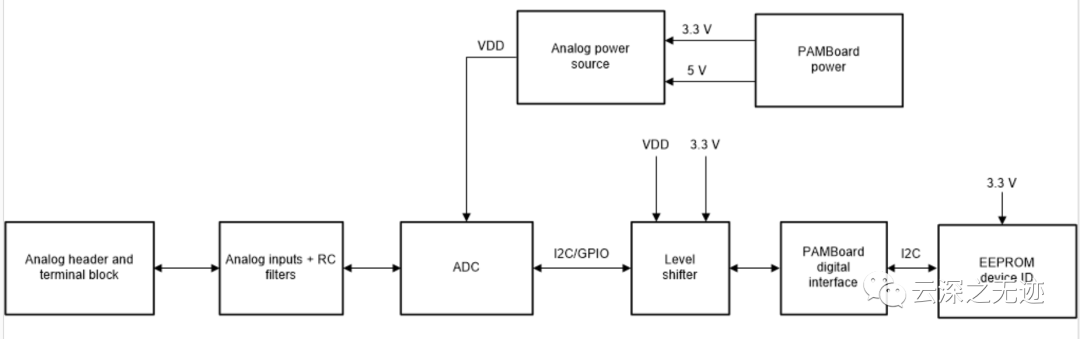

更加詳細(xì)的應(yīng)該是這樣

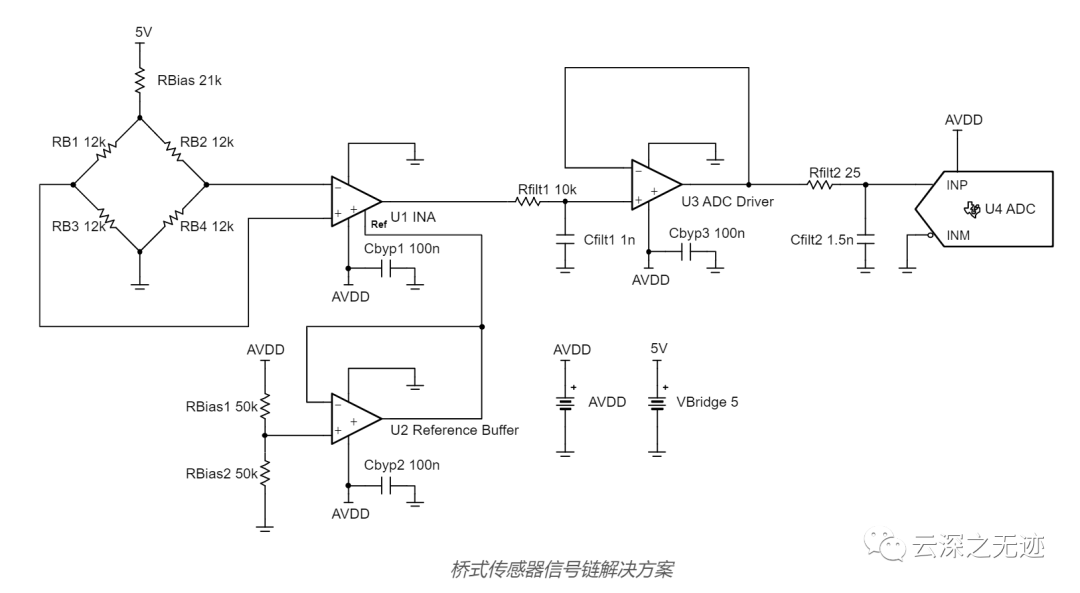

ADS111x 的全差分電壓輸入非常適合連接具有較低源阻抗的差分源,例如熱電偶和熱敏電阻。盡管 ADS111x 可以讀取雙極性差分信號(hào),但這些器件不能接受任一輸入上的負(fù)電壓。

上面的橋只是說(shuō)接差分信號(hào)而已,事實(shí)上還得進(jìn)行信號(hào)的調(diào)理

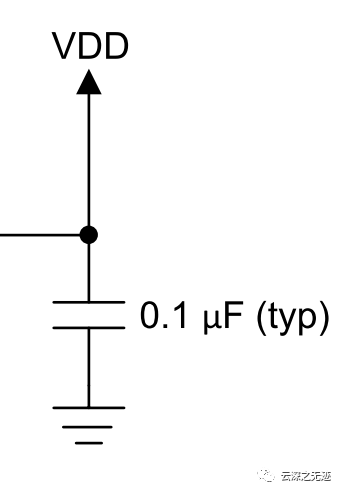

ADS111x 在轉(zhuǎn)換期間消耗瞬態(tài)電流。0.1μF 電源旁路電容器可提供電源所需的瞬時(shí)額外電流。

續(xù)流

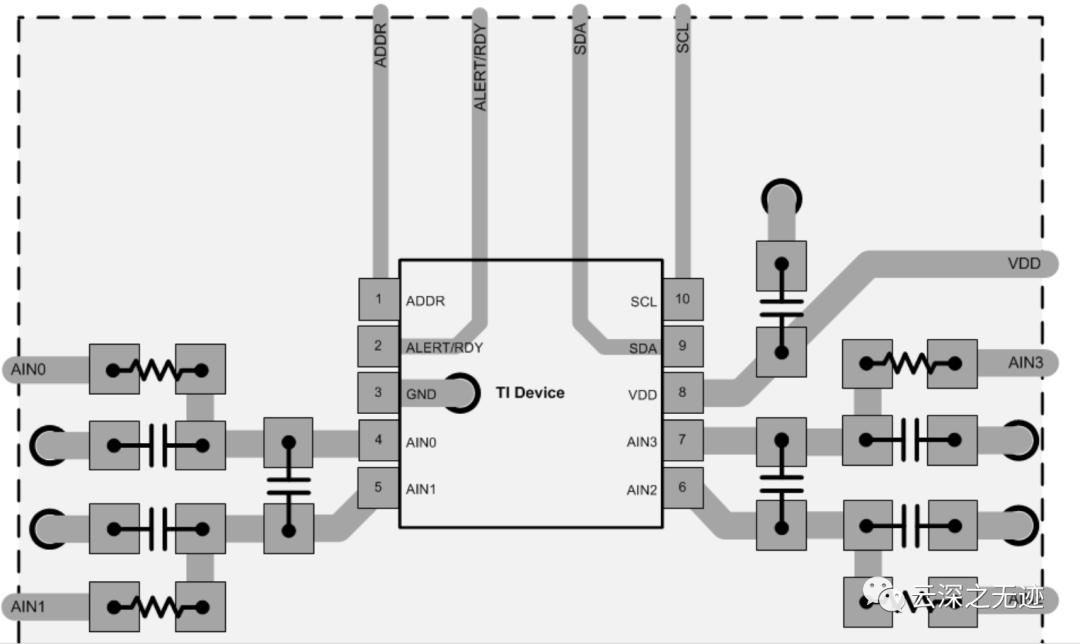

良好的電源去耦對(duì)于實(shí)現(xiàn)最佳性能非常重要。必須使用至少 0.1 μF 電容器對(duì) VDD 進(jìn)行去耦。當(dāng)器件進(jìn)行轉(zhuǎn)換時(shí),0.1μF 旁路電容器可提供電源所需的瞬時(shí)額外電流。 使用低阻抗連接將旁路電容器盡可能靠近器件的電源引腳放置。使用具有低等效串聯(lián)電阻 (ESR) 和電感 (ESL) 特性的多層陶瓷片式電容器 (MLCC),以實(shí)現(xiàn)電源去耦目的。對(duì)于非常敏感的系統(tǒng)或處于惡劣噪聲環(huán)境中的系統(tǒng),避免使用過(guò)孔將電容器連接到器件引腳,以獲得更好的抗噪聲能力。并行使用多個(gè)過(guò)孔可降低整體電感,并且有利于與接地層的連接。 VDD 穩(wěn)定后,請(qǐng)等待大約 50 μs,然后再與器件通信,以完成上電復(fù)位過(guò)程。

布局

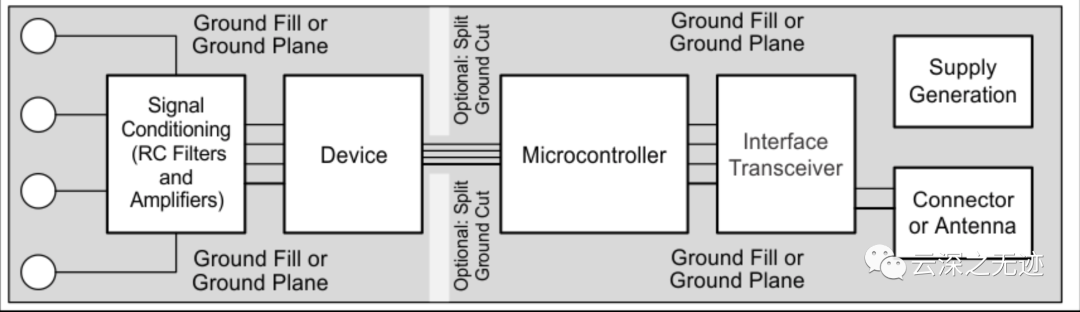

在為模擬和數(shù)字組件布局印刷電路板 (PCB) 時(shí),采用最佳設(shè)計(jì)實(shí)踐。為了獲得最佳性能,請(qǐng)將模擬組件 [例如 ADC、放大器、基準(zhǔn)電壓源、數(shù)模轉(zhuǎn)換器 (DAC) 和模擬 MUX] 與數(shù)字組件 [例如微控制器、復(fù)雜可編程邏輯器件 (CPLD)、現(xiàn)場(chǎng)可編程器件門(mén)陣列 (FPGA)、射頻 (RF) 收發(fā)器、通用串行總線 (USB) 收發(fā)器和開(kāi)關(guān)穩(wěn)壓器]。 上圖顯示了良好元件布局的示例。雖然提供了元件布局的一個(gè)很好的例子,每個(gè)應(yīng)用的最佳布局對(duì)于所采用的幾何形狀、元件和 PCB 制造能力來(lái)說(shuō)都是獨(dú)一無(wú)二的。也就是說(shuō),不存在適合每種設(shè)計(jì)的單一布局,在使用任何模擬組件進(jìn)行設(shè)計(jì)時(shí)必須始終仔細(xì)考慮。 分離模擬和數(shù)字信號(hào)。首先,在布局允許的情況下,將電路板分為模擬部分和數(shù)字部分。將數(shù)字線路遠(yuǎn)離模擬線路。這可以防止數(shù)字噪聲耦合回模擬信號(hào)。 用接地填充物填充信號(hào)層上的空白區(qū)域。 提供良好的接地返回路徑。信號(hào)返回電流在阻抗最小的路徑上流動(dòng)。如果接地層被切割或有其他走線阻止電流在信號(hào)走線旁邊流動(dòng),則必須找到另一條路徑返回源并完成電路。如果它被迫進(jìn)入更大的路徑,就會(huì)增加信號(hào)輻射的機(jī)會(huì)。敏感信號(hào)更容易受到 EMI 干擾。 在電源上使用旁路電容器來(lái)降低高頻噪聲。不要在旁路電容器和有源器件之間放置過(guò)孔。將旁路電容器放置在盡可能靠近有源器件的同一層上可產(chǎn)生最佳結(jié)果。 考慮布線的電阻和電感。通常,輸入走線具有與輸入偏置電流發(fā)生反應(yīng)并導(dǎo)致附加誤差電壓的電阻。減小源信號(hào)和返回電流所包圍的環(huán)路面積,以減小路徑中的電感。減小電感以減小 EMI 拾取,并減小器件所見(jiàn)的高頻阻抗。 差分輸入必須與進(jìn)入測(cè)量源的兩個(gè)輸入相匹配。 具有差分連接的模擬輸入必須在輸入之間差分放置一個(gè)電容器。差分測(cè)量的最佳輸入組合使用相鄰的模擬輸入線,例如 AIN0、AIN1 和 AIN2、AIN3。差分電容必須是高質(zhì)量的。最好的陶瓷片式電容器是C0G(NPO),它具有穩(wěn)定的性能和低噪聲的特性。

VOOSP一個(gè)的布局,就按照這個(gè)做

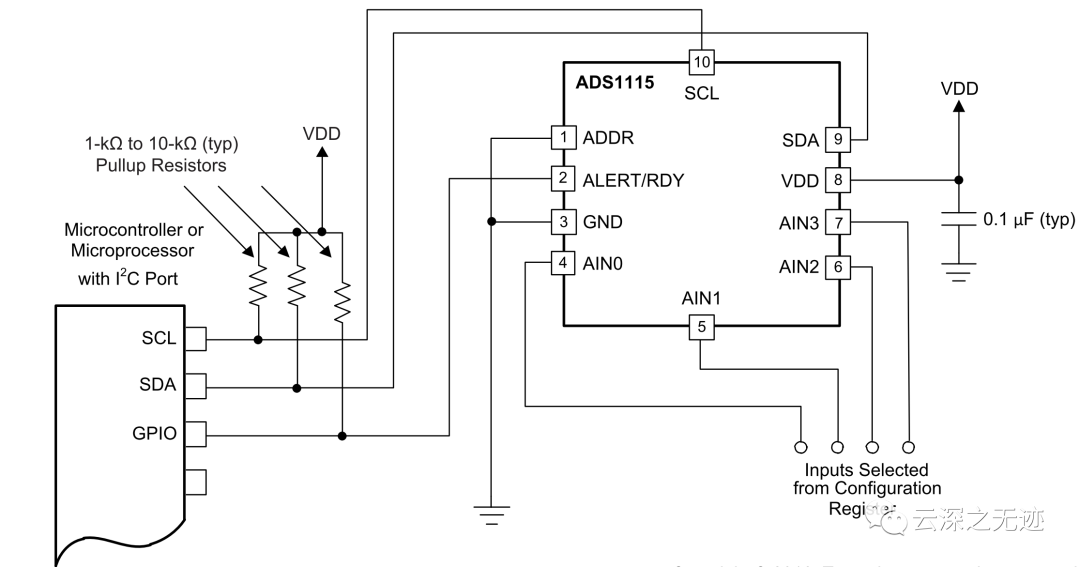

ADS111x 直接連接到標(biāo)準(zhǔn)模式、快速模式和高速模式 I 2 C 控制器。任何微控制器 I2C 外設(shè)(包括僅主控和單主控I2C外設(shè))均可與 ADS111x 一起運(yùn)行。 SDA 和 SCL 線上都需要上拉電阻,因?yàn)镮2C總線驅(qū)動(dòng)器是漏極開(kāi)路的。這些電阻器的大小取決于總線運(yùn)行速度和總線線路的電容。 電阻值越高,功耗越低,但會(huì)增加總線上的轉(zhuǎn)換時(shí)間,從而限制總線速度。 較低阻值的電阻可實(shí)現(xiàn)更高的速度,但代價(jià)是功耗更高。 長(zhǎng)總線具有更高的電容,并且需要更小的上拉電阻來(lái)補(bǔ)償。不要使用太小的電阻,因?yàn)榭偩€驅(qū)動(dòng)器可能無(wú)法將總線拉低。

來(lái)看看單端輸入:

ADS1113 和 ADS1114 可測(cè)量 1 個(gè)單端信號(hào),ADS1115 最多可測(cè)量 4 個(gè)單端信號(hào)。ADS1113和ADS1114可以通過(guò)將AIN1外部連接到GND來(lái)測(cè)量單端信號(hào)。ADS1115 通過(guò)適當(dāng)配置配置寄存器中的 MUX[2:0] 位來(lái)測(cè)量單端信號(hào)。這些就是幾個(gè)型號(hào)之間的不同用處了。

顯示了 ADS1115 的單端連接方案 單端信號(hào)范圍從 0 V 到正電源或 +FS,以較低者為準(zhǔn)。負(fù)電壓不能施加到這些器件,因?yàn)?ADS111x 只能接受相對(duì)于地的正電壓。ADS111x 在輸入范圍內(nèi)不會(huì)失去線性度。 ADS111x 提供 ±FSR 的差分輸入電壓范圍。單端配置僅使用滿量程輸入電壓范圍的一半。差分配置最大限度地提高了 ADC 的動(dòng)態(tài)范圍,并提供比單端配置更好的共模噪聲抑制。

指的是電路對(duì)共模噪聲的抑制能力。共模噪聲是同時(shí)影響電路兩個(gè)輸入端的噪聲信號(hào)。

共模噪聲衰減的計(jì)算公式為:CMRR = 20log(共模噪聲干擾電壓/因此造成的輸出誤差電壓)輸出端誤差電壓越小,表示電路抑制共模噪聲的能力越強(qiáng),CMRR值越大。

共模噪聲衰減主要由以下幾方面決定:

1. 差分放大器的共模抑制率(CMR)

2. 輸入濾波器抑制共模噪聲的性能

3. 電源供應(yīng)的干擾

4. PCB布局的抗干擾設(shè)計(jì)

5. 模擬地與數(shù)字地連接的隔離

6. 放大器參數(shù)漂移的影響通常要求儀表放大器和測(cè)量設(shè)備有很高的CMRR,比如大于80dB,來(lái)獲取精確的信號(hào)。

就是這里

通過(guò)適當(dāng)設(shè)置 MUX[2:0] 位,ADS1115 還允許 AIN3 作為測(cè)量的公共點(diǎn)。AIN0、AIN1 和 AIN2 都可以相對(duì)于 AIN3 進(jìn)行測(cè)量。在此配置中,ADS1115 通過(guò)輸入運(yùn)行,其中 AIN3 作為公共點(diǎn)。

此功能提高了單端配置的可用范圍,因?yàn)楫?dāng)GND < V (AIN3) < VDD 時(shí)允許負(fù)差分電壓。

ADS111x 采用小尺寸、低電壓工藝制造。模擬輸入具有連接至電源軌的保護(hù)二極管。然而,這些二極管的電流處理能力有限,并且長(zhǎng)時(shí)間超出電源軌約 300 mV 的模擬輸入電壓可能會(huì)永久損壞 ADS111x。防止過(guò)壓的一種方法是在輸入線上放置限流電阻。ADS111x 模擬輸入可承受高達(dá) 10 mA 的連續(xù)電流。狠狠的放電阻!!!

可以將未使用的模擬輸入連接到 GND,但可能會(huì)產(chǎn)生比以前的選項(xiàng)更高的泄漏電流。 浮動(dòng) NC(未連接)引腳,或?qū)?NC 引腳連接到 GND。如果未使用 ALERT/RDY 輸出引腳,請(qǐng)將該引腳懸空或使用弱上拉電阻將該引腳連接至 VDD。 以后ADC芯片上面不用的引腳應(yīng)該都可以這樣處理。 可以使用每個(gè)設(shè)備的不同地址引腳配置將最多四個(gè) ADS111x 設(shè)備連接到單個(gè) I2C總線。 使用地址引腳將 ADS111x 設(shè)置為四個(gè)不同的 I2C 地址之一。首先使用 GND、VDD 和 SCL 地址。如果使用 SDA 作為器件地址,請(qǐng)?jiān)?SCL 線變低后將 SDA 線保持為低電平至少 100 ns,以確保器件在 I 2 C 通信期間正確解碼地址。

串起來(lái)

顯示了同一 I2C 總線上的四個(gè) ADS111x 器件的示例。每條總線需要一組上拉電阻。可能需要降低上拉電阻值,以補(bǔ)償多個(gè)設(shè)備和增加的線路長(zhǎng)度帶來(lái)的額外總線電容。 主設(shè)備發(fā)送的第一個(gè)字節(jié)是 ADS111x 地址,后面是指示 ADS111x 偵聽(tīng)后續(xù)字節(jié)的R/ W位。 第二個(gè)字節(jié)是地址指針寄存器字節(jié)。從主機(jī)發(fā)送的第三和第四字節(jié)被寫(xiě)入寄存器地址指針位 P[1:0] 指示的寄存器。 ADS111x 的所有讀寫(xiě)事務(wù)都必須先有一個(gè) START 條件,后跟一個(gè) STOP 條件。

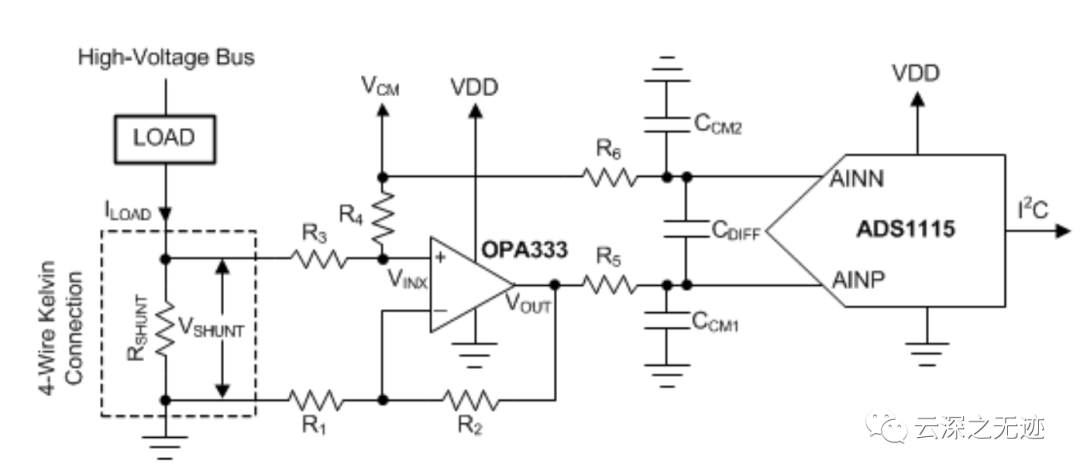

給了一個(gè)低側(cè)的電流檢測(cè),就是對(duì)地這塊的連接

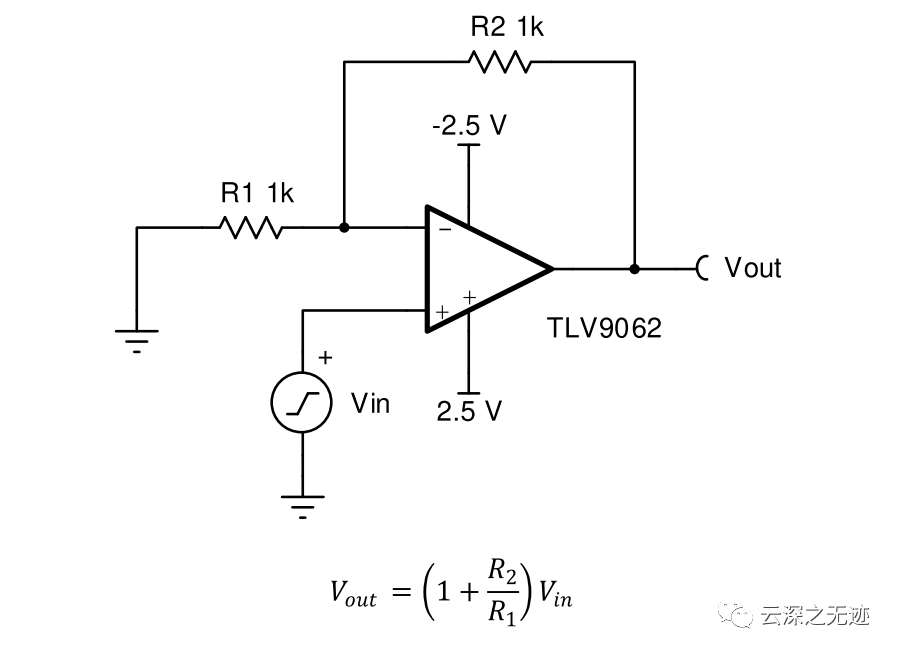

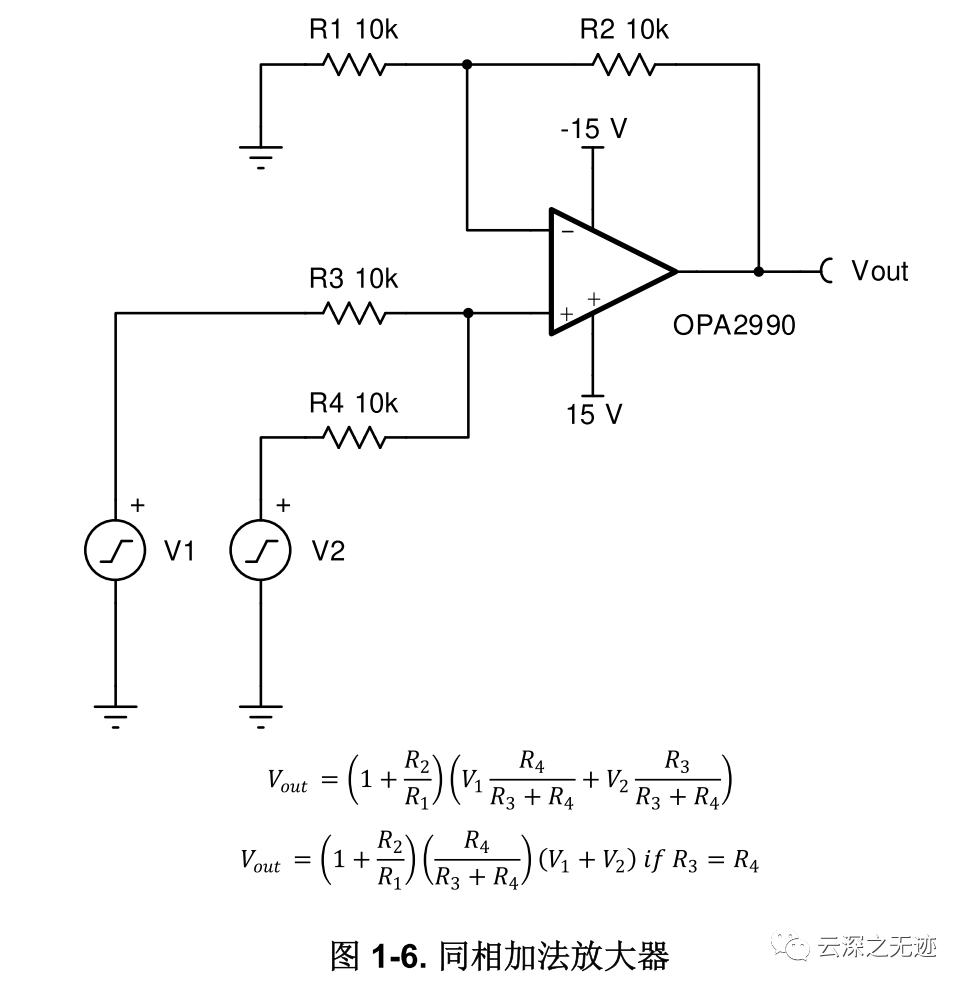

emmmm,這個(gè)放大電路我也看不懂了,運(yùn)放看是反向放大了。

除了是這個(gè)以外

我其實(shí)覺(jué)得是這個(gè),

應(yīng)用電路的第一級(jí)由同相求和放大器配置中的 OPA333 組成,有兩個(gè)用途:對(duì)接地參考信號(hào)進(jìn)行電平轉(zhuǎn)換,以允許在使用單極電源時(shí)進(jìn)行雙向電流測(cè)量。放大電平轉(zhuǎn)換電壓(V INX)。 感覺(jué)最有用的知識(shí)都在器件的數(shù)據(jù)手冊(cè)里面。

-

adc

+關(guān)注

關(guān)注

99文章

6635瀏覽量

548194 -

電平

+關(guān)注

關(guān)注

5文章

367瀏覽量

40396 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3294瀏覽量

127938

原文標(biāo)題:Ti.ADS1115-15Bit差分ADC

文章出處:【微信號(hào):TT1827652464,微信公眾號(hào):云深之無(wú)跡】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

ads1115差分采集負(fù)電壓一直是65535,為什么?

ADS1115讀取12V電壓,如何減少由電阻分壓帶來(lái)的誤差?

誰(shuí)用過(guò)ADS1115的差分啊 ,為什么我用差分通道,差值為正的時(shí)候沒(méi)有問(wèn)題,差值為負(fù)的時(shí)候輸出都是65534啊?

ADS1115是什么意思呢

ADS1115簡(jiǎn)介

【ROC-RK3568-PC開(kāi)發(fā)板試用體驗(yàn)】使用ADS1115擴(kuò)展ROC-RK3568-PC開(kāi)發(fā)板ADC功能

TI公司IIC接口16位AD模塊ADS1115

ads1115電壓測(cè)量范圍

基于51的ads1115詳細(xì)程序介紹

ads1115使用方法

基于MSP430F5529單片機(jī)的ADS1115

ADS1115使用及其驅(qū)動(dòng)電路

Ti.ADS1115-15Bit差分ADC

Ti.ADS1115-15Bit差分ADC

評(píng)論