一. 設(shè)計目標

1.編輯鏡像加法器電路原理圖。

2.對鏡像加法器進行仿真并觀察波形。

3.繪制鏡像加法器版圖,并進行 DRC 驗證。

4.對版圖電路進行仿真并觀察波形。

5.對電路網(wǎng)表進行 LVS 檢驗觀察原理圖與版圖的匹配程度。

二、鏡像加法器的電路結(jié)構(gòu)

鏡像加法器是一個經(jīng)過改進的加法器電路,首先,它取消了進位反相門;其次,門的 PUN 和 PDN 網(wǎng)絡(luò)不再是對偶的, 而是巧妙地實現(xiàn)了進位傳播 /產(chǎn)生/取消功能 ——當 D(D= ~(A+B) )或者 G(G=AB)為高時, ̄C0 分別被置為 VDD 或 GND。當滿足進位傳播條件時(即 P=A⊕B 為 1),輸入位以反相的形式傳播到 ̄C0,這一結(jié)構(gòu)的全加器單元僅需要 24 個晶體管,使面積和延時都有相當程度的減少。

其真值表如下表:(看C非和S非都為0時對應(yīng)的A、B、Ci,因為在鏡像設(shè)計中不采用反相器)

其真值表如下表:(看C非和S非都為0時對應(yīng)的A、B、Ci,因為在鏡像設(shè)計中不采用反相器)

由全加器的真值表可以得到,當A、B、Ci中只有一個輸入是1或者三個輸入都是1時,全加和輸出為1。且在A、B、C只有一個是1時,進位輸出是0.

由全加器的真值表可以得到,當A、B、Ci中任意2個輸入為1或三個輸入全為1時,進位輸出是1.

-

反相器

+關(guān)注

關(guān)注

6文章

315瀏覽量

44006 -

晶體管

+關(guān)注

關(guān)注

77文章

9970瀏覽量

140506 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30562 -

DRC

+關(guān)注

關(guān)注

2文章

153瀏覽量

36895 -

LVS

+關(guān)注

關(guān)注

1文章

37瀏覽量

10115

發(fā)布評論請先 登錄

加法器,加法器是什么意思

十進制加法器,十進制加法器工作原理是什么?

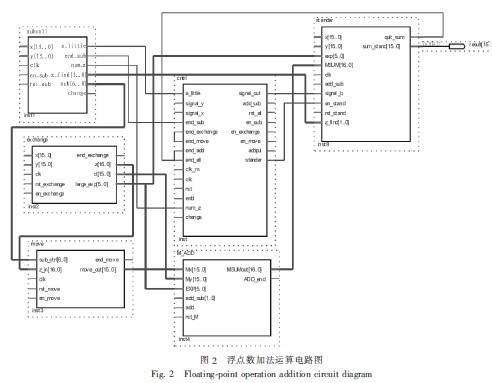

FPU加法器的設(shè)計與實現(xiàn)

同相加法器電路原理與同相加法器計算

加法器工作原理_加法器邏輯電路圖

超前進位加法器是如何實現(xiàn)記憶的呢

鏡像加法器的電路結(jié)構(gòu)及仿真設(shè)計

鏡像加法器的電路結(jié)構(gòu)及仿真設(shè)計

評論