01

帶隙基準(zhǔn)理論基礎(chǔ)

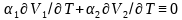

與溫度關(guān)系很小的電壓或者電流基準(zhǔn),在實(shí)際電路設(shè)計(jì)中具有重要的應(yīng)用,比如在電流鏡結(jié)構(gòu)中,需要對(duì)一“理想的”基準(zhǔn)電流進(jìn)行精確復(fù)制,這一“理想的”基準(zhǔn)電流,一般由帶隙基準(zhǔn)電路產(chǎn)生。怎樣才能產(chǎn)生一個(gè)對(duì)溫度變化保持恒定的量呢?我們可以這樣假設(shè):如果將兩個(gè)具有相反溫度系數(shù)的量,以適當(dāng)?shù)臋?quán)重進(jìn)行相加,那么最終的結(jié)果就會(huì)顯示出零溫度系數(shù)。例如,對(duì)于隨溫度變化向相反方向變化的電壓 和

和 來(lái)說(shuō),我們選取系數(shù)

來(lái)說(shuō),我們選取系數(shù) 和

和 ,使得

,使得 ,這樣就得到了具有零溫度系數(shù)的電壓基準(zhǔn)

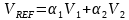

,這樣就得到了具有零溫度系數(shù)的電壓基準(zhǔn) 。下面,我們將分析,如何產(chǎn)生這兩種隨溫度變化反方向變化的電壓。

。下面,我們將分析,如何產(chǎn)生這兩種隨溫度變化反方向變化的電壓。

02

負(fù)溫度系數(shù)電壓

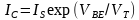

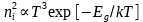

雙極性晶體管的基極-發(fā)射極電壓,具有負(fù)溫度系數(shù)。對(duì)于一個(gè)雙極性器件,我們可以寫(xiě)出 ,其中,

,其中, ,飽和電流

,飽和電流 正比于

正比于 ,其中

,其中 為少數(shù)載流子濃度,

為少數(shù)載流子濃度, 為硅的本征載流子濃度。這些參數(shù)與溫度的關(guān)系可以表示為

為硅的本征載流子濃度。這些參數(shù)與溫度的關(guān)系可以表示為 ,其中,

,其中, ,并且

,并且 ,其中,

,其中, ,為硅的帶隙能量,所以有:

,為硅的帶隙能量,所以有:

其中,b為一比例系數(shù)。寫(xiě)出 ,我們就可以計(jì)算基極-發(fā)射極電壓隨溫度的系數(shù)了。在

,我們就可以計(jì)算基極-發(fā)射極電壓隨溫度的系數(shù)了。在 對(duì)T取導(dǎo)數(shù)時(shí),我們一定要知道

對(duì)T取導(dǎo)數(shù)時(shí),我們一定要知道 也是溫度的系數(shù)。為了簡(jiǎn)化分析,我們暫時(shí)假設(shè)

也是溫度的系數(shù)。為了簡(jiǎn)化分析,我們暫時(shí)假設(shè) 保持不變,這樣有:

保持不變,這樣有:

于是我們有:

所以有:

最終可得到:

上式給出了在給定溫度T下基極-發(fā)射極電壓的溫度系數(shù),從中可以看出,它與 本身的大小有關(guān)。當(dāng)

本身的大小有關(guān)。當(dāng) ,T=300K時(shí),

,T=300K時(shí), 。

。

03

正溫度系數(shù)電壓

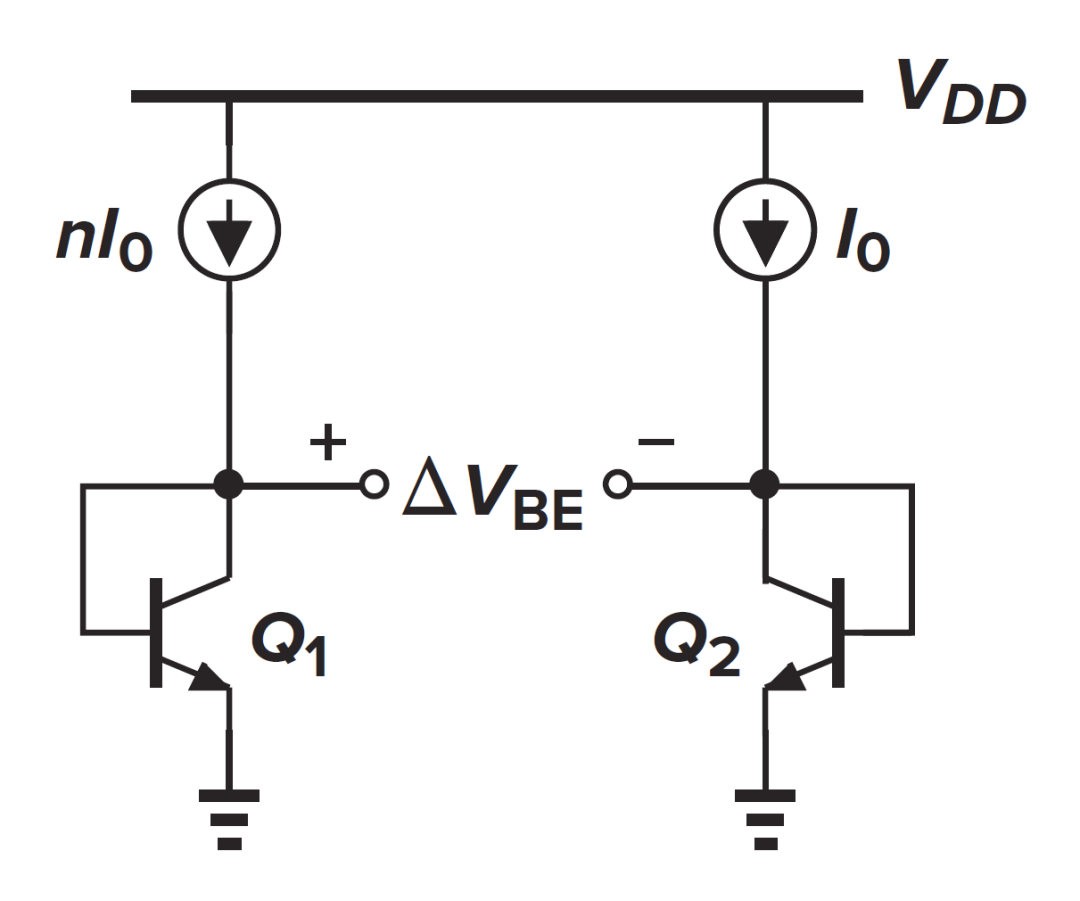

如果兩個(gè)雙極性晶體管工作在不相等的電流密度下,那么它們的基極-發(fā)射極電壓的差值就與絕對(duì)溫度成正比。

圖一

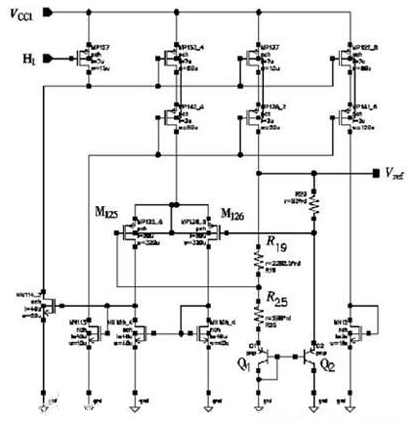

對(duì)于圖一,如果兩個(gè)同樣的晶體管( )偏置的集電極電流分別為

)偏置的集電極電流分別為 和

和 并忽略它們的基極電流,那么有:

并忽略它們的基極電流,那么有:

這樣, 的差值就表現(xiàn)出正溫度系數(shù):

的差值就表現(xiàn)出正溫度系數(shù):

04

帶隙基準(zhǔn)

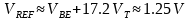

利用上面得到的正、負(fù)溫度系數(shù)的電壓,我們現(xiàn)在可以設(shè)計(jì)出一個(gè)令人滿意的零溫度系數(shù)的基準(zhǔn)。我們有 ,這里

,這里 是兩個(gè)工作在不同電流密度下的雙極性晶體管的基極-發(fā)射極電壓的差值。那么我們?cè)趺催x擇系數(shù)

是兩個(gè)工作在不同電流密度下的雙極性晶體管的基極-發(fā)射極電壓的差值。那么我們?cè)趺催x擇系數(shù) 和

和 呢?在室溫下,

呢?在室溫下, ,

, ,因此我們可以選擇令

,因此我們可以選擇令 ,選擇

,選擇 使得

使得 ,也就是

,也就是 ,這樣得到的零溫度系數(shù)的基準(zhǔn)為:

,這樣得到的零溫度系數(shù)的基準(zhǔn)為:

05

實(shí)現(xiàn)電路

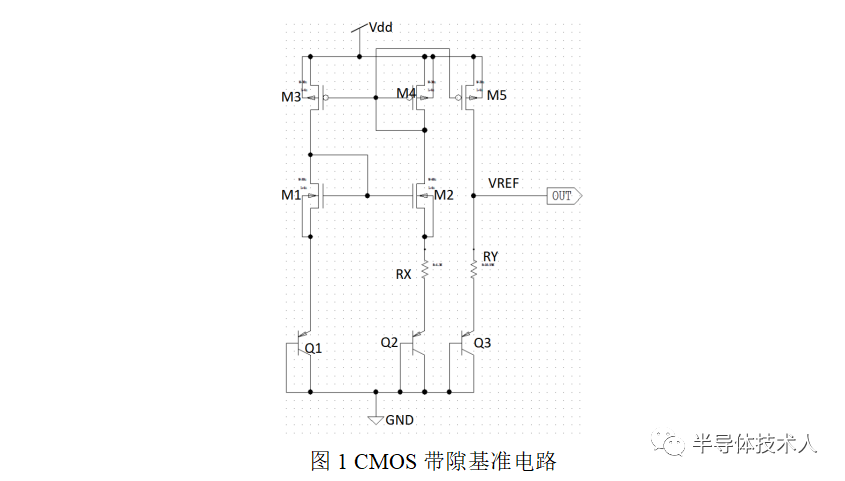

圖二

圖二為帶隙基準(zhǔn)電路的實(shí)現(xiàn)原理圖,Q1為單個(gè)晶體管,Q2為n個(gè)并聯(lián)的晶體管,我們?cè)赬點(diǎn)和Y點(diǎn)引入運(yùn)算放大器,利用運(yùn)算放大器的特性強(qiáng)制X點(diǎn)和Y點(diǎn)點(diǎn)位相等,那么有 ,即

,即 I=

I= ,所以有

,所以有 。選擇

。選擇 ,我們有輸出電壓為:

,我們有輸出電壓為:

我們選擇合適的電阻值,即可滿足 的條件。例如,可以選擇n=31,

的條件。例如,可以選擇n=31, 。

。

06

總結(jié)

至此,我們已經(jīng)完成了最簡(jiǎn)單的帶隙基準(zhǔn)電路的設(shè)計(jì)。在實(shí)際電路中,由于運(yùn)放的輸入失調(diào)等效應(yīng),還需要加入反饋回路等結(jié)構(gòu),以確保帶隙基準(zhǔn)電路能夠穩(wěn)定的工作。最終實(shí)現(xiàn)的電路會(huì)相對(duì)復(fù)雜,但是核心電路的原理基本上大同小異。

-

運(yùn)算放大器

+關(guān)注

關(guān)注

216文章

5662瀏覽量

175725 -

電流鏡

+關(guān)注

關(guān)注

0文章

44瀏覽量

17507 -

晶體管

+關(guān)注

關(guān)注

77文章

9977瀏覽量

140618 -

帶隙基準(zhǔn)電路

+關(guān)注

關(guān)注

0文章

14瀏覽量

10805 -

偏置電壓

+關(guān)注

關(guān)注

0文章

154瀏覽量

13441

發(fā)布評(píng)論請(qǐng)先 登錄

基于LDO穩(wěn)壓器的帶隙基準(zhǔn)電壓源設(shè)計(jì)

一種高精度BiCMOS電流模帶隙基準(zhǔn)電路設(shè)計(jì)

帶隙基準(zhǔn)是什么?帶隙基準(zhǔn)的結(jié)構(gòu)是由哪些部分組成的?

帶隙基準(zhǔn)電路的研究

帶隙基準(zhǔn)源的現(xiàn)狀及其發(fā)展趨勢(shì)

基于汽車(chē)環(huán)境的帶隙基準(zhǔn)電壓源的設(shè)計(jì)

低溫漂低功耗的帶隙基準(zhǔn)源技術(shù)設(shè)計(jì)

新型BiCMOS帶隙基準(zhǔn)電路的設(shè)計(jì)

帶隙電壓基準(zhǔn)源的設(shè)計(jì)與分析

帶隙基準(zhǔn)電壓源及過(guò)溫保護(hù)電路

cmos帶隙基準(zhǔn)電壓源設(shè)計(jì)

帶隙基準(zhǔn)電路_cmos無(wú)運(yùn)放帶隙基準(zhǔn)源

帶隙基準(zhǔn)是什么_帶隙基準(zhǔn)電路的優(yōu)點(diǎn)

帶你認(rèn)識(shí)帶隙基準(zhǔn)電路

帶你認(rèn)識(shí)帶隙基準(zhǔn)電路

評(píng)論