仿真和驗證是開發(fā)任何高質量的基于 FPGA 的 RTL 編碼過程的基礎。在前文中,我們介紹了面向實體/塊的仿真,并介紹了如何在虹科的IP核中執(zhí)行面向全局的仿真。

前文回顧

虹科干貨 | 如何測試與驗證復雜的FPGA設計(1)——面向實體或塊的仿真

虹科干貨 | 如何測證復雜的FPGA設計(2)——如何在虹科的IP核中執(zhí)行面向全局的仿真

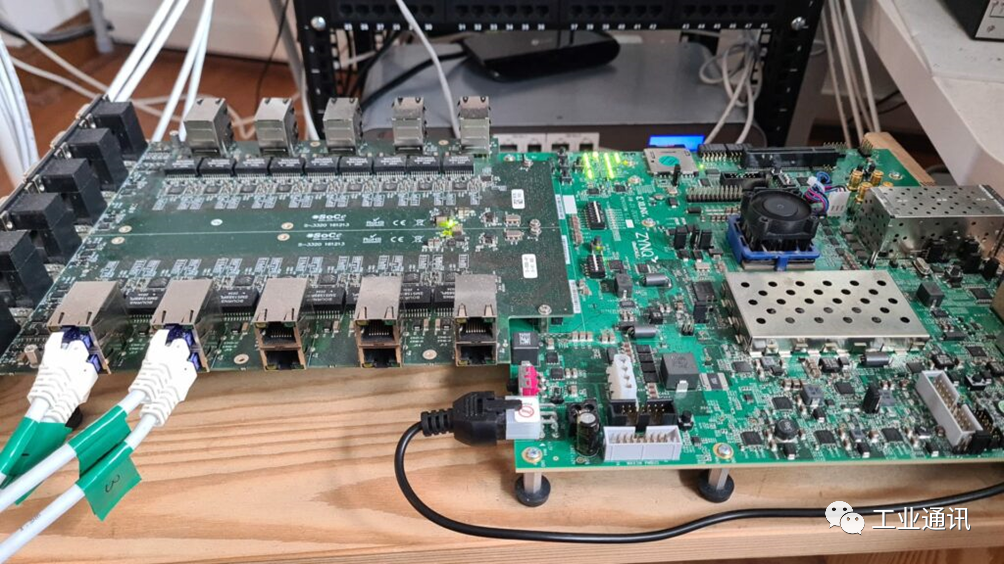

盡管擴展的仿真計劃提供了良好的可信度,但仍有許多corner的情況無法在虛擬環(huán)境中驗證。對于這些情況,開發(fā)人員需要制定基于硬件的測試計劃,而這也是獲得高質量結果的最后一步。在本篇文章中,我們將對介紹第三個關鍵步驟——在硬件平臺上驗證IP核。

硬件測試

硬件測試是為IP核產品執(zhí)行高質量測試和驗證計劃的最后一步,主要可以分為以下幾個階段:

1

測試準備

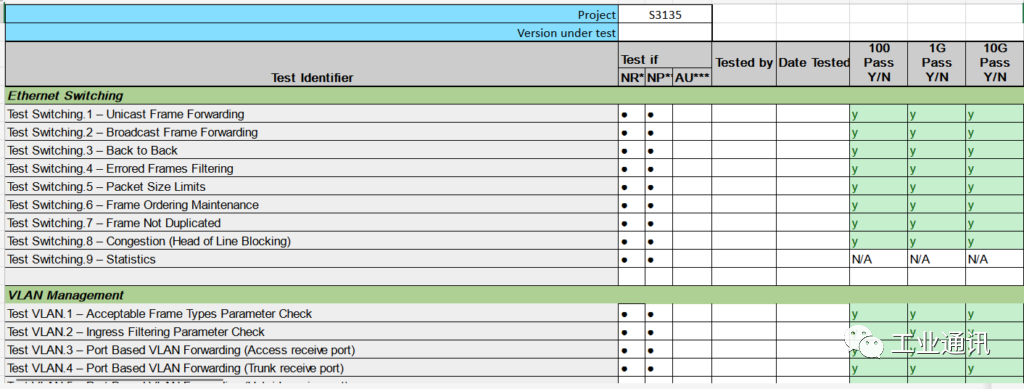

該階段定義了在產品開始測試之前必須完成的步驟。在這個階段,需要制定測試計劃文檔,里面詳細描述了必須在 DUT(被測設備)上執(zhí)行的每一項測試。

2

測試執(zhí)行

測試執(zhí)行階段主要是執(zhí)行上一個階段中制定的測試用例

3

問題報告

該階段需要檢查和報告在測試執(zhí)行期間檢測到的所有問題,虹科技術團隊將提供一個問題電子表格,其中將記錄在測試階段檢測到的每個問題。每當注冊新問題時,都會向開發(fā)團隊報告,并且能夠追蹤哪些問題已解決,哪些問題仍有待審查。

4

測試結束

該階段確定測試階段何時完成,并創(chuàng)建測試結果文檔,其中將包含成功執(zhí)行的測試的摘要以及有關測試的更多相關信息。

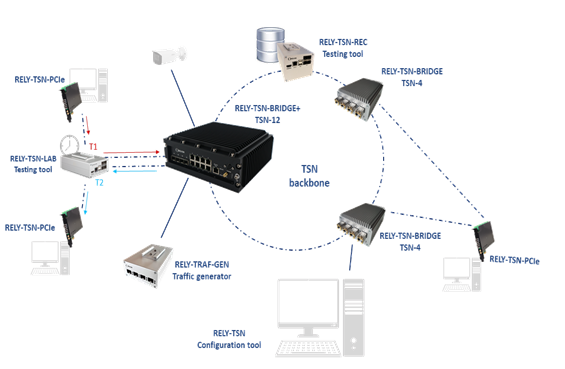

虹科SoC-e測試工具

為了優(yōu)化測試執(zhí)行過程,我們使用了虹科SoC-e測試工具,以進行自動化測試。該工具考慮了以下內容:

DUT配置過程

流量注入和嗅探

記錄從DUT 返回的流量

驗證保存的日志

將DUT 設置為原始狀態(tài)

虹科SoC-e測試軟件架構

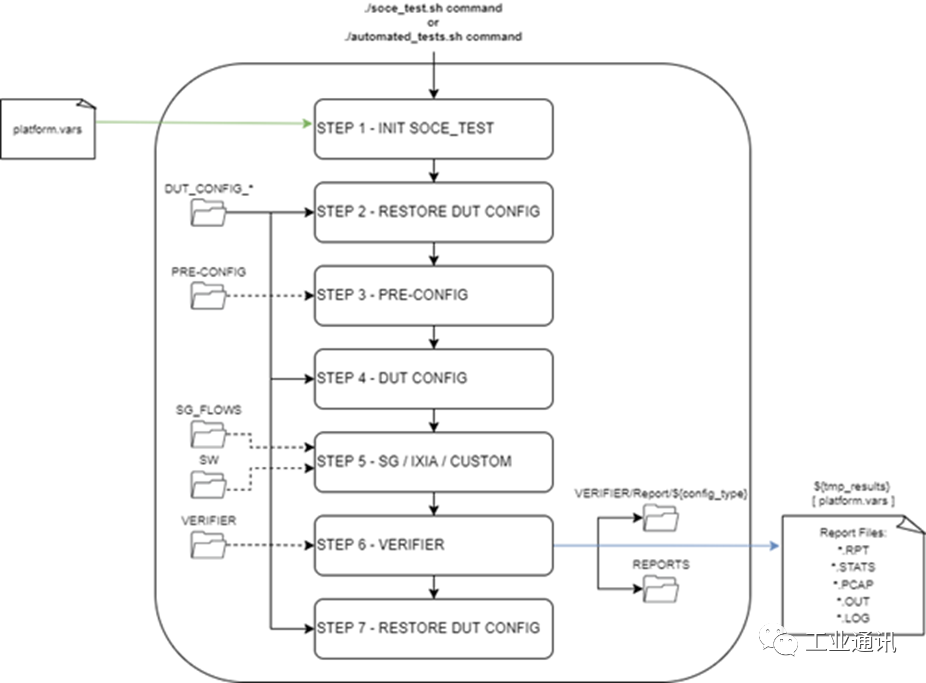

該工具的第一步與DUT 配置的執(zhí)行有關。這是通過名為 Platform.vars 的輸入配置文件完成的。通過該文件,用戶可以配置不同的參數(shù),如 DUT SSH 參數(shù)、主機 PC 的IP 地址或網絡接口。

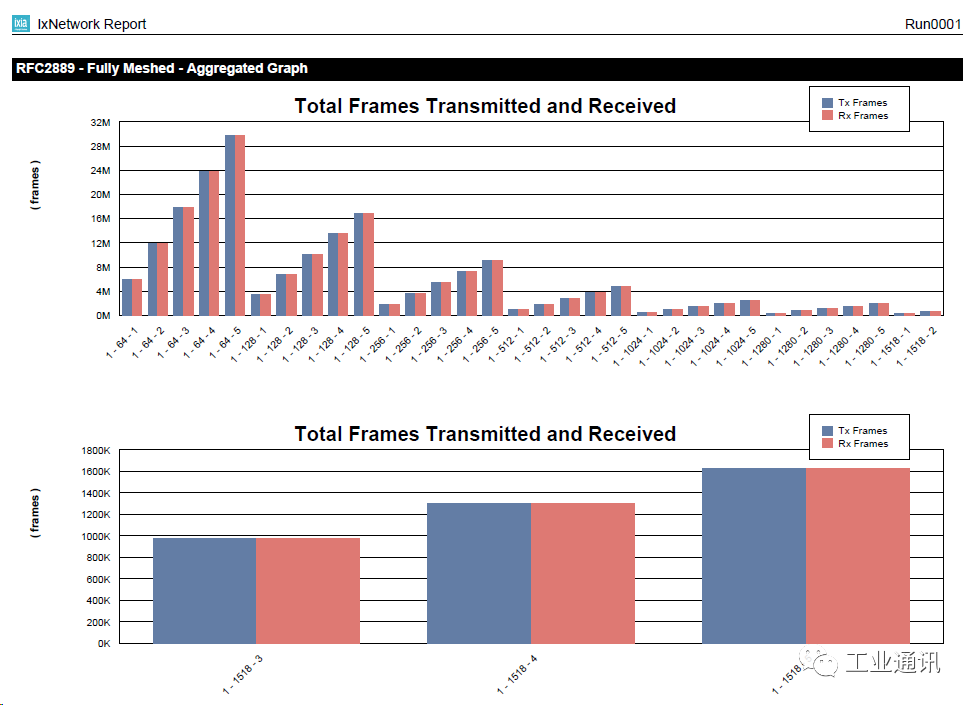

第二步,完成TS(測試站)和 DUT之間的流量注入和嗅探。我們有不同的第三方設備用作測試站,但最常用的設備之一是IXIA Novus One Plus。流量可以通過 IXIA 的 Python API 輕松發(fā)送。數(shù)據(jù)包操作是通過 Scapy Python 模塊完成的。盡管 Scapy 允許傳輸該工具生成的所有流量,但它是使用不同的工具tcpreplay執(zhí)行的。這使我們能夠克服由 Scapy 引起的帶寬和準確性方面的某些限制。在此步驟中,測試提供了自定義流量的靈活性,以驗證不同的 DUT 功能。可擴展性不是問題,因為該工具支持添加額外的流量和測試端口。

第三步,該工具使用測試站或通過 Linux tcpdump 軟件登記來自 DUT 的流量。

第四步,在虹科SoC-e測試工具驗證上一步中存儲的信息(統(tǒng)計、寄存器轉儲(dump)等),以檢查一切是否正常。通過這兩個步驟,SoC-e 測試工具為測試用例的驗證提供了一個很好的解決方案。

最后,第五步,也是最后一步。最后一步的主要目的是將 DUT 配置恢復到其原始狀態(tài),因為它可能在測試期間被修改。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

27133

發(fā)布評論請先 登錄

CAN芯片邏輯響應驗證測試

工程師必看!PWM波控制全攻略,虹科LIN模塊助力開發(fā)效率翻倍

是德科技攜手Alea成功驗證3GPP EUTRA任務關鍵型測試用例

虹科直播回放 | IO-Link技術概述與虹科IO-Link OEM

?憶聯(lián)企業(yè)級測試驗證平臺介紹

虹科方案 僅需4個步驟!輕松高效搭建虹科TSN測試網絡

Verilog 測試平臺設計方法 Verilog FPGA開發(fā)指南

虹科方案 | 精準零部件測試!多路汽車開關按鍵功能檢測系統(tǒng)

【干貨分享】硬件在環(huán)仿真(HiL)測試

虹科技術前沿 TSN網絡中時間感知整形器的性能驗證實測

TSN網絡中時間感知整形器的性能驗證實測

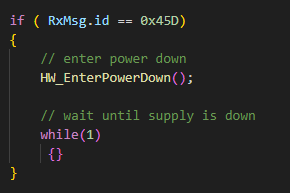

虹科干貨 |?突破功耗限制:PCAN Router設備低功耗模式與高效喚醒

虹科干貨 | 如何測試與驗證復雜的FPGA設計(3)——硬件測試

虹科干貨 | 如何測試與驗證復雜的FPGA設計(3)——硬件測試

評論