1.為什么說DSP+FPGA架構更適合視頻采集處理?

高性能的算法處理,使用硬件描述語言去編寫算法的話,復雜程度高,工作量大,不易調試,產品的開發周期將非常長。這時,如果為系統添加專為算法而生的DSP的話,將會事半功倍。

眾所周知,DSP有專門為數字信號處理所設計的指令集和流水線,可 以方便高效的執行浮點數和復數運算等,這樣我們的理論算法就可以很方便的移植到實際的工程中,可以有效的縮短產品的開發周期。

DSP+FPGA的架構,可以把FPGA的高速采集和DSP的高性能算法處理完美結合。這種高度平衡的特性集合使其非常適合各種高性能嵌入式應用場合,如:

■ 視頻追蹤

■ 圖像處理

■ 軟件無線電

■ 雷達探測

■ 光電探測

■ 水下探測

■ 定位導航

2. DSP+FPGA經典組合——C6678+Kintex-7

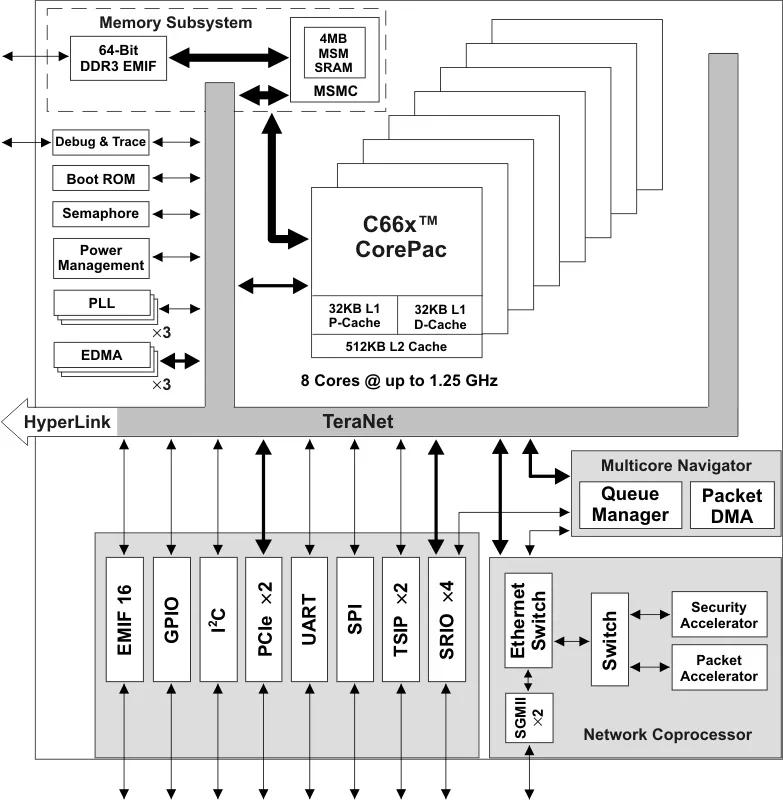

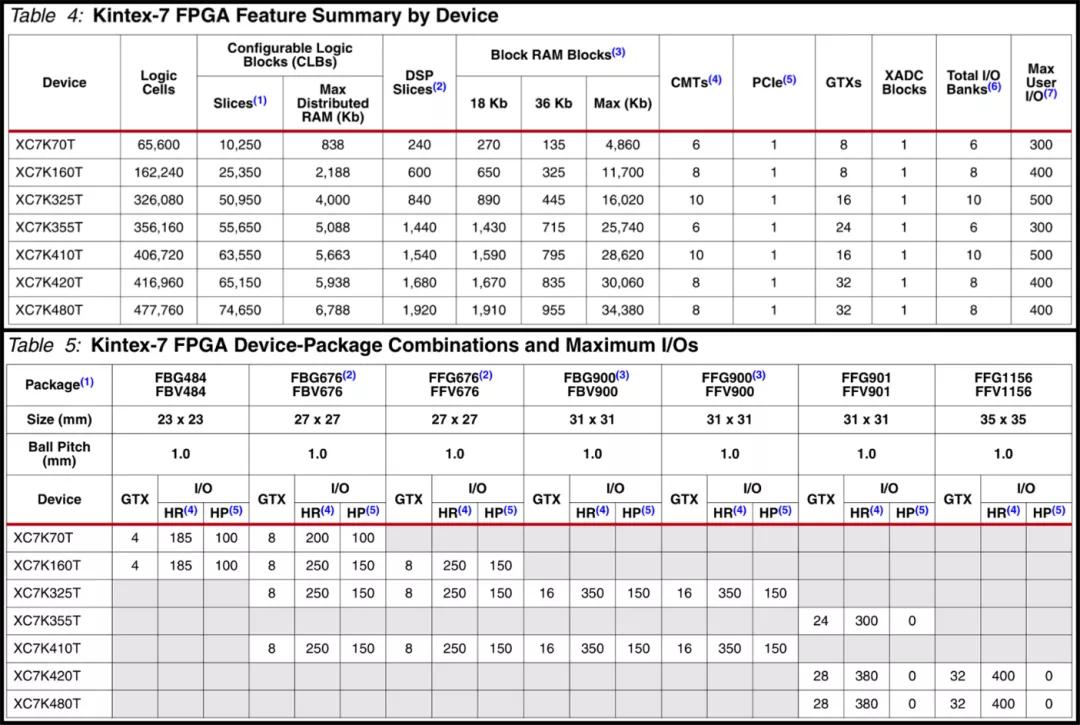

在高速圖像處理領域,TMS320C6678與Kintex-7進行搭配的DSP+FPGA架構堪稱經典中經典,C6678擁有8核C66x,每核主頻高達1.25GHz,同時擁有高達320 GMAC和160 GFLOP的運算能力,可輕松駕馭圖像的復雜算法。配合Kintex-7的高速采集,完美契合各種視頻采集場景。

圖 1 TMS320C6678處理器功能框圖

圖 2 Kintex-7特性

本文基于C6678+Kintex-7平臺,為大家介紹CameraLink、SDI、PAL、HDMI的視頻采集處理綜合案例。

3. 硬件平臺

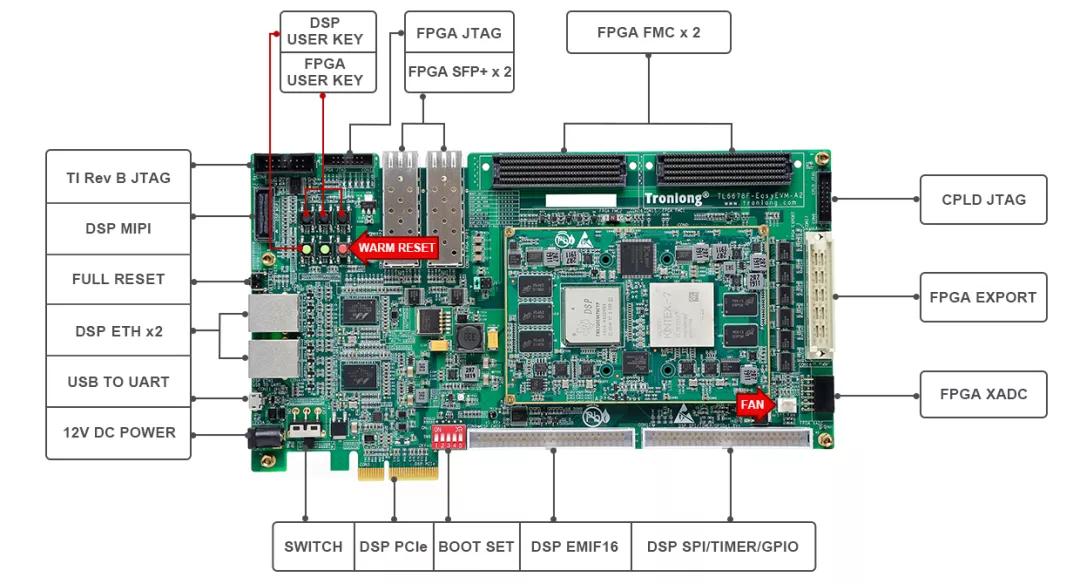

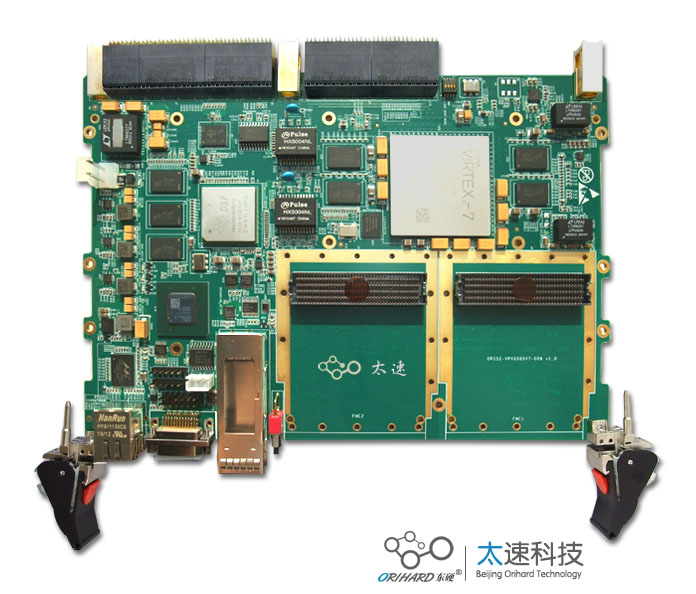

圖 3 TL6678F-EasyEVM評估板

TL6678F-EasyEVM評估板通過FMC高速接口,可接入CameraLink、SDI、PAL、HDMI等視頻采集模塊,并基于各個模塊提供了DSP+FPGA視頻采集處理綜合案例,同時提供免費技術支持服務。

4. 視頻采集處理方案

4.1 CameraLink視頻采集處理

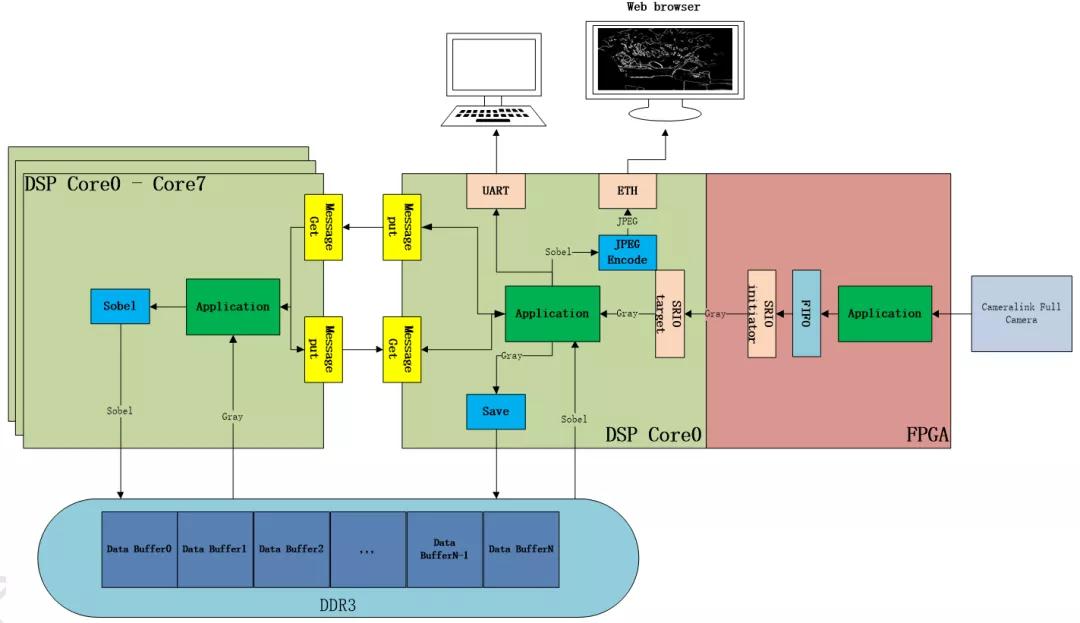

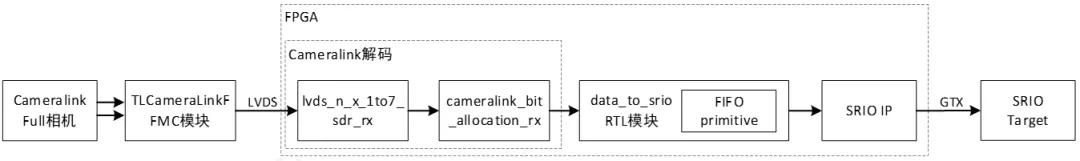

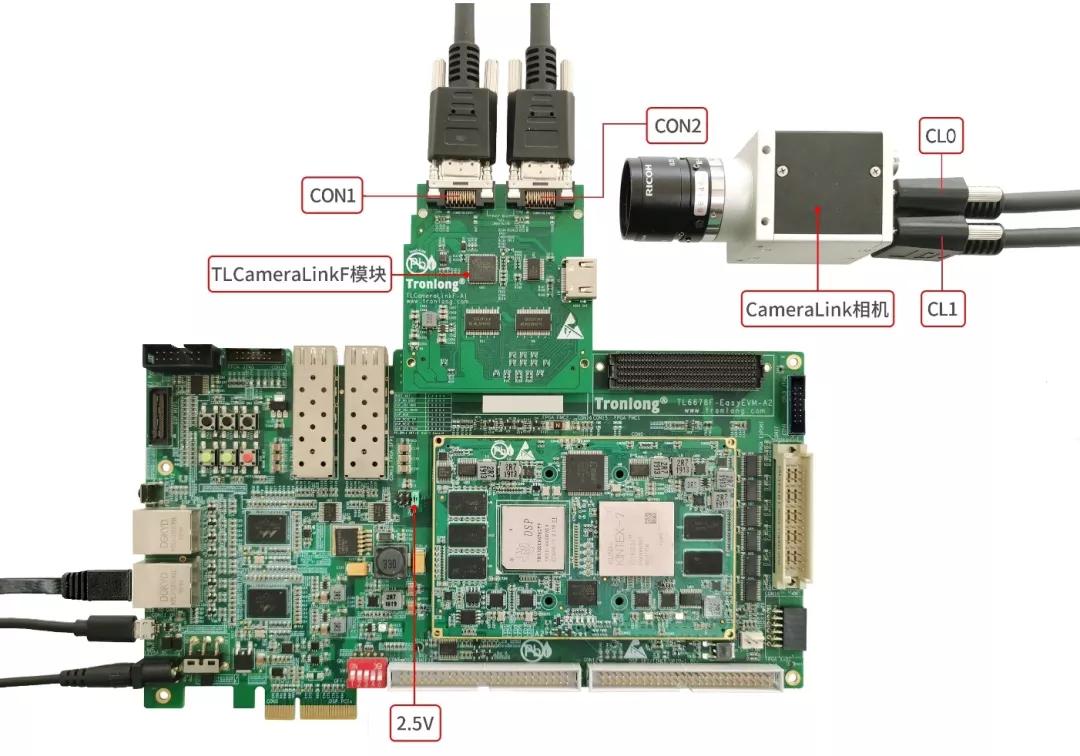

FPGA端通過FMC視頻模塊TLCameraLinkF的CameraLink接口進行分辨率為2560 x 2048的視頻采集,再經過SRIO總線將視頻數據傳輸至DSP端進行Sobel(邊緣檢測)算法處理,然后將經處理后的圖像通過網頁進行顯示。

FPGA端作為SRIO Initiator,DSP端作為SRIO Target。FPGA端通過SRIO SWRITE和乒乓方式,將數據傳輸至DSP端的0x90000000和0x90500000的DDR地址空間。

案例使用北京微視的黑白CameraLink相機RS-A5241-CM107-S00,分辨率為2560 x 2048,幀率為107,灰度輸出,每個像素8bit,則數據量為2560 x 2048 x 107 x 8 = 4487905280 ≈ 4.5Gbps。案例使用SRIO的兩個Lanes,每個Lane傳輸速率為5Gbps,總數據有效帶寬為5Gbps x 2 x 80% = 8Gbps。

圖 4 案例功能框圖

圖 5 FPGA端程序功能框圖

圖 6 CameraLink模塊

圖 7 硬件連接

圖 8 測試效果圖

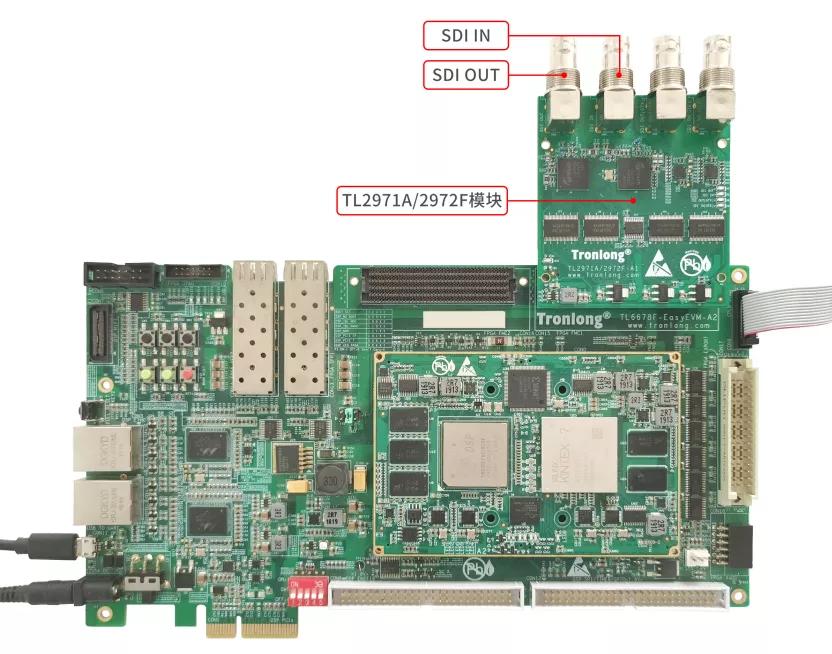

4.2 SDI視頻采集處理

Kintex-7 FPGA通過使用Video In to AXI4-Stream IP核,將SDI視頻模塊TL2971A/2972F的SDI IN接口輸入的1080P60的視頻采集進來,并通過VDMA緩存到DDR,最后通過AXI4-Stream to Video Out IP核將視頻從模塊的SDI OUT接口輸出顯示。其中VDMA通過Microblaze配置。

圖像數據亦可通過SRIO高速總線傳輸到TMS320C6678 DSP進行算法處理,并返回處理結果。

圖 9

圖 10 硬件連接

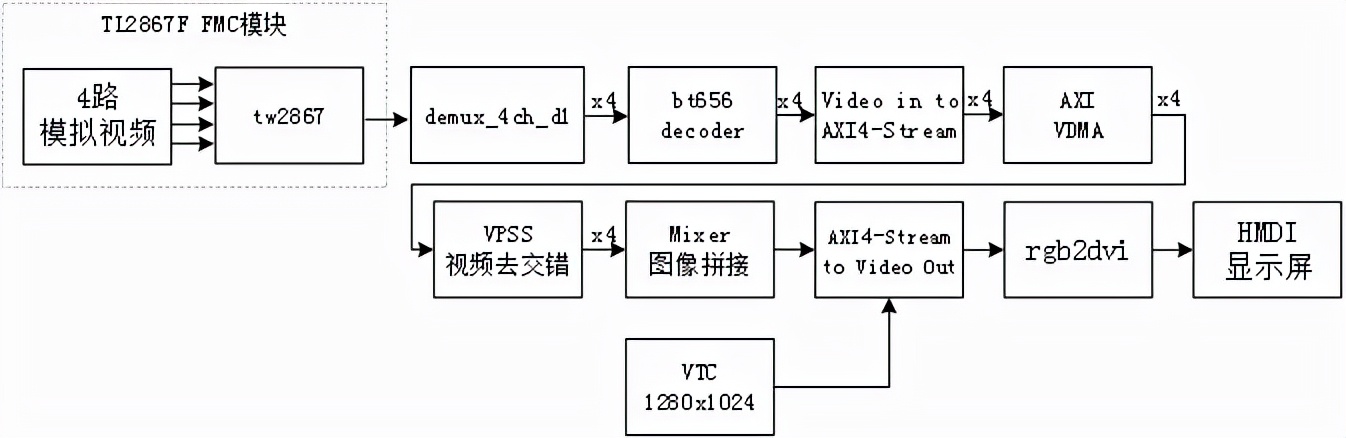

4.3 PAL視頻采集處理(4路D1)

在Kintex-7 FPGA上搭建MicroBlaze軟核,并由MicroBlaze配置PAL視頻模塊TL2867F和各IP核,將模塊輸出的一路4通道D1時分復用的復合視頻,拆分成4路獨立的BT656嵌入式同步視頻,再將4路視頻進行BT656解碼分離出同步信號和像素數據。使用VDMA IP緩存到內存設備上,通過VPSS IP將4路圖像進行去交錯,然后由Mixer IP將四路圖像拼接起來,通過rgb2dvi邏輯模塊,將RGB視頻信號轉換為DVI視頻信號,最后通過模塊的HDMI1接口輸出顯示到顯示器。支持PAL制式(分辨率為720x576)視頻輸入,輸出顯示分辨率為1280x1024。

圖像數據亦可通過SRIO高速總線傳輸到TMS320C6678 DSP進行算法處理,并返回處理結果。

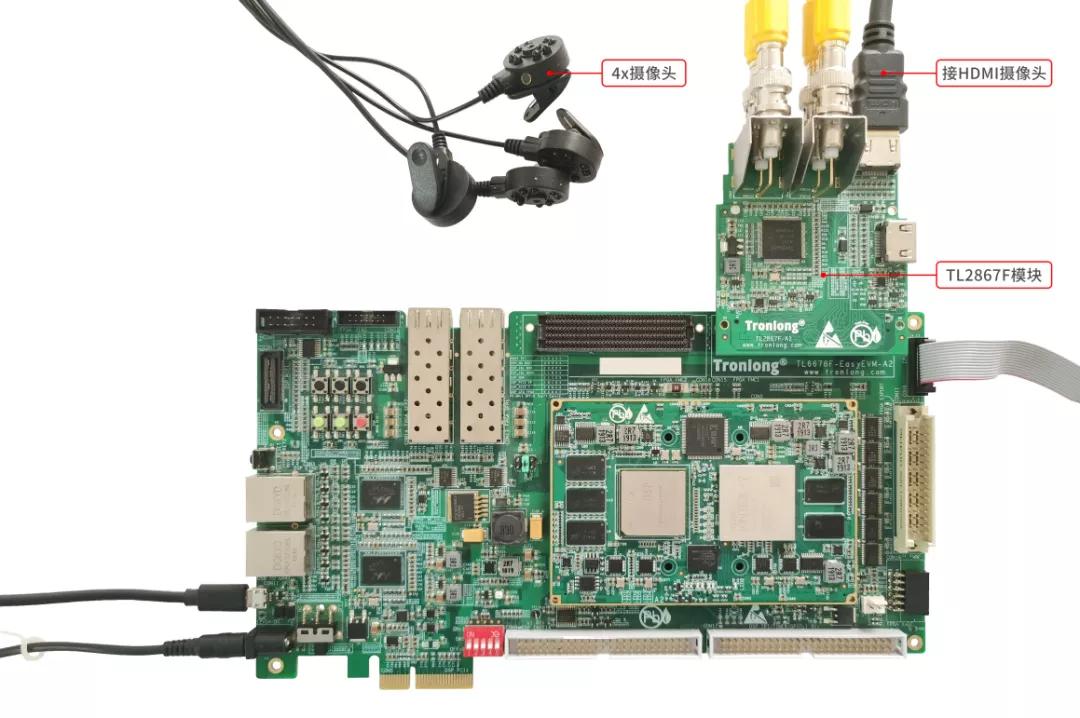

圖 11

圖 12

圖 13 硬件連接

圖 14

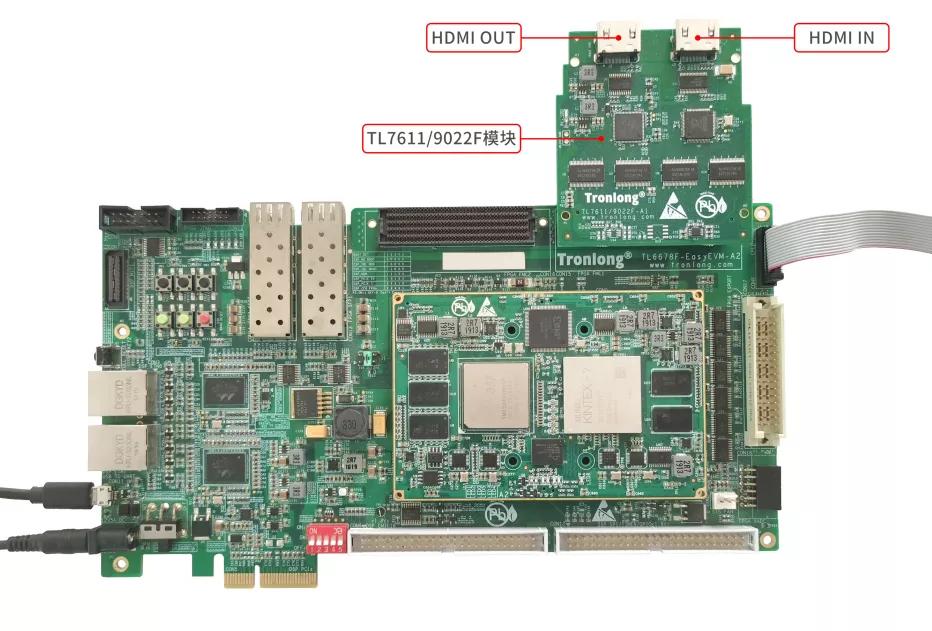

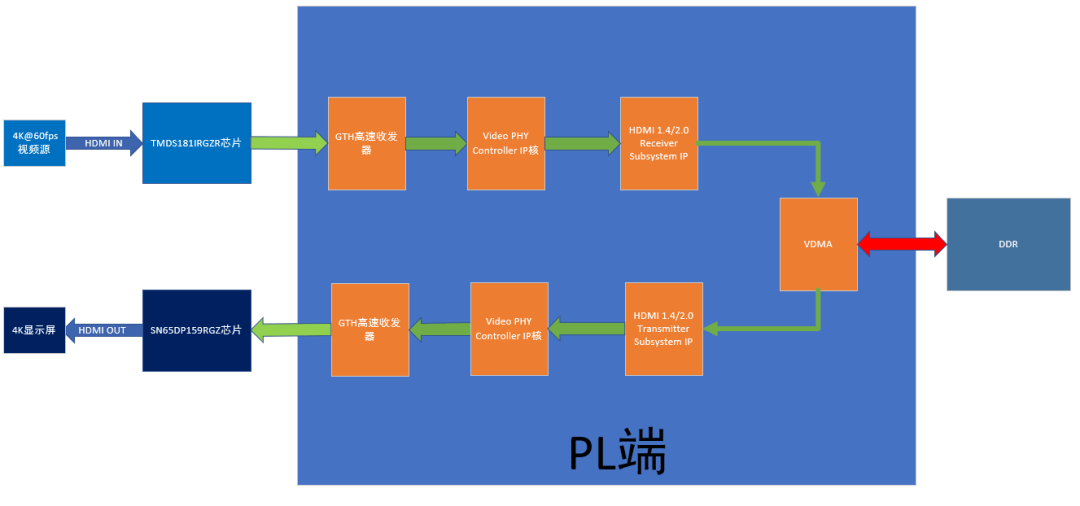

4.4 HDMI視頻采集處理

Kintex-7 FPGA使用Video In to AXI4-Stream IP核,通過HDMI視頻采集模塊TL7611/9022F的HDMI IN接口將1080P60視頻采集進來,并通過VDMA緩存到DDR,最后通過AXI4-Stream to Video Out IP核將視頻從模塊的HDMI OUT接口輸出顯示。其中VDMA IP核,HDMI OUT芯片(SIL9022)和HDMI IN芯片(ADV7611)通過MicroBlaze運行裸機程序進行配置。

圖像數據亦可通過SRIO高速總線傳輸到TMS320C6678 DSP進行算法處理,并返回處理結果。

圖 15

圖 16 硬件連接

-

dsp

+關注

關注

555文章

8139瀏覽量

355022 -

FPGA

+關注

關注

1643文章

21949瀏覽量

613715 -

嵌入式

+關注

關注

5136文章

19515瀏覽量

314503 -

硬件開發

+關注

關注

3文章

169瀏覽量

24662 -

TMS320C6678

+關注

關注

3文章

39瀏覽量

18451

發布評論請先 登錄

基于STM32的數據采集+心率檢測儀(原理圖、PCB、程序源碼等)

TYPE-C與HDMI聯合,打造雙4K USB3.0采集模塊

解鎖4K,Xilinx MPSoC ARM + FPGA高清視頻采集與顯示方案!

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

FMC子卡設計方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數據處理核心板

使用的是LMH0344+LMH0341+xilinx Kintex 7方案,出現采集數據錯誤的原因?

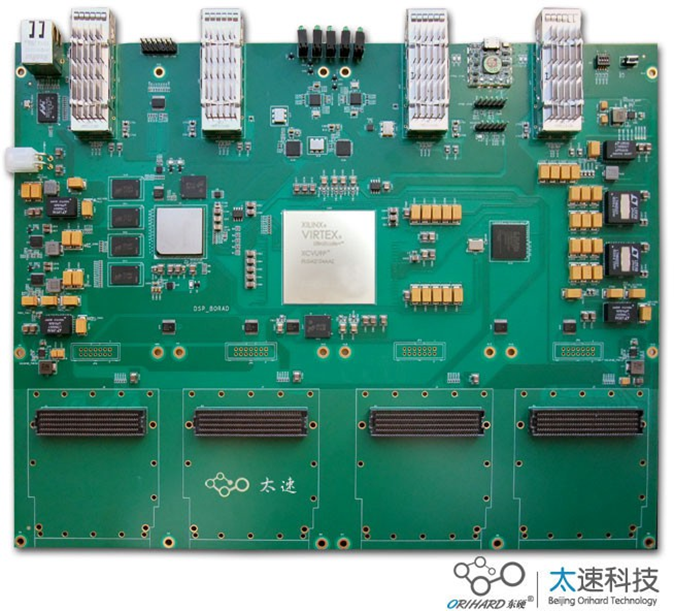

6U CPCI板卡設計方案:8-基于雙TMS320C6678 + XC7K420T的6U CPCI Express高速數據處理平臺

AMS-MS4K_C:4K多畫面視頻拼接處理器,重塑視覺盛宴的新標桿

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡

TMS320C6678多核固定和浮點數字信號處理器數據表

SM320C6678-HIREL多核固定和浮點數字信號處理器數據表

源碼免費下載!C6678+K7視頻采集處理方案,這里全都有

源碼免費下載!C6678+K7視頻采集處理方案,這里全都有

評論