01

遠端簇型拓撲介紹

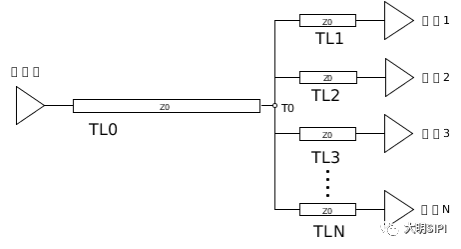

下圖為遠端簇型拓撲結構的示意圖。從驅動器到分支點T0這段傳輸線TL0的長度相對于分支點到各個負載處傳輸線TL1~TLN要長很多。這種結構多用于多個負載的位置相對集中的情況。

其拓撲結構有如下特點:

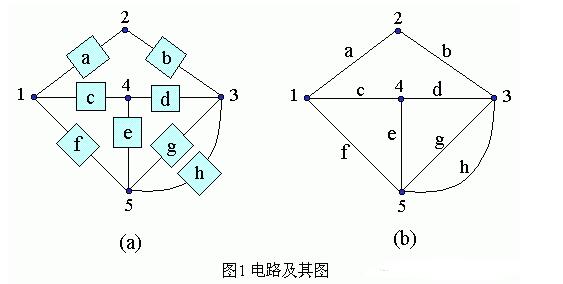

1.鏈路中只有T0一個阻抗不連續點;

2.負載很多時T0點前后的阻抗突變很大。T0點前阻抗為

,在有N個負載的情況下T0點后的阻抗為

,在有N個負載的情況下T0點后的阻抗為

也就是說負載數越多入射波在T0點發生的負反射越嚴重。

3.此外,從各個負載反射回源端的反射信號到達T0點也會發生負反射。如果T0點到各個負載的布線TL1~TLN沒有嚴格控制等長的話,負載之間的相互影響就會變得很嚴重。

4.當TL1~TLN嚴格控制等長時,所有負載的接收波形一致性會非常好。這也給解決信號完整性問題帶來了方便。

使用ADS搭建一個一驅三的遠端簇拓撲。驅動器為3.3VLVCMOS電平,輸出阻抗20ohm、上升時間為500ps、下降時間1ns左右;TL0長度為2000mil,TL1=TL2=TL3=1000mil。

傳輸線的延時按照6mil/ps計算,分支線TL1~TL3的延時為166ps左右,已經達到了上升時間的1/3,分支線能夠體現傳輸線效應。

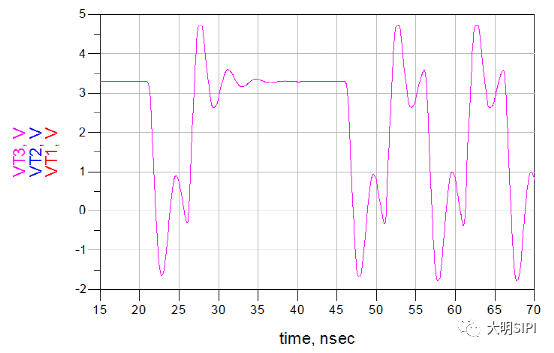

仿真結果如下所示,信號邊沿單調、由于驅動器輸出過驅動,負載接收波形存在較大的過沖和振鈴,且三個負載的接收波形完全重疊。

02

遠端簇拓撲的SI分析

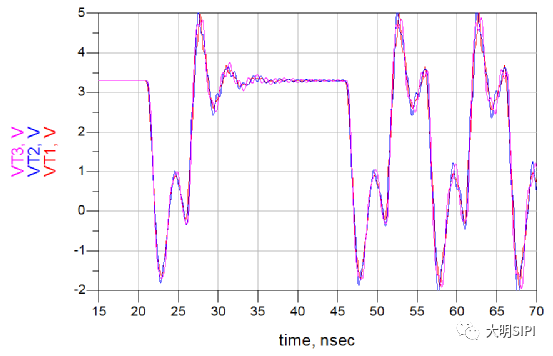

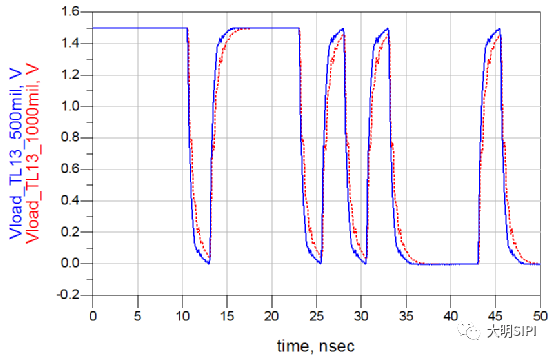

那么當T0點到各個負載的布線長度不同時又會出現什么現象呢?我們將TL1調整到500mil,TL3調整到1500mil,TL2為1000mil不變。此時的仿真結果如下所示:

當T0點到各個負載的布線長度不等長時三個負載的接收波形就出現了差異:

1.所有負載在接收波形在穩定電平處都會有幅度微小的震蕩,而且信號的過沖明顯超過了TL1、TL2、TL3等長時的幅度。

2.這些震蕩和過沖的增大就來自于三個負載之間的相互影響,但這一影響并不足以影響信號質量,而接收波形中存在的過沖顯而易見是由于驅動器驅動能力過強導致只需要添加源端匹配即可解決。

3.由此可見一般的LVTTL或者CMOS電平的低速總線的設計,使用遠端簇的拓撲大多能夠解決信號完整性問題。

?T0點到負載端布線延時的影響

除了需要保證各個負載所在分支布線等長外,還需要注意分支的延時。雖然相比菊花鏈拓撲遠端簇拓撲已經極大的改善了信號質量,但我們也需要注意拓撲中畢竟還是存在T0點這個阻抗不連續點。在遠端簇拓撲中負載的個數、T0點到負載的布線延時、驅動器輸出信號的上升時間對負載端接收信號的信號質量都有著密切關系。

我們通常認為:“T0點到負載的布線延時如果小于上升時間的一半時就不會對信號質量有明顯的影響,如果T0點到負載的布線延時大于信號上升時間的一半時就會在信號邊沿產生明顯的回溝或者臺階。” 這只是一個經驗法則不一定很精確但卻可以幫助我們快速地發現問題。

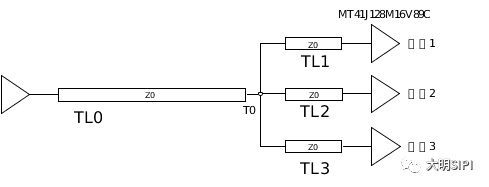

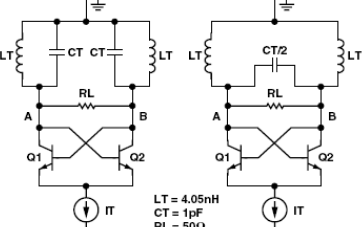

為了驗證這一結論我們在ADS中搭建DDR3地址信號的仿真電路進行分析。驅動端使用TI的C6678處理器的DDR3接口地址信號buffer,負載使用美光的DDR3存儲器。查看6678的IBIS模型可知其地址信號輸出上升下降時間均為260ps左右,輸出阻抗40ohm。仿真對比兩種情況:(1)設置TL0=2000mil,TL1~TL3長度為1000mil、延時170ps大于上升時間的一半;(2)TL0=2500mil,TL1~TL3長度為500mil、延時85ps小于上升時間的一半。

圖1.800Mbps

(1)上圖所示紅色點虛線的波形,由于TL1TL3的延時大于信號上升時間一半導致在負載端的接收波形上升下降邊都存在一個很小的回溝,當然這個回溝也會隨著TL1TL3的布線延時、負載的個數的增大而增大;

(2)藍色實線波形,TL1~TL3的延時小于信號上升時間一半,負載端的接收波形邊沿單調。

紅色虛線回溝的產生顯然是和源端阻抗是否匹配沒有太大的關系的,是由于負載和分支點之間的反射導致。對于數據信號在時序余量充足的情況下,很小的回溝或者臺階影響不大;但是如果是時鐘信號就要考慮如何消除回溝了。如果由于受布局等因素的限制無法減小分支布線延時,對于單端信號我們可以通過添加戴維南端接來解決這一問題。

標準的戴維南匹配應該是接在拓撲的最末端但對于遠端簇拓撲我們也只能添加在分支點T0位置,這就可能導致戴維南匹配起不到預期的效果;

對于差分信號可以考慮在每個負載端都在兩根差分線間加跨接電阻,但此時所有跨接電阻的阻值都相當于并聯在一起,會使信號的幅度明顯減小。也可以只在分支點處加一個跨接電阻,阻值需要通過仿真確定。

最關鍵的一點需要我們記住,就是時鐘信號不到萬不得以不要驅動兩個以上的負載,對于高速信號的多負載結構消除回溝和臺階需要付出的代價會非常大。由于PCB板以及系統工作中存在太多的不可控因素,無論采用何種方式的匹配都無法完全規避風險。

遠端簇拓撲在比較低速的DDR2等總線的設計中有一些應用。當然這需要一定的約束條件,比如說需要考慮:

(1)驅動器的驅動能力;

(2)分支點到負載的布線長度等條件同時也會受到芯片布局的限制;

(3)負載的個數。需要注意負載個數太多會導致分支點處的阻抗突變非常大,同時也可能會導致布線層數的增加使PCB成本上升。

如果負載的個數增加導致遠端簇拓撲無法滿足要求,我們就需要考慮更換拓撲方式樹型拓撲是一個很好的選擇被廣泛應用于多負載的DDR、DDR2以及DIMM條的設計中。

-

處理器

+關注

關注

68文章

19785瀏覽量

233323 -

驅動器

+關注

關注

54文章

8605瀏覽量

148909 -

DDR3

+關注

關注

2文章

282瀏覽量

42908 -

仿真器

+關注

關注

14文章

1033瀏覽量

84873 -

CMOS電平

+關注

關注

0文章

20瀏覽量

7355

發布評論請先 登錄

開關電源拓撲結構介紹

不同的充電拓撲結構介紹

BOOST電路拓撲結構介紹

ddr3菊花鏈拓撲結構是什么

介紹一種負載比較集中時采用的拓撲結構—遠端簇拓撲

介紹一種負載比較集中時采用的拓撲結構—遠端簇拓撲

評論