本文轉(zhuǎn)自公眾號(hào),歡迎關(guān)注關(guān)于

RISC-V指令異常調(diào)試實(shí)例 (qq.com)

前言

本文以一個(gè)簡(jiǎn)單的實(shí)例介紹RISC-V指令異常的調(diào)試過(guò)程,思路都是一樣的,遇到其他情況時(shí)分析過(guò)程也類似。

相關(guān)內(nèi)容參考《riscv-privileged-20211203.pdf》

過(guò)程

現(xiàn)象是程序執(zhí)行后進(jìn)入了異常中斷,可以通過(guò)GDB的bt命令看到

#12 0x02002e9c in exception () at src/lib/riscv/src/exception.c:55

#13 0x02002b40 in is_exception ()

Backtrace stopped: frame did not save the PC

(gdb)

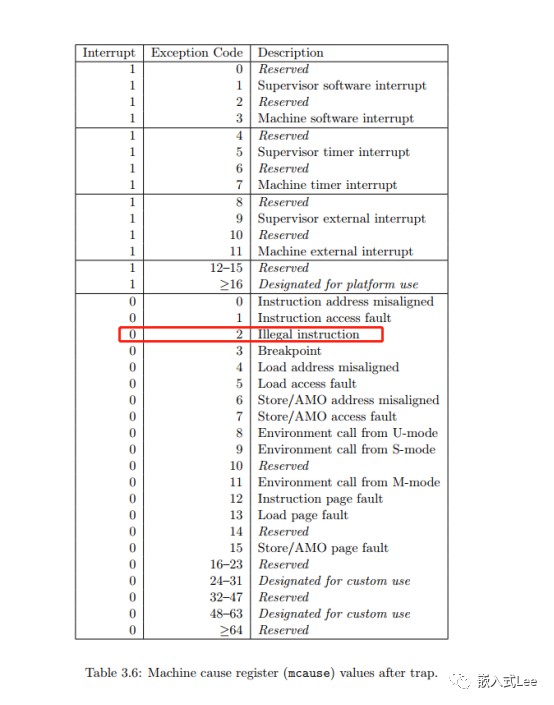

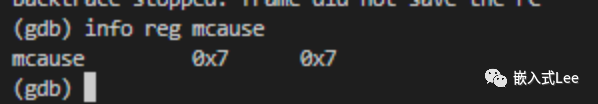

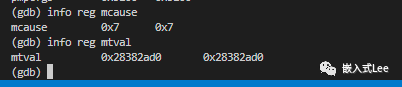

既然是進(jìn)入了異常中斷,那么就需要確認(rèn)到底是什么異常,

這可以通過(guò)mcause寄存器查看

(gdb) info reg mcause

mcause 0x2 0x2

(gdb)

可以看到是非法指令異常

那么我們就搜索文檔的Illegal instruction可以查看到所有可能導(dǎo)致Illegal instruction的原因。

我們搜到以下信息,即mtval寄存器保存了異常指令,mepc指向了異常指令

可以看到mepc的內(nèi)容是0,那么猜測(cè)應(yīng)該是函數(shù)指針未初始化直接調(diào)用導(dǎo)致的

(gdb) info reg mtval

mtval 0x0 0x0

(gdb) info reg mepc

mepc 0x0 0x0

(gdb)

到這里基本就確認(rèn)了方向了,可以重點(diǎn)看哪些地方有函數(shù)指針,或者逐步注釋函數(shù),或者逐步斷點(diǎn)定位即可。

這里很快就確認(rèn)了是

是如下代碼導(dǎo)致

int xxx_ioctl(unsigned int dev_id, unsigned int cmd, void *data)

{

if (dev_id >= xxx_drv.dev_num)

return -1;

return xxx_drv.ops.ioctl(&(xxx_drv.dev[dev_id]), cmd, data);

}

查看函數(shù)指針正好是0

(gdb) p xxx_drv.ops.ioctl

$1 = (int (*)(struct xxx_dev_s *, unsigned int, void *)) 0x0

(gdb)

回溯代碼確認(rèn)了是某個(gè)外設(shè)沒有初始化成功則這個(gè)回調(diào)函數(shù)沒有初始化。原因就定位了。

總結(jié)

對(duì)于異常的調(diào)試可以參考手冊(cè)《riscv-privileged-20211203.pdf》,從異常原因入手,逐漸反推,確認(rèn)異常觸發(fā)點(diǎn)然后確定原因。

審核編輯:湯梓紅

-

指令

+關(guān)注

關(guān)注

1文章

614瀏覽量

36197 -

調(diào)試

+關(guān)注

關(guān)注

7文章

603瀏覽量

34494 -

命令

+關(guān)注

關(guān)注

5文章

725瀏覽量

22655 -

RISC-V

+關(guān)注

關(guān)注

46文章

2472瀏覽量

48204

發(fā)布評(píng)論請(qǐng)先 登錄

正式的RISC-V基礎(chǔ)指令集架構(gòu)與特權(quán)架構(gòu)規(guī)范來(lái)了,RISC-V基金會(huì)已正式批準(zhǔn)

RISC-V指令集架構(gòu)特點(diǎn)

RISC-V的Store AMO access fault調(diào)試實(shí)例

【RISC-V開放架構(gòu)設(shè)計(jì)之道|閱讀體驗(yàn)】RISC-V基礎(chǔ)整數(shù)指令集

RISC-V基礎(chǔ)整數(shù)指令集

關(guān)于RISC-V學(xué)習(xí)路線圖推薦

RISC-V指令集概述

RISC-V基礎(chǔ)指令詳解

什么是RISC-V? RISC-V指令具有哪些特點(diǎn)應(yīng)用?

RISC-V 發(fā)展

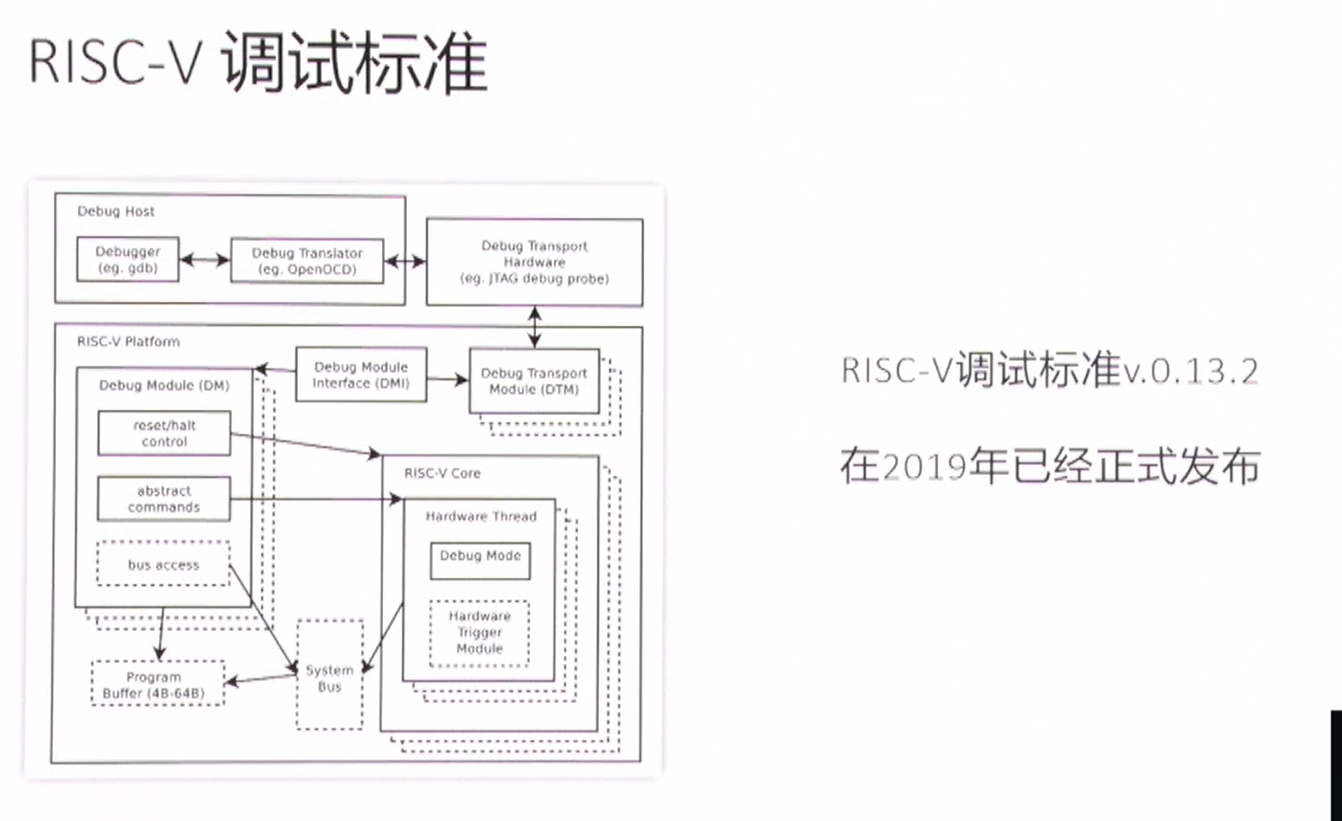

RISC-V的調(diào)試標(biāo)準(zhǔn)及跟蹤技術(shù)

簡(jiǎn)單講講RISC-V指令集CPU的參數(shù)

RISC-V指令異常調(diào)試實(shí)例

RISC-V指令異常調(diào)試實(shí)例

評(píng)論