在這篇博客中,我將展示另一個功能,它使Verdi Protocol Analyzer成為調試內存協議問題和驗證正確系統行為的首選工具。此外,該工具還可用于驗證命令序列器以及 DUT 和內存模型之間的交互。我們今天要看的功能是將交易與相應的信號同步。

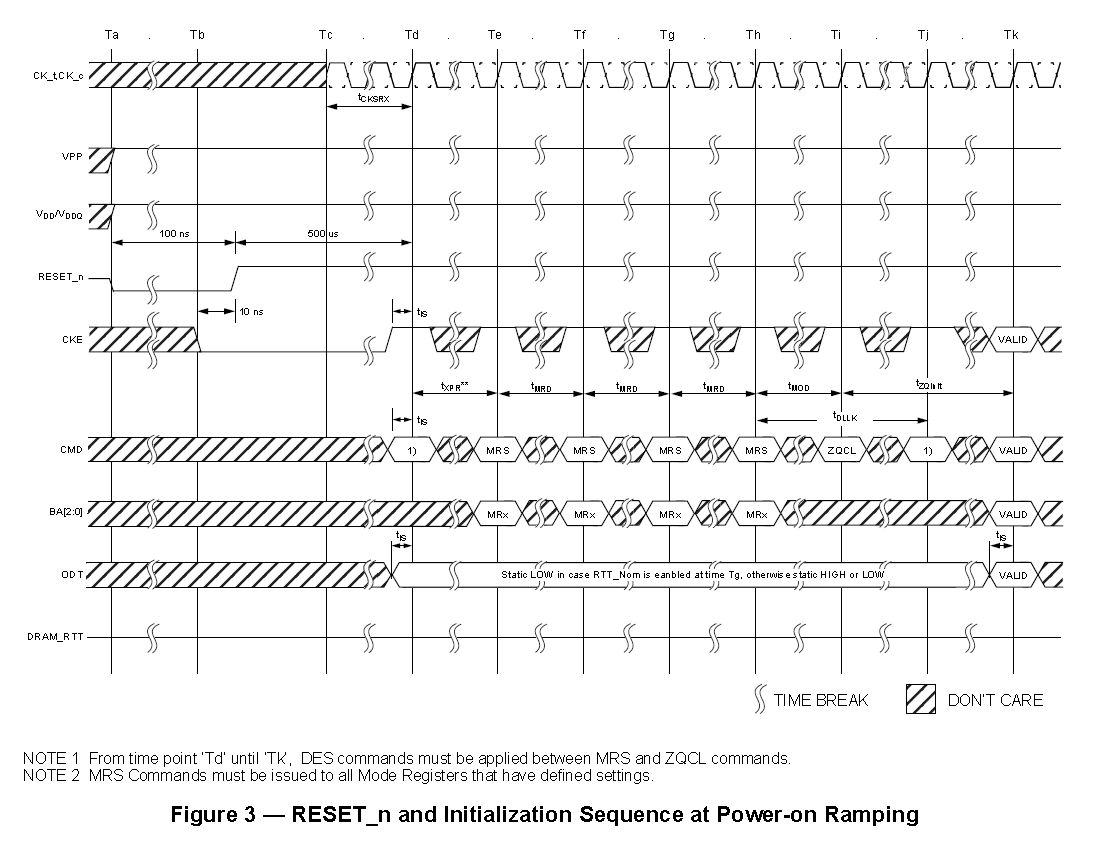

為了演示同步功能,我選擇使用復雜的命令序列來初始化 DDR 內存。上電初始化需要 15 個 DDR 存儲器序列或步驟,如 Jedec 標準 JESD79-4 第 3.3.1 節所列。這些步驟在標準圖3所示的波形中描述,如下所述。

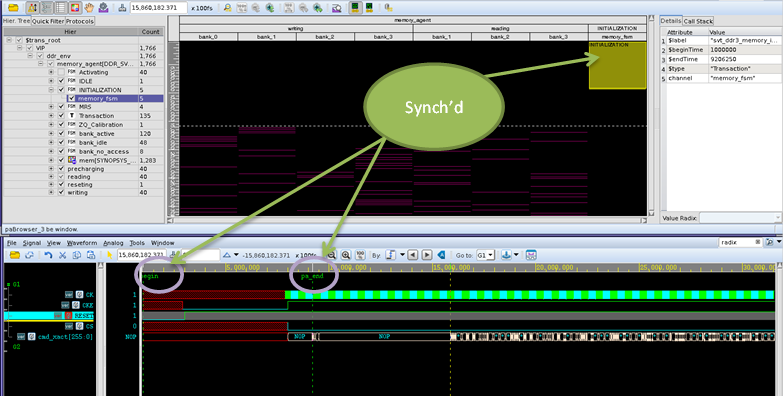

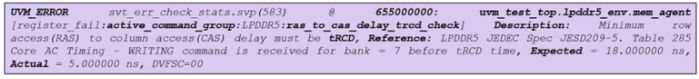

現在讓我們看一下Verdi協議分析器中相同的上電初始化步驟。在這里,與其查看大量擺動信號,不如觀察完成的 15 個步驟作為 1 筆交易。此外,在Verdi中,可以突出顯示初始化事務,并在nWave中交叉引用序列的開始和結束時間。此同步功能縮小了用戶可以只關注初始化步驟的區域,而不會陷入與初始化無關的其他信號和時間戳的泥潭。

以下屏幕截圖對此進行了演示。

同步內存事務和信號

總之,Verdi 協議分析器事務/信號同步功能將調試和驗證時間縮短一半或更多。祝您快速輕松地調試。

審核編輯:郭婷

-

存儲器

+關注

關注

38文章

7632瀏覽量

166380 -

DDR

+關注

關注

11文章

731瀏覽量

66366 -

DUT

+關注

關注

0文章

190瀏覽量

12839

發布評論請先 登錄

物理內存模型的演變

用于快速模型的模型調試器11.21版用戶指南

用于快速模型的模型調試器11.20版用戶指南

分布式對象調試中的事件模型

LogP簡化模型參數估計

MIPS可簡化Android應用開發的先進調試和開發工具已開

Elastos內存管理對軟件調試的支持

java線程內存模型

簡化內存模型的調試

簡化內存模型的調試

評論