PCI-SIG?發(fā)布了PCI Express?規(guī)范PCIe? 6.0的最新修訂版。憑借 64GT/s 原始數(shù)據(jù)速率物理層,可通過 256 通道配置實(shí)現(xiàn)高達(dá) 16 GB/s 的數(shù)據(jù)傳輸。通過此次發(fā)布,PCIe 繼續(xù)滿足行業(yè)對高帶寬和低延遲互連的需求,其潛力可以通過依賴存儲 (NVMe) 和一致性 (CXL) 協(xié)議加以利用。

PCIe 6.0 的帶寬比 PCIe 5.0 翻了一番,這是通過擺脫差分信號并使用成熟的 PAM4 調(diào)制和灰度編碼技術(shù)來實(shí)現(xiàn)的。此外,智能前向糾錯和重放技術(shù)可在鏈路伙伴之間提供低延遲傳輸。

與上一代相比,該規(guī)范繼續(xù)保持與現(xiàn)有設(shè)備發(fā)現(xiàn)和軟件生態(tài)系統(tǒng)的向后兼容性,并在每一層中進(jìn)行了大量改進(jìn)。

大量更改位于數(shù)據(jù)鏈路層中,包括 Flit 序列號、信用流控制和 Flit 結(jié)構(gòu)定義。

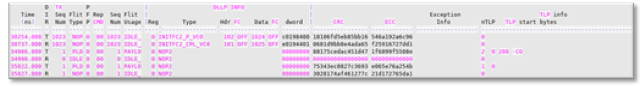

新的 256B Flit 模式,加上高效打包,分配給 TLP、DLLP、CRC 和 ECC。下面的快照捕獲了 Synopsys 驗證 IP 事務(wù)日志中的 Flit 交換事務(wù)。如下所示,交換帶有 NOP 的 Flit 或帶有或不帶有 DLLP 的有效負(fù)載。

引入的鏈路層更改旨在修復(fù)序列號滾動更新和共享/專用積分的問題。為了解決序列號翻轉(zhuǎn)問題,具有有效負(fù)載的 Flit 的序列號遞增;所有其他 Flit 都使用與上一個 Flit 相同的序列號。為了幫助促進(jìn)這一點(diǎn),更新了 Flit 用法以指示有和沒有有效負(fù)載的 Flit。共享積分機(jī)制經(jīng)過調(diào)整,可防止 1 個 VC 主導(dǎo)所有共享積分。在 Flit 模式下,共享積分是“默認(rèn)”,專用積分僅在需要時使用。使用共享/專用配額的 TLP 之間的區(qū)別使用 Flit 模式前綴進(jìn)行管理。

由于灰色編碼和預(yù)編碼規(guī)則的變化,物理層的變化帶來了一定程度的向后不兼容。更新了以 64GT/s 執(zhí)行環(huán)回均衡和以 64GT/s 進(jìn)入合規(guī)性的 LTSSM 規(guī)則。其他 LTSSM 更改包括在 Flit 模式下向恢復(fù)狀態(tài)添加新的狀態(tài)轉(zhuǎn)換,以及對 64GT/s 均衡過程的調(diào)整。

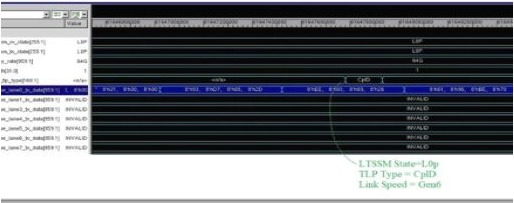

下面是 VIP 波形的快照,說明了在鏈路伙伴之間啟用完全均衡的情況下,速率更改為 PCIe 6.0。

新的節(jié)能狀態(tài) L0p 僅適用于 Flit 模式。L0p 是 LTSSM 的傳統(tǒng) L0 狀態(tài)的一部分,使用配置的鏈路寬度來節(jié)省功耗。下面的快照描述了鏈路寬度配置為 0 通道的 L1p 過渡。即使在這種狀態(tài)下,數(shù)據(jù)傳輸也會繼續(xù)發(fā)生。

PCIe 堆棧關(guān)鍵層的更新也帶來了從 IP 擴(kuò)展到 SoC 再到系統(tǒng)的 PCIe 6.0 設(shè)計的功能驗證方面的一些挑戰(zhàn)。

審核編輯:郭婷

-

soc

+關(guān)注

關(guān)注

38文章

4329瀏覽量

221637 -

crc

+關(guān)注

關(guān)注

0文章

204瀏覽量

29970 -

PCIe

+關(guān)注

關(guān)注

16文章

1322瀏覽量

84661

發(fā)布評論請先 登錄

華為WiMAX業(yè)務(wù)突飛猛進(jìn) 與對手仍有差距

國外PCIE的書籍《pci express system architecture》

PCI Express的基本工作原理

IDT推出新系列PCI Express (PCIe) 系統(tǒng)互

IDT宣布推出PCI Express Gen2 系統(tǒng)互連交換

射頻識別(RFID)半導(dǎo)體市場未來幾年將突飛猛進(jìn)

GaN——如何讓RF功率放大器帶寬和功率突飛猛進(jìn)

AI助力語音識別技術(shù)獲得突飛猛進(jìn)的發(fā)展

全球區(qū)塊鏈?zhǔn)袌龅?023年將實(shí)現(xiàn)突飛猛進(jìn)的增長

Linux5.11開始圍繞PCI Express6.0進(jìn)行早期準(zhǔn)備

PCIe 6.0的新變化與新挑戰(zhàn)

使用多代 PCIe 構(gòu)建高性能互連

PCI Express突飛猛進(jìn):與PCIe 6.0實(shí)現(xiàn)高帶寬互連

PCI Express突飛猛進(jìn):與PCIe 6.0實(shí)現(xiàn)高帶寬互連

評論