復位對數字電路的重要性

我們在數字電路設計時,為了使系統在上電后處于 已知的確定狀態 ,常使用復位電路來實現這一目的。復位是數字邏輯電路所必須的,無論是最簡單的數字時序邏輯門電路,還是復雜的 MCU、ARM、DSP、FPGA 系統,凡是有時序要求的數字邏輯電路系統,都需要復位信號。復位狀態通常是一個電路系統的初始條件,復位信號的有效使電路的狀態進入設計者預先設定的狀態,通常在系統初始化時或者系統死機硬重啟時有效。通常復位信號還與系統的啟動時序密切相關,它與系統各電源域的時序必須滿足一定的先后關系,系統才能正常運行。可見,復位信號在系統中具有十分重要的地位。

最簡單的復位電路分析

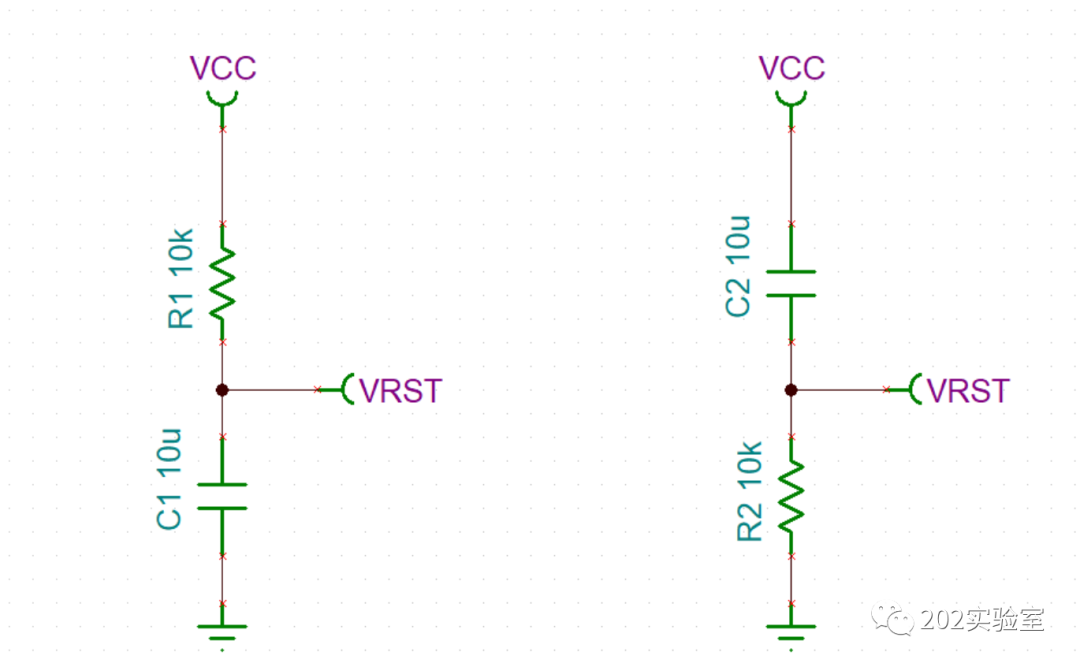

在一些時序和可靠性要求不高的場合,RC 電路是最為常用的復位電路形式。復位信號一般有高有效和低有效兩種形式,對應的電路形式如下圖所示,下圖的左側為低有效形式,而右側為高有效形式。

RC復位電路

下面對左側低有效電路做簡要分析。根據電路的零狀態(電路中所有的源為 0 的狀態)響應特點,當電路上電時,電源電壓 VCC 立即達到穩定值,電容 C1 兩端電壓為 0V;隨后電路通過 R1 對 C1 充電,隨著時間推移,C1 電壓逐漸上升。當 VRST 的電壓達到芯片的 時,芯片復位完成,進入正常工作狀態。

我們把 RC 叫作 RC 電路的時間常數,若令 **\\tau=RC**,根據電路理論,可以推導出 RC 電路中電容兩端電壓(VRST)隨充電時間 t 的變化關系。其公式如下:

可見,隨著時間的推移,VRST 將逐漸接近 VCC,但理論上永遠不能達到 VCC。一般當 時電壓可上升到 0.63VCC; 時,VRST=0.86VCC; 時,VRST=0.95*VCC; 時,VRST=0.98*VCC; 時,VRST=0.99*VCC;工程上一般認為到了 就算充電完成了。

下圖是串聯 RC 電路的仿真結果驗證,其中,R=10Kohm,C=10uF,也即 ,可見,其結果與理論分析完全吻合。

RC充電時間常數

簡單復位電路的改進

上述復位電路雖然簡單,但也存在一定的缺陷,如前所述,其只能用于時序和可靠性要求不高的場合。當電路掉電時,電容 C 兩端電壓接近 VCC,而電源電壓則從 VCC 開始跌落直到 0V。由于芯片的 RST 引腳通常為高阻態,電容 C1 只能通過電阻 R1 放電,放電時電容兩端電壓與時間滿足關系:

對于上述電路,其放電波形及對應的時刻如下如:

RC放電時間常數

可見,放電過程比較緩慢, 時,VRST=0.37*VCC。如果電路在短時間內發生掉電,并立即上電,那么可能存在由于電容兩端的電量沒有放盡,導致此時雖然電源已經重新上電,但由于復位電平不夠低,復位并未可靠起效,引起系統狀態紊亂。

如何通過電路設計改進該問題呢?其實改動也很簡單,由于此時限制放電速度的是充電電阻,因此,只需要在電阻兩端反向并聯一只二極管,此二極管在電路上電時反偏,不影響電容充電。而當電源掉電時,二極管正偏導通,將短接電阻兩端,形成電容的快速放電通路。電路如下所示:

改進的RC復位電路

下面我通過搭建實際電路,測試了沒有放電二極管和增加放電二極管時電路充放電狀態的對比,分別如下圖所示:

RC復位上電對比

RC復位掉電對比

圖中黃色曲線為 VCC 電壓,而紫色曲線為 VRST 電壓,左邊為未加二極管的曲線,右邊為增加后的情況,可見,該二極管對充電過程沒有影響,只對掉電時的 VRST 下降速率有幫助。不過,這里也發現當 VRST 下降到一定值后仍然會比電源下降略慢,這是由于我這里使用的是高速開關二極管 1N4148,該二極管具有較高的正向導通壓降(Max.=1V),因此,會在導通時致使 VRST 與電源間存在壓差,這里最好使用 肖特基二極管 ,能夠保證足夠低的正向壓降,更有利于 VRST 的快速掉電。

使用專用復位芯片

在一些要求比較高的場合,由于 RC 電路的時間常數受器件的離散型和溫度影響較大,復位時間波動較大,RC 電路也不能實現電源軌的監控,因此簡單的 RC 電路并不能滿足電路性能的要求。這時候就需要使用專用的復位芯片來達到更可靠的復位。

一般專用的復位芯片在功能方面都比較全面。比如支持手動復位,支持單/多電源域監控(電源看門狗),支持開漏/推挽輸出,支持復位釋放時間可調(如 LM8365)等。

電壓監控器是監控系統內一個或多個電源軌的器件。電壓監控器可以檢測欠壓事件(電壓低于某個閾值)或過壓事件(電壓超過某個閾值)。根據器件狀態的不同,當受監控的電壓軌電壓低于或高于預設的閾值電壓時,電壓監控器會將信號置為使能、禁用或復位其他器件。

部分電壓監控器可以同時監控欠壓和過壓情況,稱為 窗口檢測器 。電壓監控器旨在確保系統正常上電,防止處理器發生欠壓,同時實時監控系統,避免因電壓軌超出規范而產生性能問題或系統故障。其工作原理通過下圖表征:

電壓監控器原理

帶有電壓監控器功能的復位 IC,能夠保證復位的釋放發生在電源供應正常之后,從而確保可靠復位。同時,若電源出現過壓或跌落故障,芯片還能及時保護處理器,并在電源恢復后執行可靠復位重啟。

為了適應不同的應用,復位 IC 通常還支持可選的高電平有效或低電平有效,推挽或開漏輸出。推挽和開漏指的是輸出驅動的類型,推挽輸出在輸出端使用兩個晶體管。當頂部晶體管導通時,輸出設置為高電平;底部晶體管導通時,輸出設置為低電平。開漏輸出僅使用一個晶體管,通過其將輸出設置為低電平,同時另外使用一個上拉電阻代替頂部晶體管設置高電平輸出。下圖展示了開漏和推挽兩種輸出類型:

開漏和推挽輸出

推挽式輸出的優點是速度快并且功耗低。然而,開漏輸出可以將多個監控器件的輸出連接在一起,形成或/與邏輯輸出配置,方便多電源軌的監控控制。

下圖展示了來自 TI 的 LM3710 的典型應用電路和對應的時序圖,除標準復位功能外,LM3710 還支持手動復位(MR)、電源故障輸入(PFI)、看門狗輸入(WDI)、看門狗定時器和低電壓線路輸出,支持為眾多應用提供所需的靈活性。

上圖中所示的應用電路使用 R1 和 R2 作為與 VIN2 相連的分壓器,以便設置電源故障的復位閾值,實現對第二電源的監控。如果第二電源的電壓降至電源故障復位閾值以下,PFI 引腳將變為低電平,PFO 引腳也隨之降至低電平。

此引腳與 MR 引腳相連,因此將觸發復位。如果在 WDI 引腳上的看門狗窗口內未檢測到任何“喂狗”活動,也會發生復位。WDI 引腳可以與微處理器相連,通過使微處理器發送間歇性脈沖,檢測其是否仍然正常工作。

當 VCC 處的電源電壓降至比復位電壓閾值低 2%左右時,低電壓線路輸出(LLO)引腳將變為低電平。LLO 引腳可以連接微處理器進行檢測。當此引腳進入激活狀態后,發送到微處理器的信號可能觸發其他操作,例如向另一器件發送信號,或以 LED 閃爍等形式向用戶報警。

時序圖所示為監控第二電壓輸入(VIN2)的示例。當與 PFI 引腳相連的 VIN2 變為低電平后,PFO 引腳也將變為低電平,進而導致 MR 引腳降為低電平,隨即觸發復位。使用電源故障和手動復位功能的方法多種多樣,用戶可以根據應用需求自行選擇。

總結

復位電路在數字系統中必不可少,看似簡單的復位電路,其實在設計中也有許多關鍵點需要考慮,有時候更是決定了系統的可靠性與功能。如今很多芯片都內置了基本的復位電路,如 POR(上電復位),并支持一定的可配置。復位電路作為系統的敏感信號,在原理圖設計和 Layout 時都需要格外小心,做好防護,防止受到如 ESD 之類的干擾。

針對最簡單的 RC 復位電路,本文給出了一種通過增加肖特基二極管而實現的高性價比的優化方案,并對電路性能做了實驗分析。如果你的系統需要更高的可靠性,那么,選用專用的復位和監控 IC 將是不錯的選擇,這些芯片通常具備豐富的功能和足夠的靈活性,能夠為系統提供更完整的可靠性保障,當然,這些是需要付出成本的。

-

mcu

+關注

關注

146文章

17824瀏覽量

360243 -

ARM

+關注

關注

134文章

9304瀏覽量

374931 -

數字電路

+關注

關注

193文章

1637瀏覽量

81561 -

復位信號

+關注

關注

0文章

67瀏覽量

6534

發布評論請先 登錄

Excel進行電路統計分析

復位電路設計分析

復位電路設計分析

評論