1.封裝的定義及功能

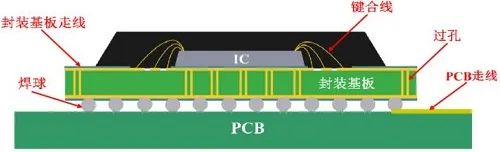

封裝是電路集成技術(shù)的一項(xiàng)關(guān)鍵工藝,指的是將半導(dǎo)體器件通過薄膜技術(shù)連接固定在基板或框架內(nèi),引出端子,再使用特殊的絕緣介質(zhì)固定起來,提供承載結(jié)構(gòu)保護(hù)防止內(nèi)部器件受到破壞,從而使器件發(fā)揮正常功能的工藝技術(shù)。或?qū)⑵涿枋鰹榘丫哂刑囟üδ艿男酒胖迷谝粋€(gè)與其兼容的外部容器中,并為芯片運(yùn)行提供穩(wěn)定的工作環(huán)境。下圖所示,由晶元、封裝基板、鍵合線、焊球以及PCB板等組成為典型封裝結(jié)構(gòu)。

封裝技術(shù)常以四個(gè)不同的層次區(qū)分,如下圖所示。第一層次為零級(jí)封裝,主要是指芯片層次上的互連,包括芯片間以及集成電路元件間的互連。第二層次為一級(jí)封裝,它是將一個(gè)或多個(gè)芯片以合適的形式封裝起來,并將芯片的焊區(qū)和封裝的引腳通過引線鍵合等方式連接。一級(jí)封裝也稱為芯片級(jí)封裝。第三層次為二級(jí)封裝,它是將經(jīng)一級(jí)封裝后的器件連同其它無源器件一同安置在PCB上。二級(jí)封裝也稱為板級(jí)封裝。第四層次為三級(jí)封裝,它是將經(jīng)二級(jí)封裝后的電路板通過疊層、互連插座或柔性電路板等與母板相連,構(gòu)成整機(jī)系統(tǒng)。

優(yōu)良的芯片級(jí)封裝可以減輕后續(xù)板級(jí)封裝甚至整機(jī)封裝的設(shè)計(jì)壓力。因?yàn)樾酒?jí)封裝為處于密封環(huán)境中的芯片提供保護(hù),并保障電源與信號(hào)正常的輸入與輸出。同時(shí),將芯片產(chǎn)生的熱量散發(fā)到外部環(huán)境,確保芯片能夠在所要求的工作條件下穩(wěn)定且可靠地工作。另外封裝還可以實(shí)現(xiàn)電氣連接功能,封裝基板上可以根據(jù)需求埋置各種有源無源器件。芯片經(jīng)封裝后,它的接點(diǎn)連接到封裝外殼的管腳上,這些管腳又經(jīng)過PCB上的導(dǎo)線與其他器件相連接,從而實(shí)現(xiàn)內(nèi)部電路與外部電路的連接。同時(shí),芯片封裝能夠防止大氣中的雜質(zhì)對(duì)其電路腐蝕。

綜上所述,封裝的基本功能歸結(jié)為:電源供給、信號(hào)交流、埋置器件、散熱、芯片保護(hù)和機(jī)械支撐。

2.封裝技術(shù)的發(fā)展及分類

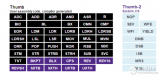

隨著無線通信、消費(fèi)類電子產(chǎn)品以及航空航天電子技術(shù)的飛速發(fā)展,作為現(xiàn)代信息技術(shù)核心的半導(dǎo)體器件需要最大限度地滿足多功能、小型化、高速率及低功耗等要求。自1965年Gordon Moore提出摩爾定律以來,目前微處理器已經(jīng)能集成超過10億個(gè)晶體管。然而,隨著集成電路特征尺寸進(jìn)入納米尺度后,傳統(tǒng)的摩爾定律受到嚴(yán)峻挑戰(zhàn)。半導(dǎo)體工藝受限于光衍射分辨率極限和材料量子隧穿效應(yīng)的影響,難以繼續(xù)縮小晶體管尺寸。因此,如何進(jìn)一步增加單位面積的晶體管數(shù)量,降低單晶體管的功耗并提高工作速度,成為當(dāng)前亟待解決的問題。如下圖所示,在1970s,發(fā)展了直插式的通孔技術(shù),例如雙列直插式封裝技術(shù)(DIP)、插針網(wǎng)格陣列封裝技術(shù)(PGA)。在十九世紀(jì)八十年代,表面貼裝得到發(fā)展,例如小外形封裝(SOP)、方型扁平式封裝技術(shù)(QFP)和帶引線的塑料芯片載體(PLCC);在十九世紀(jì)九十年代,發(fā)展了例如芯片尺寸封裝(CSP)、球柵陣列封裝(BGA)等具有系統(tǒng)級(jí)封裝(SIP)功能的封裝形式;在二十世紀(jì)初,多種SIP技術(shù)在市場(chǎng)的驅(qū)動(dòng)下發(fā)展迅速,例如封裝體疊層技術(shù)(POP)、晶片級(jí)芯片封裝(WL CSP);在2010年以后,隨著集成密度的進(jìn)一步提升,硅通孔(TSV)、扇出式晶圓級(jí)封裝(FO WLP)得到發(fā)展。當(dāng)前及未來的很長(zhǎng)時(shí)間,封裝技術(shù)將是延續(xù)甚至超越摩爾定律的關(guān)鍵技術(shù),也是集成電路(IC)領(lǐng)域一個(gè)強(qiáng)有力的競(jìng)爭(zhēng)市場(chǎng)。

封裝的分類方法并不統(tǒng)一。根據(jù)密封性可以分為氣密性和非氣密性封裝,軍用產(chǎn)品需要在較大溫度范圍內(nèi)使用,一般采用氣密性封裝,而民用產(chǎn)品則多用非氣密性產(chǎn)品。

封裝產(chǎn)品按材料通常分為:塑料封裝、金屬封裝和陶瓷封裝。塑料封裝主要應(yīng)用于商業(yè)產(chǎn)品,具有低成本優(yōu)勢(shì),但在芯片散熱、穩(wěn)定性和氣密性方面相對(duì)較差。金屬封裝和陶瓷封裝多用于航空航天及軍工領(lǐng)域,散熱、氣密性和穩(wěn)定性均比較優(yōu)良。

從器件與母板的連接方式則可以分為通孔插裝技術(shù)(THT)和表面貼裝技術(shù)(SMT)。將器件安置在母板的一面、管腳焊在另一面的技術(shù)稱之為通孔插裝技術(shù)。這種技術(shù)中,每個(gè)管腳需要占掉母板兩面的空間且焊點(diǎn)面積較大,所需安裝空間較大。在表面貼裝封裝中,管腳和器件焊在同一面,能夠支持回流焊等大規(guī)模生產(chǎn)。

目前還有三種被廣泛使用的封裝技術(shù)。

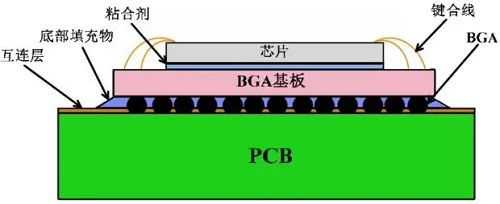

(1)球柵陣列(Ball Grid Array,BGA)封裝

BGA是目前IC封裝熱點(diǎn)技術(shù)之一,它是20世紀(jì)90年代初出現(xiàn)的新型封裝技術(shù)。最先將BGA這項(xiàng)技術(shù)投入使用的是摩托羅拉公司,它出現(xiàn)在移動(dòng)電話的芯片中,隨后康柏公司也將這項(xiàng)技術(shù)用于個(gè)人電腦和工作站上。它基于插針網(wǎng)格陣列(Pin GridArray,PGA)封裝的陣列布置技術(shù),將插入的針腳改換成微球,同時(shí)結(jié)合QFP的回流焊技術(shù)實(shí)現(xiàn)焊接。BGA封裝結(jié)構(gòu)圖如下圖所示。

BGA封裝得到廣泛應(yīng)用的優(yōu)勢(shì)在于以下幾點(diǎn):

1)較高的IO密度。一方面,BGA管腳通過陣列排布,間距為1.27mm、1.0mm、0.8mm、0.5mm等多種類型,加工相對(duì)簡(jiǎn)單,焊接方便,成品率高,成為高密度管腳數(shù)封裝的最佳選擇。另一方面,封裝面積相對(duì)較小,相較于傳統(tǒng)封裝形式面積縮小30%~60%。

2)優(yōu)異的電學(xué)性能。BGA封裝芯片的管腳是一個(gè)個(gè)金屬焊球,相比QFP封裝,寄生電感要小得多。采用這一封裝可以降低互連傳輸損耗,獲得更加優(yōu)異的電性能。

3)可靠性較高。傳統(tǒng)的QFP、PLCC封裝的引線腳均勻地分布在封裝體四周,當(dāng)IО數(shù)越來越多,間距小于0.4mm時(shí),表面貼裝技術(shù)設(shè)備的精度難以滿足要求,引線腳極易變形,從而導(dǎo)致貼裝可靠性降低。

4)良好的散熱性能。BGA的金屬焊球陣列為散熱提供充足的出口,同時(shí)基板的金屬層加大了散熱效率,進(jìn)一步加強(qiáng)了芯片散熱能力,大幅度提高了芯片高速運(yùn)行時(shí)的穩(wěn)定性。

(2)芯片級(jí)(Chip Scale Package,CSP)封裝

CSP封裝和BGA封裝同為20世紀(jì)的產(chǎn)物。90年代后期,日本半導(dǎo)體廠家率先推出芯片面積/封裝面積=1:1.1的CSP封裝結(jié)構(gòu)。事實(shí)上,許多CSP封裝也均采用BGA形式。美國(guó)固態(tài)技術(shù)協(xié)會(huì)對(duì)CSP的定義為封裝尺寸不超過裸片的1.2倍的封裝。由于CSP是在原有封裝BGA技術(shù)上發(fā)展而來,因此,目前普遍把焊球間距小于lmm的 BGA技術(shù)認(rèn)為是CSP封裝。

CSP的主要競(jìng)爭(zhēng)優(yōu)勢(shì)在于:

1)焊球間距極小。在各種相同尺寸的芯片封裝中,可以容納更多的引腳,應(yīng)用在IO數(shù)超過2000的高性能芯片上。

2)電學(xué)性能優(yōu)良。CSP為芯片級(jí)封裝在尺寸上比BGA小了很多,因此其布線更加短小,高頻寄生參數(shù)很小,提升了信號(hào)傳輸質(zhì)量。

3)封裝無需下填充料。CSP封裝工藝中可以不使用下填充料就能夠使晶元與基板粘合緊密,不會(huì)因?yàn)闊崤蛎浂斐蓱?yīng)力,節(jié)省了工序,提高了生產(chǎn)效率。

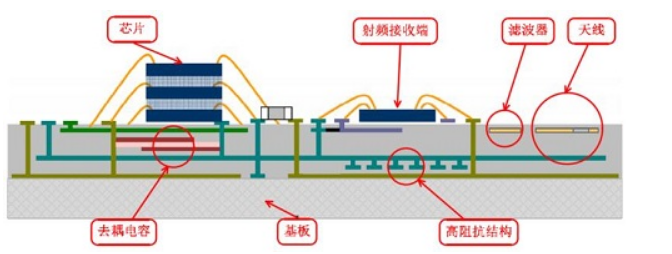

(3)多芯片組件(Multichip Module,MCM)封裝

MCM封裝是SMT后在微電子領(lǐng)域興起并得到迅速發(fā)展的一項(xiàng)引人矚目的新技術(shù)。MCM是將2個(gè)及以上的裸芯片和其它微型元器件互連組裝在同一塊高密度多層互連基板上,形成高密度、高性能、高可靠性的電子組件,如下圖所示。MCM是在印制電路板和表面貼裝技術(shù)的基礎(chǔ)上發(fā)展起來的新一代微電子封裝技術(shù),適應(yīng)于現(xiàn)代集成電路技術(shù)向高密度、高性能、高可靠性、小型化的發(fā)展要求,是實(shí)現(xiàn)系統(tǒng)集成一個(gè)非常重要的手段。

MCM具備以下特點(diǎn):

1)將大型集成電路的裸芯片高密度安裝在同一基板上,省去了單獨(dú)對(duì)芯片的封裝,整體上縮減了組件封裝的尺寸和重量。

2)裸片與基板的面積占比至少達(dá)到20%,由于互連線長(zhǎng)度縮短,提高了信號(hào)的傳輸速率、降低了延遲。

3)能夠?qū)?a href="http://www.asorrir.com/analog/" target="_blank">模擬/數(shù)字電路、天線、微波器件、功率器件以及貼片器件等合理有效的整合在封裝體內(nèi),使之獨(dú)立成為一個(gè)多功能部件,或者成為電路系統(tǒng)中的子系統(tǒng)。

3.倒裝芯片(Flip-Chip)封裝技術(shù)

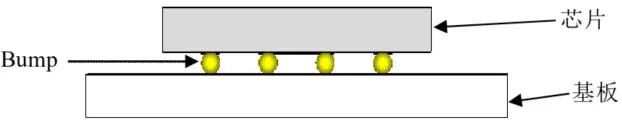

倒裝芯片起源于20世紀(jì)60年代,由IBM率先研發(fā)出來,是將硅片有源區(qū)朝下以倒扣的方式背對(duì)基板通過焊料凸點(diǎn)(簡(jiǎn)稱Bump)與基板進(jìn)行互連,芯片放置方向與傳統(tǒng)封裝有源面朝上相反,故稱倒裝芯片,如下圖所示。

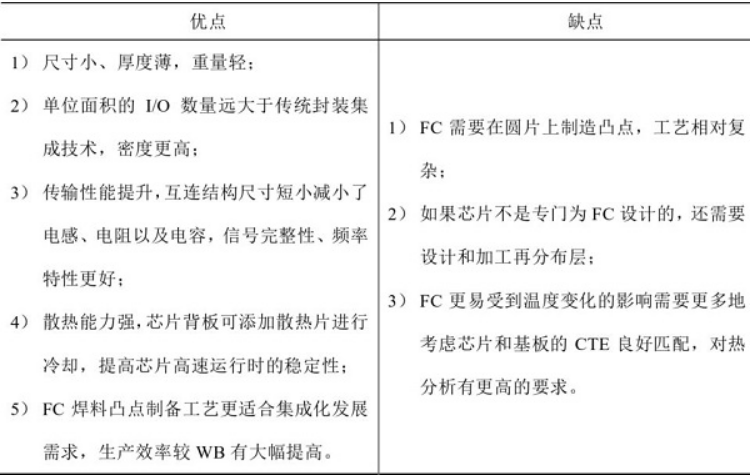

近幾年來,倒裝芯片封裝技術(shù)已被運(yùn)用到各種高端電子器件和高密度封裝領(lǐng)域。倒裝芯片作為高輸入輸出的主流封裝技術(shù),輸入與輸出端可以同時(shí)分布在整個(gè)芯片表面,因而封裝密度更高,信號(hào)處理速度更快。它還可以采用類似SMT來加工,是高密度封裝和系統(tǒng)級(jí)封裝的發(fā)展方向。Flip-Chip封裝具有鮮明的優(yōu)點(diǎn),當(dāng)然也具有其局限性。其優(yōu)點(diǎn)與缺點(diǎn)如下表所示。

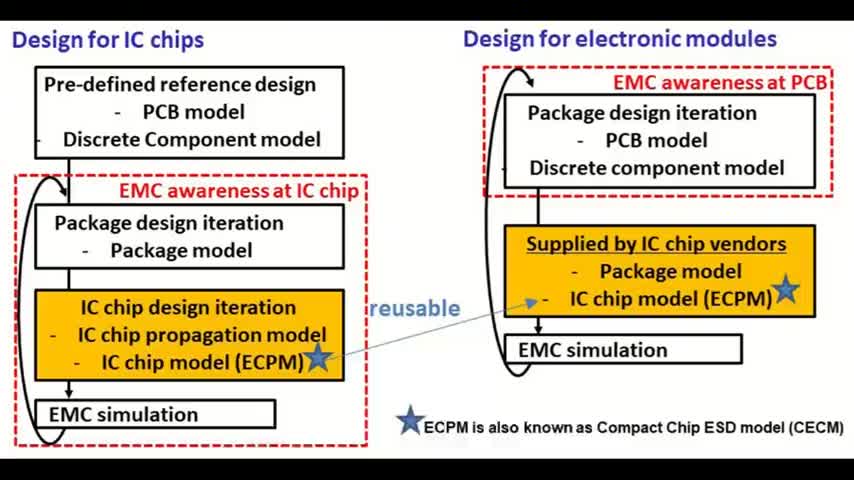

總體而言,數(shù)字計(jì)算和無線通信的快速融合促使半導(dǎo)體技術(shù)朝著更高速率、更高集成度和更低功耗的方向發(fā)展。未來的電子系統(tǒng)需要更寬的頻帶、更高的頻率和更低的功耗來處理海量的數(shù)據(jù)。國(guó)際半導(dǎo)體技術(shù)藍(lán)圖(ITRS)曾在2013年預(yù)測(cè)時(shí)鐘頻率在2022年將上升至20GHz。這使得印刷電路板(Printed Circuit Board,PCB)的設(shè)計(jì)、封裝的設(shè)計(jì)和芯片的設(shè)計(jì)都面臨著嚴(yán)峻的電磁兼容(Electromagnetic Compatibility,EMC)挑戰(zhàn)。如果在封裝或者芯片內(nèi)能夠減少噪聲和電磁干擾,可以極大地減輕后續(xù)PCB級(jí)和整機(jī)的EMC設(shè)計(jì)壓力,從而大幅縮短研發(fā)周期和降低成本。

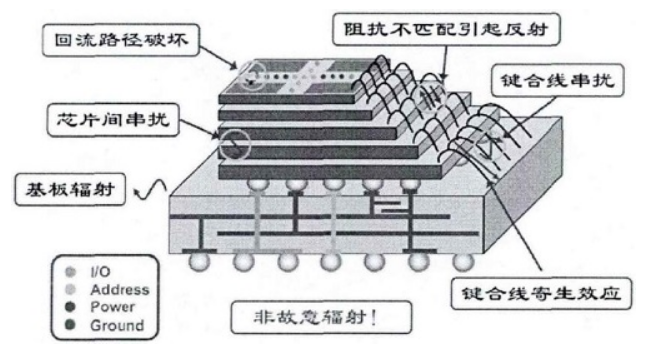

如下圖所示,芯片封裝設(shè)計(jì)中面臨著眾多的EMC問題,主要包括芯片及鍵合線間的串?dāng)_、阻抗不匹配、信號(hào)回流路徑不完整及輻射干擾問題。

4.芯片封裝中EMI的耦合路徑

4.1傳導(dǎo)耦合

傳導(dǎo)耦合是干擾源對(duì)敏感設(shè)備產(chǎn)生干擾的主要路徑之一。干擾源產(chǎn)生的噪聲通過兩者之間的電路連接耦合到敏感設(shè)備上,引發(fā)一系列EMI問題。封裝引線或引腳是噪聲耦合進(jìn)或耦合出IC的主要途徑。例如,同步開關(guān)噪聲(SSN)在電源總線上是一個(gè)波動(dòng)的電壓,如果某個(gè)電源總線的芯片或封裝上去耦合不充分,則所有以該電源總線為參考的引腳都可能會(huì)存在電壓波動(dòng)。IC上的電壓波動(dòng)同時(shí)會(huì)引起連接到芯片上的器件引腳之間產(chǎn)生電壓差,外部的噪聲耦合進(jìn)入芯片內(nèi)部。

4.2電場(chǎng)耦合

電場(chǎng)耦合是由于金屬導(dǎo)體之間的分布電容導(dǎo)致的一種耦合。在電子產(chǎn)品中,當(dāng)金屬物體(如金屬封裝Lid或散熱器)距芯片表面很近時(shí),就會(huì)發(fā)生電場(chǎng)耦合。

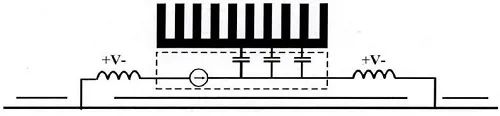

由于IC的集成度日趨升高,芯片電路對(duì)應(yīng)的功率密度日趨變大,芯片因此產(chǎn)生嚴(yán)重的散熱問題。如果不能解決芯片散熱問題,會(huì)導(dǎo)致芯片電路加速老化,甚至使芯片引腳焊接部分的焊錫熔化,影響芯片的正常工作。為了解決芯片散熱問題,一般在芯片上方放置散熱器幫助芯片把熱量帶走并散發(fā)掉,使芯片可以在安全的環(huán)境中運(yùn)轉(zhuǎn)。但散熱器一般是由高電導(dǎo)率的金屬制成,當(dāng)在電路板上放置散熱器時(shí),散熱器會(huì)大幅度增強(qiáng)芯片到外部的能量耦合,引起腔體諧振。

針對(duì)散熱器引起的諧振問題,相關(guān)研究人員給出了不同的解決方案,常見的解決思路包括將散熱器和PCB充分連接即將散熱器接地,以及破壞散熱器/PCB所組成的諧振結(jié)構(gòu)。但這兩種方法在工程實(shí)施上存在困難,且其作用頻率范圍及實(shí)際效果有限。

對(duì)于散熱器所引起的諧振問題,雖然輻射出去的電磁能量的源頭是芯片內(nèi)部的IC,但工程上并不會(huì)將它看做IC自身的輻射。IC與散熱器之間是通過電場(chǎng)耦合的,而IC與PCB之間是通過傳導(dǎo)耦合的,散熱器/PCB是有效的輻射天線。

4.3磁場(chǎng)耦合

當(dāng)高頻電流環(huán)存在于IC封裝的內(nèi)部,引起相應(yīng)磁場(chǎng)分布的改變,噪聲能量就會(huì)通過磁場(chǎng)進(jìn)出IC。芯片內(nèi)部的電流環(huán)磁通量可能會(huì)通過互感在器件外部的電流環(huán)路上產(chǎn)生非期望電壓;同理器件外面的電流環(huán)也可能通過磁場(chǎng)耦合影響芯片內(nèi)部電路的電壓。

4.4輻射場(chǎng)耦合

輻射耦合是指電磁能量通過輻射進(jìn)行空間轉(zhuǎn)移,轉(zhuǎn)移的空間距離一般大于幾個(gè)工作波長(zhǎng)屬于電磁遠(yuǎn)場(chǎng)。電磁遠(yuǎn)場(chǎng)與近場(chǎng)相比,電磁遠(yuǎn)場(chǎng)電磁場(chǎng)強(qiáng)度小,衰減速度快。

找到引起輻射超標(biāo)問題的天線結(jié)構(gòu)是解決EMI輻射問題的首要前提。對(duì)于確定的天線結(jié)構(gòu),一般可以采取以下三種措施進(jìn)行輻射抑制:

1.降低噪聲源的幅度;

2.消除部分的有效天線;

3.切斷噪聲源與天線之間的聯(lián)系。

下圖所示,對(duì)于一個(gè)典型的散熱器結(jié)構(gòu),芯片內(nèi)部的IC是噪聲源,散熱器與PCB 上的電源/地平面構(gòu)成了有效的輻射天線,噪聲源通過電場(chǎng)耦合和傳導(dǎo)耦合與天線聯(lián)系起來,通過輻射場(chǎng)耦合輻射到空間區(qū)域,造成EMI輻射超標(biāo)問題。對(duì)于此類EMI輻射超標(biāo)問題,一般可以通過充分的芯片管腳去耦,從而減小耦合到散熱器上的高頻電流的幅度(降低噪聲源幅度),或減小集成電路與散熱器之間的耦合電容(切斷噪聲源與天線之間的聯(lián)系)來解決。但是這些看起來簡(jiǎn)單而行之有效的方法,在實(shí)際工程運(yùn)用中均存在很多問題。

5.共模EMI輻射基本原理

在高速電路設(shè)計(jì)中,運(yùn)用差分線傳輸高速信號(hào)是解決高頻SI問題的一項(xiàng)重要措施。差分信號(hào)可以有效減小軌道塌陷問題,增益高,可以實(shí)現(xiàn)遠(yuǎn)距離傳輸。但鍵合線、換層信號(hào)過孔等阻抗不可控互連結(jié)構(gòu)會(huì)導(dǎo)致部分差模信號(hào)轉(zhuǎn)化為共模信號(hào),導(dǎo)致EMI輻射超標(biāo)。

5.1差分線基本結(jié)構(gòu)與原理

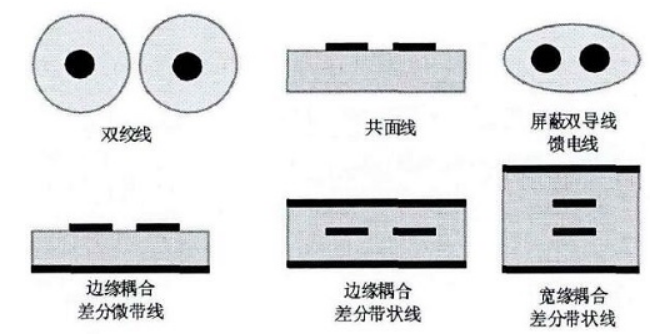

差分對(duì)通常以成對(duì)的傳輸線形式出現(xiàn),其中每條傳輸線都可以看做簡(jiǎn)單的單端線,但兩者之間存在明顯的耦合關(guān)系。因此,類似于單端傳輸線,差分對(duì)也有多種不同的截面形式,如下圖所示。

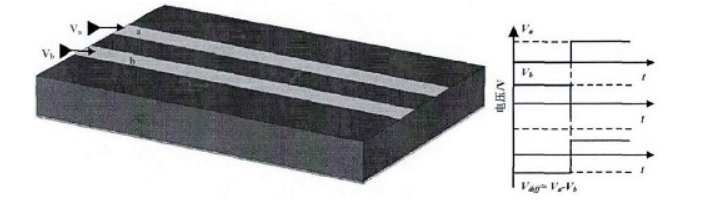

如下圖所示,我們將傳輸線a和b上傳輸?shù)碾妷悍謩e記為Va和Vb,

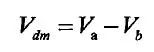

則在接收端接收到的差分信號(hào)為:

由于差分對(duì)在設(shè)計(jì)中難以做到完全對(duì)稱,因此還存在共模信號(hào)。共模信號(hào)一般可以表示為:

在理想的工作場(chǎng)景中,共模信號(hào)的值是不變的,因此不會(huì)引起SI或其他系統(tǒng)問題。但實(shí)際上,電路板上傳輸線設(shè)計(jì)中很小的擾動(dòng)都會(huì)引起共模分量的改變,差分對(duì)中共模分量的改變可能會(huì)導(dǎo)致EMI輻射超標(biāo)。

5.2差分和共模電流的基本輻射型

在實(shí)際芯片封裝設(shè)計(jì)中,鍵合線、換層走線等互連線的擾動(dòng)均可能導(dǎo)致EMI輻射超標(biāo)高頻信號(hào)電流在傳輸線上以回路的形式存在,即信號(hào)電流及其返回電流。在回路中傳輸?shù)碾娏骺梢苑纸鉃椴罘蛛娏骱凸材k娏鲀煞N基本形式。其中幅度相等、方向相反的差分電流產(chǎn)生的場(chǎng)可以抵消;而幅度及方向均相同的共模電流,產(chǎn)生的電場(chǎng)分量則會(huì)相互疊加。以平行雙導(dǎo)線為例,其差分電流和共模電流的電場(chǎng)輻射如下圖所示。

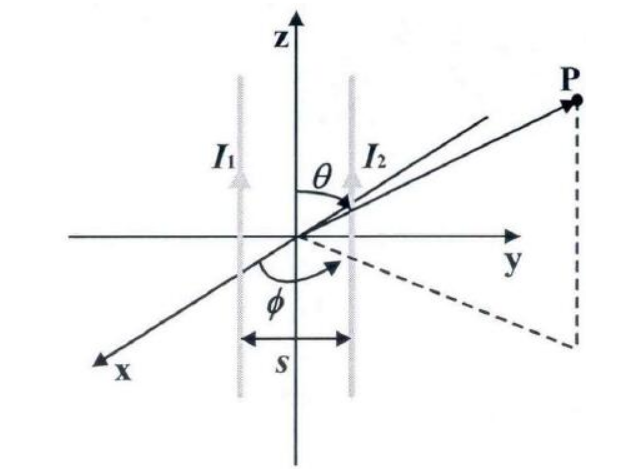

如下圖所示,對(duì)于一對(duì)長(zhǎng)為L(zhǎng),相距s的平行導(dǎo)線,其周圍為均勻的介質(zhì)(ε,μ)。平行雙導(dǎo)可看作一個(gè)二元天線陣列,天線陣列中的每個(gè)元素都可以當(dāng)做偶極子天線。

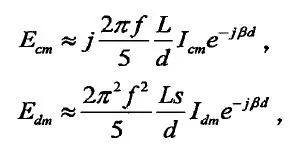

如下式所示,其中β為相位常數(shù),d為雙導(dǎo)線中心距離:

由上式可知,共模電流產(chǎn)生的電場(chǎng)輻射Ecm與導(dǎo)體的長(zhǎng)度L及工作頻率f成正比,與雙導(dǎo)體之間的距離無關(guān)。差分電流產(chǎn)生的輻射電場(chǎng)Edm正比于頻率f的平方和回路面積Ls,反比于d。事實(shí)上,在實(shí)際互連結(jié)構(gòu)中,共模輻射的效率遠(yuǎn)遠(yuǎn)高于差模輻射。因而,抑制共模輻射是解決EMI問題的關(guān)鍵。

-

emi

+關(guān)注

關(guān)注

53文章

3683瀏覽量

130202 -

封裝

+關(guān)注

關(guān)注

128文章

8455瀏覽量

144714 -

無線通信

+關(guān)注

關(guān)注

58文章

4703瀏覽量

144829 -

BGA

+關(guān)注

關(guān)注

5文章

564瀏覽量

48115 -

芯片封裝

+關(guān)注

關(guān)注

11文章

568瀏覽量

31228

原文標(biāo)題:芯片封裝概述及EMI

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

波音客機(jī)概述及特征

電子羅盤概述及應(yīng)用基本介紹

內(nèi)存管理概述及原理

示波器探頭概述及應(yīng)用

單片開關(guān)電源設(shè)計(jì)概述及程序流程圖

芯片封裝概述及EMI

芯片封裝概述及EMI

評(píng)論