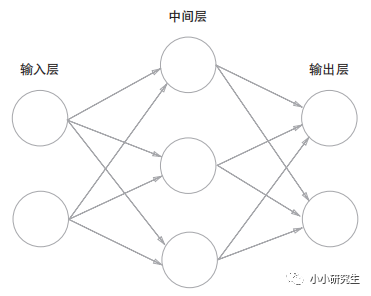

第0層是輸入層,最后一層是輸出層,中間是中間層或隱藏層。上圖中的網(wǎng)絡(luò)有3層神經(jīng)元,實(shí)質(zhì)只有兩層有權(quán)重,因此稱為兩層網(wǎng)絡(luò)。

1、激活函數(shù)

感知器:y=0(b+w1x1+w2x2<=0)或y=1(b+w1x1+w2x2>0)改寫為

y=h(b+w1x1+w2x2),h(x)=0(x<=0)或h(x)=1(x>0)

激活函數(shù)h(x):將輸入信號(hào)的總和轉(zhuǎn)換為輸出信號(hào)的表達(dá)式,決定如何激活輸入信號(hào)的總和。

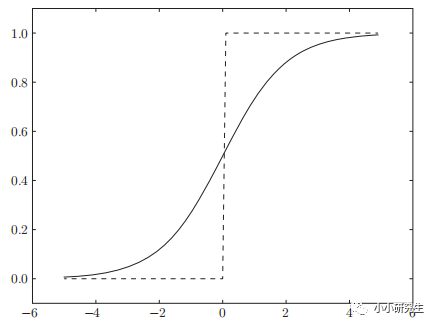

上式中的激活函數(shù)是階躍函數(shù),只能返回0或1,而神經(jīng)網(wǎng)絡(luò)中的激活函數(shù)常用的是sigmoid函數(shù)和ReLU函數(shù)。

1'sigmoid函數(shù)

h(x)=1/(1+exp(-x))

和階躍函數(shù)的對比:sigmoid是平滑的函數(shù),輸出隨輸入發(fā)生連續(xù)的變化,因此可以返回0-1之間的實(shí)數(shù)。

和階躍函數(shù)的相同點(diǎn):輸入小時(shí),輸出接近0,輸入增大時(shí)輸出向1靠近,即當(dāng)輸入信號(hào)為重要信息時(shí),都會(huì)輸出較大值,且兩者輸出都在0-1之間。

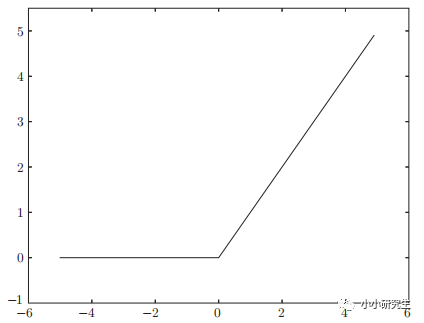

2'ReLU函數(shù)

h(x)=x(x>0);h(x)=0(x<=0)

輸入大于0時(shí)直接輸出,輸入小于0時(shí)輸出0

總結(jié):激活函數(shù)只能為非線性函數(shù),因?yàn)榫€性函數(shù)的問題是多個(gè)隱藏層可以用一個(gè)隱藏層實(shí)現(xiàn)。例如h(x)=cx作為激活函數(shù),y(x)=h(h(h(x)))對應(yīng)的三層神經(jīng)網(wǎng)絡(luò)可以用一層表示y(x)=c^3x。如果要用疊加層則必須使用非線性函數(shù)。

-

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4806瀏覽量

102736 -

網(wǎng)絡(luò)

+關(guān)注

關(guān)注

14文章

7761瀏覽量

90351 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4367瀏覽量

64164 -

感知器

+關(guān)注

關(guān)注

0文章

34瀏覽量

11965 -

深度學(xué)習(xí)

+關(guān)注

關(guān)注

73文章

5554瀏覽量

122468

發(fā)布評(píng)論請先 登錄

單片機(jī)基礎(chǔ)知識(shí)學(xué)習(xí)筆記分享

通信基礎(chǔ)知識(shí)教程

FPGA開發(fā)經(jīng)驗(yàn)與技巧_基礎(chǔ)知識(shí)學(xué)習(xí)篇(1)

ADC【DSP基礎(chǔ)知識(shí)】

使用Eclipse基礎(chǔ)知識(shí)

Verilog_HDL基礎(chǔ)知識(shí)非常好的學(xué)習(xí)教程 (1)

學(xué)習(xí)PLC必備四方面基礎(chǔ)知識(shí)

機(jī)器學(xué)習(xí)的基礎(chǔ)知識(shí)詳細(xì)說明

直流穩(wěn)壓電路的基礎(chǔ)知識(shí)學(xué)習(xí)課件免費(fèi)下載

了解一下機(jī)器學(xué)習(xí)中的基礎(chǔ)知識(shí)

51單片機(jī)學(xué)習(xí) 基礎(chǔ)知識(shí)總結(jié)

單片機(jī)基礎(chǔ)知識(shí)學(xué)習(xí)筆記

深度學(xué)習(xí)基礎(chǔ)知識(shí)(2)

深度學(xué)習(xí)基礎(chǔ)知識(shí)(2)

評(píng)論