在芯片設(shè)計(jì)中,SoC(System on Chip)和NoC(Network on Chip)是兩個(gè)不同的架構(gòu),它們在內(nèi)部通信方式、設(shè)計(jì)理念方面存在著很大的差異。 SoC以緊湊的結(jié)構(gòu)和低功耗著稱,適用于小型和低功耗的應(yīng)用,而NoC則采用分布式通信的方式,能夠?yàn)榇笠?guī)模的系統(tǒng)和高帶寬應(yīng)用提供高效的通信方式。 隨著互聯(lián)網(wǎng)、物聯(lián)網(wǎng)等領(lǐng)域的不斷發(fā)展,NoC架構(gòu)的芯片技術(shù)也將得到更廣泛的應(yīng)用。 本文將探討SoC和NoC架構(gòu)的差異以及各自的優(yōu)勢與挑戰(zhàn)。

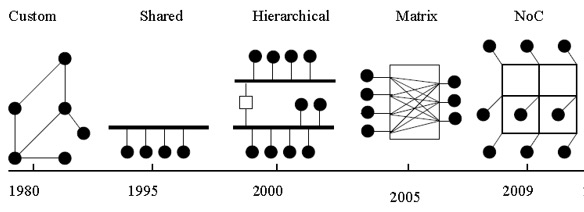

1互連的演變

共享總線:共享總線(如ARM的AMBA總線和IBM的CoreConnect總線)是SoC中常用的通信機(jī)制。 它們支持使用標(biāo)準(zhǔn)接口并允許 IP 重用的模塊化設(shè)計(jì)方法,但隨著系統(tǒng)帶寬需求的擴(kuò)大,共享總線結(jié)構(gòu)成為性能瓶頸。

分層總線:分層總線涉及使用多個(gè)總線或總線段來減輕主總線上的負(fù)載。 這種層次結(jié)構(gòu)允許同一總線段上的模塊之間進(jìn)行本地通信,而不會(huì)導(dǎo)致總線其余部分擁塞。 這種方法的缺點(diǎn)是降低了靈活性和可擴(kuò)展性,并且設(shè)計(jì)過程很復(fù)雜。 連接到總線上的內(nèi)核越多,實(shí)現(xiàn)時(shí)間收斂和服務(wù)質(zhì)量的難度就越大。

總線矩陣:full crossbar系統(tǒng)是片上總線通信的替代方案。 不過,隨著參與系統(tǒng)數(shù)量的增加,線路的復(fù)雜性可能會(huì)超過邏輯部分。 當(dāng)進(jìn)行系統(tǒng)升級時(shí),接口設(shè)計(jì)會(huì)受到影響,所有連接模塊都會(huì)受到影響。 盡管受益于亞微米技術(shù),計(jì)算和存儲(chǔ)使用更小的邏輯單元和內(nèi)存,但通信的能量并沒有按比例減少。 相反,串?dāng)_效應(yīng)、電遷移和互連延遲對時(shí)序收斂會(huì)產(chǎn)生負(fù)面影響。

2000 年代初期,一些技術(shù)人員提出使用預(yù)定義平臺(tái)來實(shí)現(xiàn)芯片中多個(gè)內(nèi)核之間的通信,這種集成交換網(wǎng)絡(luò)能夠滿足未來系統(tǒng)的可重用性、可擴(kuò)展帶寬和低功耗等關(guān)鍵需求,稱為片上網(wǎng)絡(luò)(Network-on-Chip,簡稱NoC)。

2什么是NoC(Network-on-Chip)?

NoC是一種新型的芯片內(nèi)通信結(jié)構(gòu),它采用類似計(jì)算機(jī)網(wǎng)絡(luò)的設(shè)計(jì)思想,將片上系統(tǒng)內(nèi)部的各個(gè)處理器、存儲(chǔ)器、I/O等單元連接起來,形成一個(gè)可重構(gòu)的、高效的、靈活的通信網(wǎng)絡(luò)。

NoC 與Soc

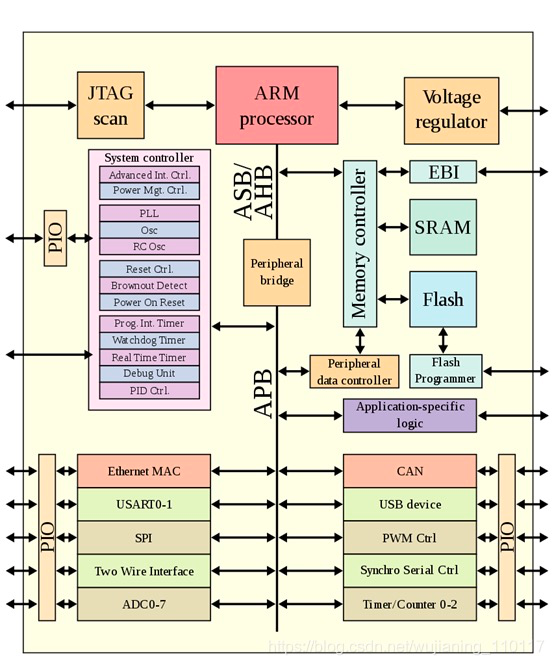

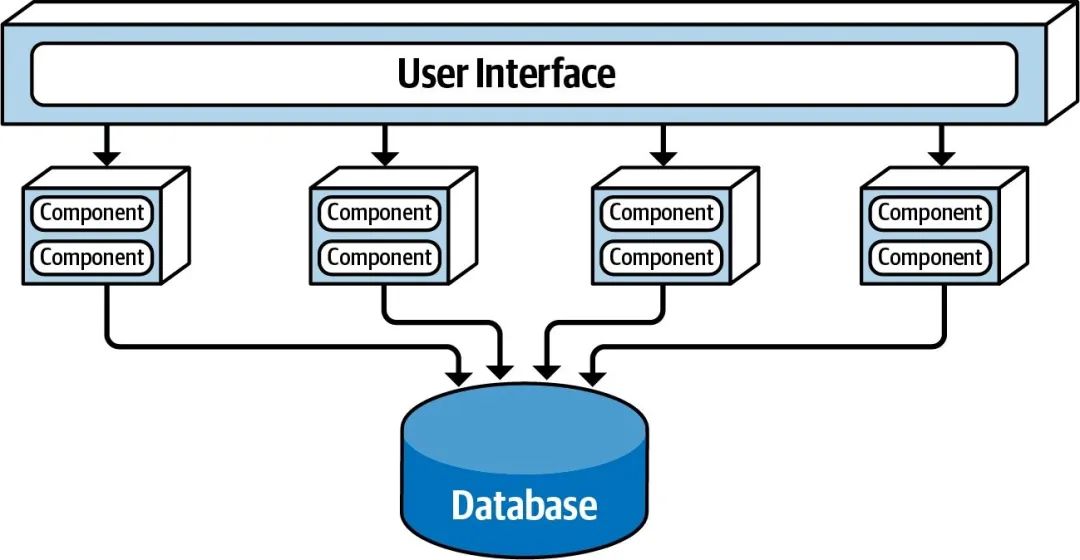

SoC(System on Chip)是一種在單個(gè)芯片上集成多個(gè)不同功能的電子系統(tǒng)的設(shè)計(jì)方法。 在SoC中,不同的組件(如處理器核心、內(nèi)存控制器、圖形處理器等)被集成在同一個(gè)芯片上,以便于更高效、更緊湊的設(shè)計(jì)和制造。

根據(jù)應(yīng)用的不同,SoC 設(shè)計(jì)通常包含存儲(chǔ)設(shè)備、RAM/ROM 內(nèi)存塊、中央處理器 (CPU)、輸入/輸出端口和外圍接口,例如定時(shí)器、內(nèi)部集成電路、通用異步接收/發(fā)送器(UART)、圖形處理單元(GPU)、控制器區(qū)域網(wǎng)絡(luò)(CAN)、串行外設(shè)接口(SPI)等。 此外,根據(jù)需要,還可以包括浮點(diǎn)單元或模擬/數(shù)字信號處理系統(tǒng)。

| 圖:SoC整體架構(gòu)

目前SoC設(shè)計(jì)相對比較成熟。 大部分芯片公司芯片制造都采用SoC架構(gòu)。 然而,隨著商業(yè)應(yīng)用開始不斷追求指令運(yùn)行并存性和預(yù)測性,芯片中集成的核數(shù)目將不斷增多,基于總線架構(gòu)的SoC將逐漸難以不斷增長的計(jì)算需求。 其主要表現(xiàn)為:

可擴(kuò)展性差。

SoC系統(tǒng)設(shè)計(jì)是從系統(tǒng)需求分析開始,確定硬件系統(tǒng)中的模塊。 為了使系統(tǒng)能夠正確工作,SoC中各物理模塊在芯片上的位置是相對固定的。 一旦在物理設(shè)計(jì)完畢后,要進(jìn)行修改,實(shí)際上就有可能是一次重新設(shè)計(jì)的過程。 另一方面,基于總線架構(gòu)的SoC,由于總線架構(gòu)固有的仲裁通信機(jī)制,即同一時(shí)刻只能有一對處理器核心進(jìn)行通信,限制了可以在其上擴(kuò)展的處理器核心的數(shù)量。

平均通信效率低。

SoC中采用基于獨(dú)占機(jī)制的總線架構(gòu),其各個(gè)功能模塊只有在獲得總線控制權(quán)后才能和系統(tǒng)中其他模塊進(jìn)行通信。 從整體來看,一個(gè)模塊取得總線仲裁權(quán)進(jìn)行通信時(shí),系統(tǒng)中的其他模塊必須等待,直到總線空閑。

單一時(shí)鐘同步問題。

總線結(jié)構(gòu)要求全局同步,然而隨著工藝特征尺寸越來越小,工作頻率迅速上升,達(dá)到10GHz以后,連線延時(shí)造成的影響將嚴(yán)重到無法設(shè)計(jì)全局時(shí)鐘樹的成都,而且由于時(shí)鐘網(wǎng)絡(luò)龐大,其功耗將占據(jù)芯片總功耗的大部分。

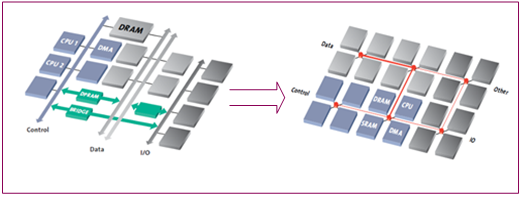

NoC是一種基于網(wǎng)絡(luò)結(jié)構(gòu)的芯片內(nèi)通信方式,它使用專門設(shè)計(jì)的網(wǎng)絡(luò)拓?fù)鋪韺?shí)現(xiàn)不同組件之間的通信。 與傳統(tǒng)的總線結(jié)構(gòu)相比,NoC能夠提供更高的帶寬、更低的延遲和更好的可擴(kuò)展性。

| 圖:從總線結(jié)構(gòu)到網(wǎng)絡(luò)拓?fù)?/p>

NoC具有以下幾個(gè)基本優(yōu)勢:

可擴(kuò)展性:NoC的拓?fù)浣Y(jié)構(gòu)和通信機(jī)制可根據(jù)需要靈活設(shè)計(jì)和配置,可以適應(yīng)不同的處理器核心數(shù)量和布局,同時(shí)支持快速的系統(tǒng)擴(kuò)展。

高性能:NoC具有高帶寬和低延遲的特點(diǎn),可以支持高效的多處理器并行計(jì)算和數(shù)據(jù)交換。

低功耗:由于NoC采用點(diǎn)對點(diǎn)的通信機(jī)制,相比于總線結(jié)構(gòu)具有更少的冗余傳輸,因此能夠降低功耗。

可靠性:NoC具有高度的可靠性和容錯(cuò)能力,由于采用冗余鏈路和路由算法,能夠快速檢測和恢復(fù)故障,從而保證系統(tǒng)的穩(wěn)定性和可靠性。

3NoC架構(gòu)

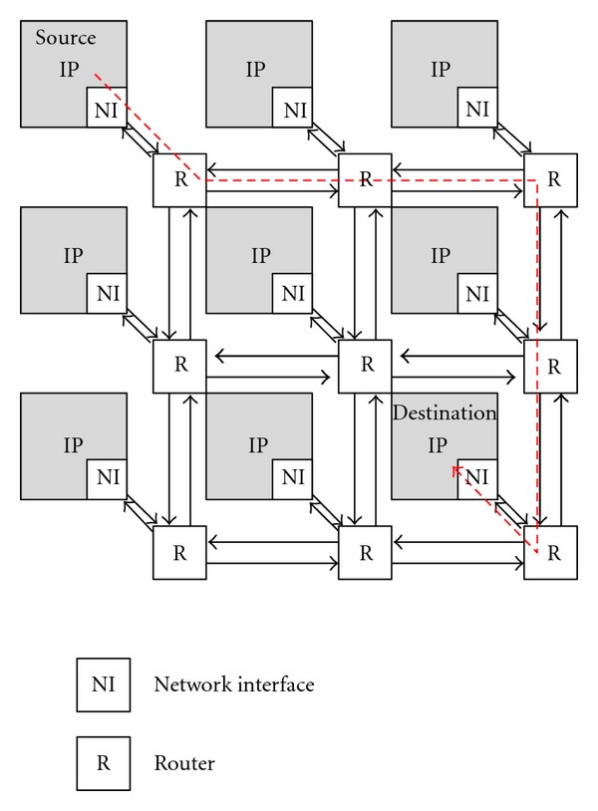

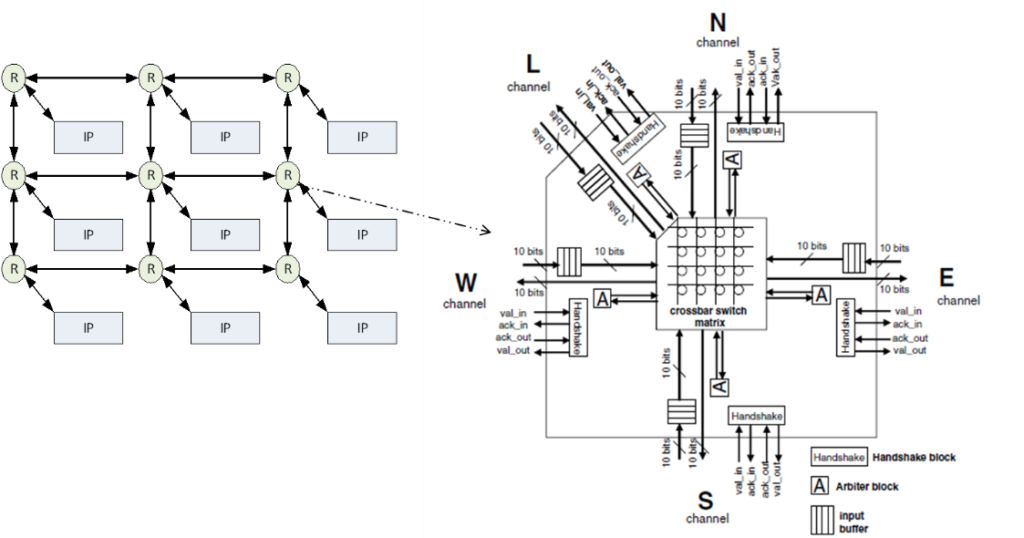

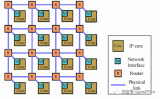

NoC 架構(gòu)主要由三個(gè)模塊組成。

第一個(gè)也是最重要的,是物理連接節(jié)點(diǎn)并實(shí)現(xiàn)通信的鏈路。

第二個(gè)是路由器,實(shí)現(xiàn)通信協(xié)議。

最后一個(gè)是網(wǎng)絡(luò)適配器 (NA) 或網(wǎng)絡(luò)接口 (NI),在 IP 核和網(wǎng)絡(luò)之間建立邏輯連接。

| 圖:網(wǎng)狀拓?fù)渲械牡湫?NoC 架構(gòu)

鏈路:鏈路是路由器之間傳輸數(shù)據(jù)的物理通道,可以是電氣信號線、光纖、無線信號等。 鏈路的帶寬和延遲是影響NoC性能的重要因素,因此鏈路的設(shè)計(jì)需要充分考慮數(shù)據(jù)傳輸?shù)乃俣群涂煽啃浴?/p>

路由器:路由器是NoC的基本組成部分,用于連接芯片內(nèi)部的各個(gè)處理器、存儲(chǔ)器、I/O等單元。 路由器的作用是負(fù)責(zé)接收來自不同節(jié)點(diǎn)的數(shù)據(jù),然后根據(jù)預(yù)先定義的路由算法,將數(shù)據(jù)轉(zhuǎn)發(fā)到目標(biāo)節(jié)點(diǎn)。 路由器通常具有多個(gè)輸入端口和輸出端口,可以同時(shí)處理多條數(shù)據(jù)流。 路由器還包含一個(gè)邏輯塊,實(shí)現(xiàn)流控制策略(路由、仲裁器等),并定義通過NoC移動(dòng)數(shù)據(jù)的總體策略。

| 圖:路由器的通用架構(gòu)

網(wǎng)絡(luò)接口/適配器:這部分負(fù)責(zé)在IP核和網(wǎng)絡(luò)之間建立邏輯連接,因?yàn)槊總€(gè) IP 都可能具有與網(wǎng)絡(luò)相關(guān)的不同接口協(xié)議。 這部分很重要,它實(shí)現(xiàn)了計(jì)算和通信之間的分離,允許相互獨(dú)立地重用核心和通信基礎(chǔ)設(shè)施。

NoC還支持多種通信協(xié)議,包括高速緩存一致性協(xié)議、DMA協(xié)議等,讓它們可以更好地支持多核處理器系統(tǒng)和分布式計(jì)算應(yīng)用。

4NoC的拓?fù)浣Y(jié)構(gòu)

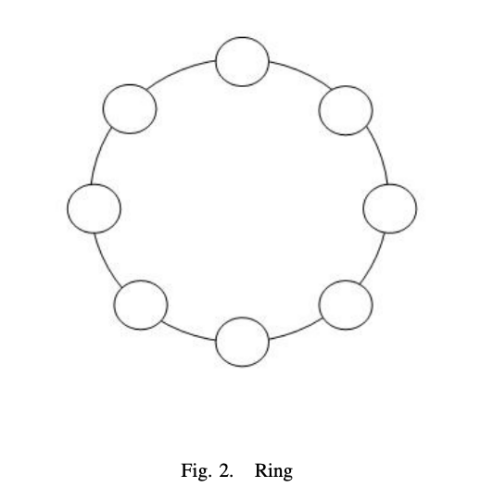

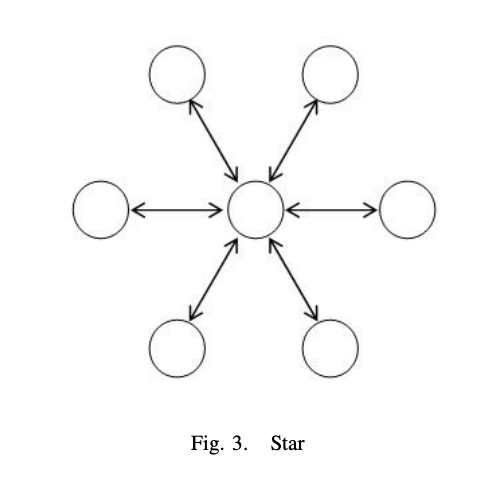

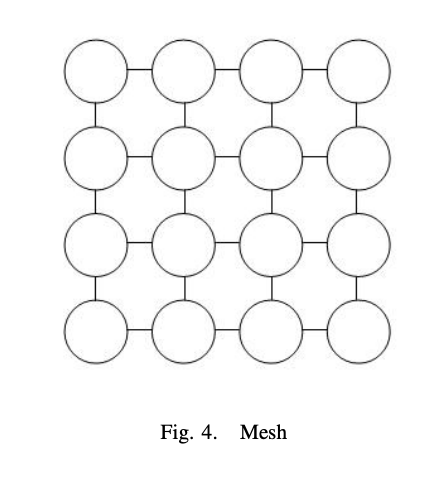

NoC的拓?fù)浣Y(jié)構(gòu)是指路由器之間的連接方式,常見的拓?fù)浣Y(jié)構(gòu)包括環(huán)形,星形,Mesh,樹形,胖樹形,蝴蝶形和環(huán)面等。

環(huán)形:所有節(jié)點(diǎn)都以環(huán)狀方式連接,它的優(yōu)點(diǎn)包括:(1)電纜故障容易定位,故障排除更容易。 (2)安裝比較容易。 局限性包括:(1)網(wǎng)絡(luò)擴(kuò)容可能導(dǎo)致網(wǎng)絡(luò)中斷。 (2)即使是電纜的一個(gè)斷裂也會(huì)破壞整個(gè)網(wǎng)絡(luò)。

星形:星形拓?fù)渲睆叫。骄S距離小,同時(shí)操作簡單,每個(gè)節(jié)點(diǎn)都是隔離的,不受故障節(jié)點(diǎn)的影響。 不過中心節(jié)點(diǎn)是瓶頸,中心節(jié)點(diǎn)故障會(huì)導(dǎo)致整個(gè)網(wǎng)絡(luò)故障。

Mesh:Mesh拓?fù)涫且环N基于網(wǎng)格形式的拓?fù)浣Y(jié)構(gòu),其中每個(gè)節(jié)點(diǎn)都與周圍的節(jié)點(diǎn)相連。 在Mesh結(jié)構(gòu)中,每個(gè)節(jié)點(diǎn)只需要了解相鄰節(jié)點(diǎn)的地址,因此它的路由算法比較簡單。 Mesh結(jié)構(gòu)的優(yōu)點(diǎn)是可以快速地進(jìn)行點(diǎn)到點(diǎn)通信,但是它的鏈路數(shù)目較多,容易出現(xiàn)擁塞。

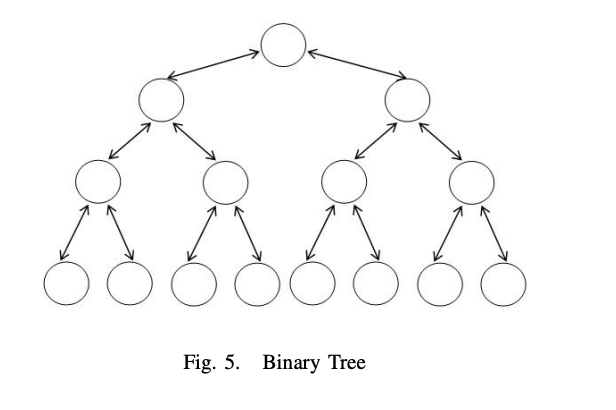

Tree(樹形):樹形拓?fù)溆身敳浚ǜ┕?jié)點(diǎn)和底部(葉)節(jié)點(diǎn)組成,此拓?fù)渲械墓?jié)點(diǎn)可以訪問更廣泛的網(wǎng)絡(luò)資源,并得到多家供應(yīng)商的支持。 但是,它的瓶頸是根節(jié)點(diǎn),根節(jié)點(diǎn)的故障會(huì)導(dǎo)致整個(gè)網(wǎng)絡(luò)的故障。 此外,隨著節(jié)點(diǎn)的增加,網(wǎng)絡(luò)配置會(huì)變得更加復(fù)雜。

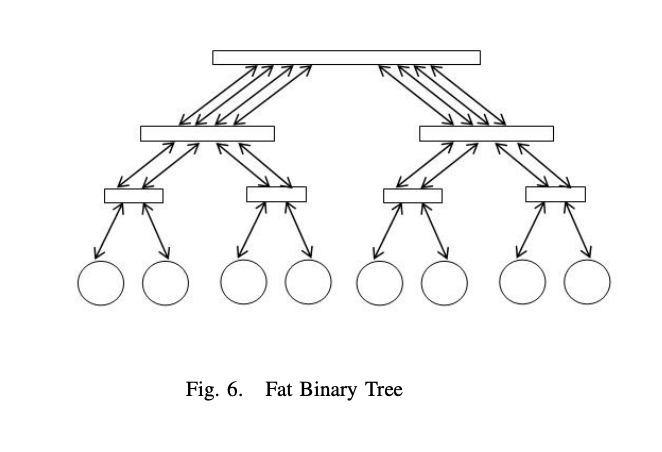

Fat-tree(胖樹):Fat-tree拓?fù)涫且环N基于樹形的拓?fù)浣Y(jié)構(gòu),其中每個(gè)節(jié)點(diǎn)都具有多個(gè)輸入端口和輸出端口。 Fat-tree結(jié)構(gòu)的優(yōu)點(diǎn)是具有較好的可擴(kuò)展性和高帶寬,但是它的路由算法比較復(fù)雜,并且需要更多的硬件資源來實(shí)現(xiàn)。

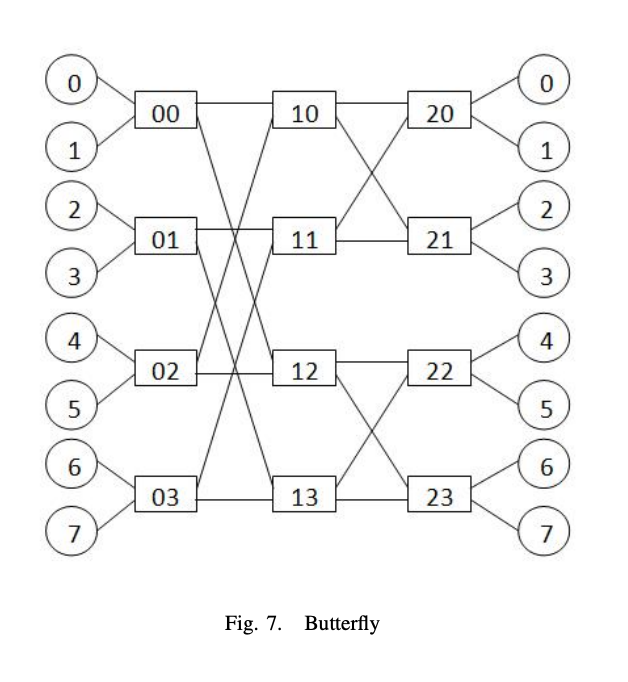

蝴蝶形:基本的蝴蝶架構(gòu)從源節(jié)點(diǎn)到目的節(jié)點(diǎn)只有一條路徑,缺乏路徑多樣性,導(dǎo)致鏈路容錯(cuò)性低,帶寬低。 此外,這種拓?fù)浣Y(jié)構(gòu)通常需要很長的電線,復(fù)雜的電線布局會(huì)導(dǎo)致更多的能源消耗。

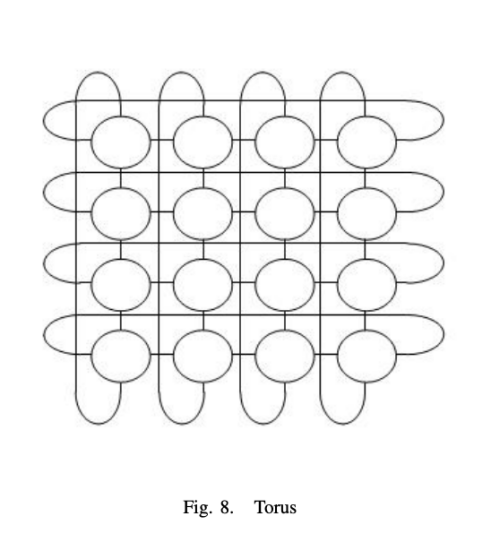

Torus(環(huán)面):Torus拓?fù)浣Y(jié)構(gòu)是一種基于環(huán)形的拓?fù)浣Y(jié)構(gòu),其中每個(gè)節(jié)點(diǎn)都與周圍的節(jié)點(diǎn)相連,并形成一個(gè)環(huán)形結(jié)構(gòu)。 在Torus結(jié)構(gòu)中,每個(gè)節(jié)點(diǎn)可以看作是環(huán)上的一個(gè)點(diǎn),可以通過不同的路徑快速地到達(dá)目標(biāo)節(jié)點(diǎn)。 Torus結(jié)構(gòu)的優(yōu)點(diǎn)是具有良好的擴(kuò)展性和可靠性,但是它的路由算法比Mesh結(jié)構(gòu)要復(fù)雜一些。

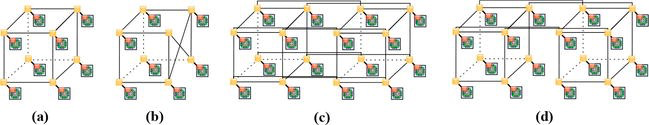

此外還有立方體架構(gòu),它的主要缺點(diǎn)是由于度的限制,其網(wǎng)絡(luò)規(guī)模會(huì)受到限制。 為了解決這個(gè)問題,已經(jīng)提出了各種變體,例如折疊超立方體、雙立方體、交叉立方體、立方體連接循環(huán)、層次立方體和元立方體等等。

不同的拓?fù)浣Y(jié)構(gòu)具有不同的優(yōu)缺點(diǎn),具體應(yīng)用時(shí)需要根據(jù)系統(tǒng)的需求來選擇適合的拓?fù)洹?例如,在需要高帶寬和低延遲的場景中,可以選擇環(huán)面結(jié)構(gòu); 在需要高可擴(kuò)展性和高帶寬的場景中,可以選擇胖樹結(jié)構(gòu)。 同時(shí),NoC的拓?fù)浣Y(jié)構(gòu)可以根據(jù)系統(tǒng)需求進(jìn)行優(yōu)化,還可以進(jìn)行混合結(jié)構(gòu)的設(shè)計(jì),充分利用不同拓?fù)浣Y(jié)構(gòu)的優(yōu)點(diǎn)。

5NoC挑戰(zhàn)

NoC 提供了一個(gè)可擴(kuò)展的模塊化平臺(tái),可提供高效的片上通信,以應(yīng)對 SoC 集成的趨勢,但是仍需要關(guān)注相關(guān)挑戰(zhàn)以進(jìn)一步提高系統(tǒng)性能。

鏈接

為數(shù)據(jù)傳輸選擇并行或串行鏈路一直是 NoC 中的主要問題之一。 一方面,串行鏈路可以大大節(jié)省面積、降低噪聲和減少干擾。 但是,數(shù)據(jù)傳輸需要串行器和解串行器電路。 另一方面,并行鏈路有助于降低功耗,但由于其基于緩沖區(qū)的架構(gòu),它會(huì)占用更多面積。

路由器架構(gòu)

由于底層架構(gòu)必須體積小才能消耗更少的功率,路由協(xié)議設(shè)計(jì)呈現(xiàn)了成本和性能之間的權(quán)衡。 例如,復(fù)雜的路由協(xié)議會(huì)使路由器設(shè)計(jì)變得復(fù)雜。 這樣的話,會(huì)消耗更多的面積和功率。 簡單的路由協(xié)議將是具有成本效益的解決方案,但其在流量路由方面的性能會(huì)相對較低。

面積/空間優(yōu)化

在 NoC 架構(gòu)中,通信通過連接的模塊通過路由器網(wǎng)絡(luò)以長鏈路的方式進(jìn)行。 不同拓?fù)涞逆溌反笮 ?shù)據(jù)包大小、緩沖區(qū)大小、流量/擁塞控制和交換協(xié)議等各種方案不僅需要巨大的 NoC 設(shè)計(jì)空間,而且使開放基準(zhǔn)測試具有挑戰(zhàn)性。 因此,為了提高系統(tǒng)性能,鏈路優(yōu)化勢在必行。 雖然這個(gè)問題可以通過中繼器來解決,但會(huì)消耗更多的芯片面積。 同樣,為了促進(jìn)NoC技術(shù)的廣泛應(yīng)用,需要有效的空間評估和實(shí)施設(shè)計(jì)工具,這些工具可以與當(dāng)前的標(biāo)準(zhǔn)工具無縫集成。

延遲

在 NoC 中,延遲增加是由于 NI 數(shù)據(jù)打包/解包的額外延遲造成的。 它還可以歸因于容錯(cuò)協(xié)議開銷和流量/擁塞控制延遲。 此外,由于競爭和緩沖,路由延遲也會(huì)影響網(wǎng)絡(luò)性能。 因此,為了提高網(wǎng)絡(luò)性能(即滿足嚴(yán)格的延遲限制),需要原生 NoC 支持、低直徑拓?fù)浜透呒壛髁靠刂品椒ā?/p>

功耗泄漏

根據(jù)應(yīng)用的不同,NoC 中的鏈路利用率可能會(huì)有所不同,在某些情況下會(huì)非常低。 為了滿足最壞情況的要求,NoC 旨在保持冗余鏈路并在低鏈路利用率下運(yùn)行。 然而,即使是理想鏈路,由于相關(guān)的復(fù)雜路由邏輯塊和 NI,NoC 也會(huì)消耗相對較多的功率。 因此,為了進(jìn)一步提高其在減少泄漏功耗方面的性能,需要?jiǎng)?chuàng)新的架構(gòu)和電路技術(shù)。

6小 結(jié)

NoC技術(shù)作為新一代芯片設(shè)計(jì)的趨勢,正逐漸得到廣泛的應(yīng)用。 通過采用高效的內(nèi)部通信架構(gòu)和靈活的互聯(lián)方式,NoC可以實(shí)現(xiàn)高性能、低功耗、可擴(kuò)展性和可靠性等優(yōu)勢,為未來的人工智能、物聯(lián)網(wǎng)、自動(dòng)駕駛等新興領(lǐng)域的發(fā)展提供了重要的支撐。 盡管NoC技術(shù)還面臨著一些挑戰(zhàn)和困難,但隨著技術(shù)的不斷發(fā)展和應(yīng)用的推廣,NoC將會(huì)成為未來芯片設(shè)計(jì)的重要方向和趨勢。

審核編輯:湯梓紅

-

ARM

+關(guān)注

關(guān)注

134文章

9287瀏覽量

374662 -

soc

+關(guān)注

關(guān)注

38文章

4322瀏覽量

221519 -

總線

+關(guān)注

關(guān)注

10文章

2941瀏覽量

89303 -

芯片架構(gòu)

+關(guān)注

關(guān)注

1文章

31瀏覽量

14683 -

NoC

+關(guān)注

關(guān)注

0文章

39瀏覽量

11876

原文標(biāo)題:從SoC到NoC :芯片架構(gòu)的演進(jìn)與變革

文章出處:【微信號:SDNLAB,微信公眾號:SDNLAB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

ARM聚焦下一代處理器架構(gòu),或引發(fā)新變革

SoC系統(tǒng)級芯片

NoC是什么?NoC有哪些技術(shù)優(yōu)勢?

SOC與微架構(gòu)微架構(gòu)與SOC有什么區(qū)別?

基于FPGA的NoC多核處理器的設(shè)計(jì)

語音網(wǎng)絡(luò)架構(gòu)的演進(jìn)

系統(tǒng)級芯片(SoC)的技術(shù)演進(jìn)與未來發(fā)展趨勢

芯片廠商從SoC架構(gòu)轉(zhuǎn)向Chiplet

從分層架構(gòu)到微服務(wù)架構(gòu)介紹(五)

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

AMD Versal系列FPGA NoC介紹及實(shí)戰(zhàn)

傳智驛芯聯(lián)手Arteris,利用創(chuàng)新NoC技術(shù)駕馭復(fù)雜SoC設(shè)計(jì)

談存儲(chǔ)芯片的演進(jìn)之路

FPGA領(lǐng)域NoC硬件架構(gòu)下的應(yīng)用

從芯片到系統(tǒng):SOC如何重塑電子產(chǎn)業(yè)

從SoC到NoC:芯片架構(gòu)的演進(jìn)與變革

從SoC到NoC:芯片架構(gòu)的演進(jìn)與變革

評論