邏輯門(mén)(LogicGates)是集成電路設(shè)計(jì)的基本組件,通過(guò)晶體管或MOS管組成的簡(jiǎn)單邏輯門(mén),可以對(duì)輸入的電平(高或低)進(jìn)行一些簡(jiǎn)單的邏輯運(yùn)算處理,而簡(jiǎn)單的邏輯門(mén)可以組合成為更復(fù)雜的邏輯運(yùn)算,是超大規(guī)模電路集成設(shè)計(jì)的基礎(chǔ)。

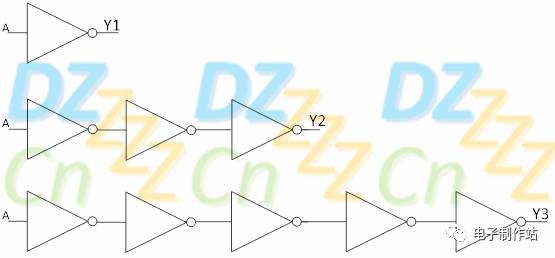

最基本的邏輯門(mén)有三種,即“與”、“或”、“非”,其對(duì)應(yīng)的符號(hào)如下圖所示:

至于它們的邏輯作用這里不再列出了,免得大家說(shuō)編劇我灌水,為了顯得我能勉強(qiáng)高逼格一點(diǎn),我們仔細(xì)看看邏輯門(mén)芯片中有哪些信息值得我們關(guān)注,F(xiàn)ollow me!

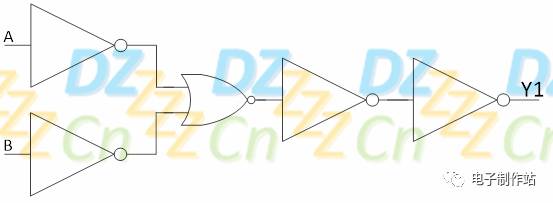

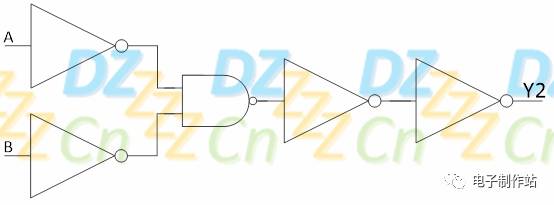

如果你仔細(xì)觀察過(guò)74系列與、或、非邏輯器件數(shù)據(jù)手冊(cè)(datasheet)的邏輯原理圖(Logic Diagram),我們會(huì)發(fā)現(xiàn)上面三個(gè)門(mén)會(huì)是下圖那樣的:

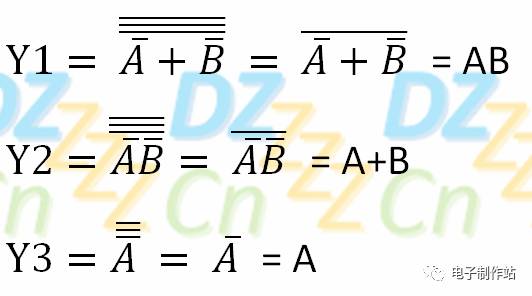

我們利用以前教材上的知識(shí)來(lái)化簡(jiǎn)一下這三個(gè)組合邏輯,如下所示:

果然還是“與”、“或”、“非”邏輯,有心人可能立馬就發(fā)現(xiàn)其中的奧秘:這些邏輯全都被表達(dá)成“與非”、“或非”!原來(lái)以前在學(xué)校做的那些將邏輯表達(dá)式化成“與非”、“或非”的題目在這里就有呀,真是學(xué)以致用呀,我太興奮了,我太有才了,我太…

打住,今天我來(lái)這不是讓你來(lái)做這些簡(jiǎn)單的表達(dá)式化簡(jiǎn),而是想問(wèn)你們兩個(gè)問(wèn)題:

(1)為什么這么簡(jiǎn)單且基本得不能再基本的邏輯運(yùn)算要做得這么復(fù)雜?或者換句話說(shuō),為什么學(xué)校的書(shū)本上有那么多將邏輯表達(dá)式化成“與非”、“或非”的題目?

(2)為什么插入那么多非門(mén)?好像不要錢(qián)似的!

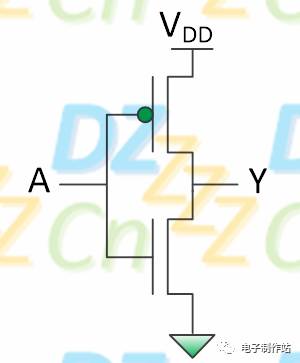

這兩個(gè)問(wèn)題涉及到集成電路的設(shè)計(jì),我們首先來(lái)看看在CMOS集成電路設(shè)計(jì)中是如何將這三個(gè)邏輯設(shè)計(jì)出來(lái)的,如下圖所示的“非門(mén)”邏輯構(gòu)造:

上面帶圓圈的是PMOS晶體管,下面是NMOS晶體管,從開(kāi)關(guān)的角度來(lái)看,PMOS管相當(dāng)于PNP三極管,輸入為“1”時(shí)截止,輸入為“0”時(shí)導(dǎo)通;而NMOS則相當(dāng)于NPN三極管,輸入為“1”時(shí)導(dǎo)通,輸入為“0”時(shí)截止(這個(gè)比喻可能不太合適,但你可以這么去理解這個(gè)開(kāi)關(guān)行為,因?yàn)橄鄬?duì)于MOS管,可能更多人對(duì)三極管更熟悉,如果不是的話,可以忽略這個(gè)比喻)。

當(dāng)輸入為“0”時(shí),下面的NMOS截止,而上面的PMOS導(dǎo)通將輸出拉為高電平,即輸出“1”。當(dāng)輸入為“1”時(shí),上面的PMOS截止,而下面的NMOS導(dǎo)通將輸出拉為低電平,即輸出“0”,很明顯,這就是個(gè)“非門(mén)”邏輯。

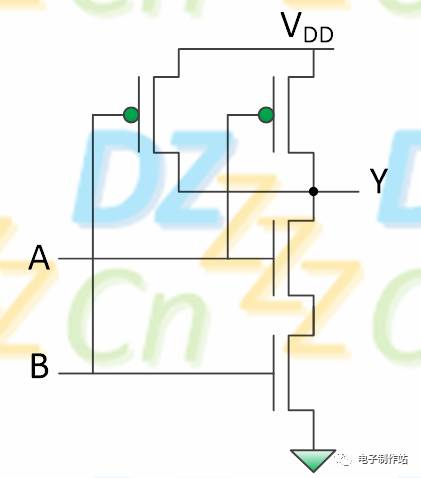

OK,我們?cè)倏纯础芭c非門(mén)”邏輯的結(jié)構(gòu):

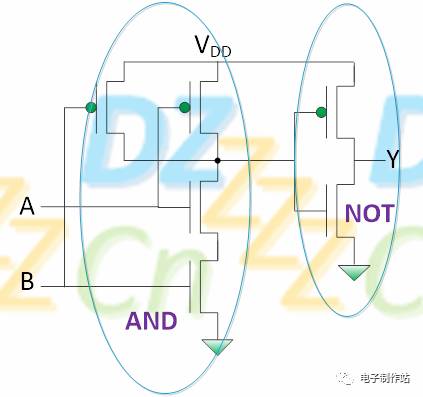

當(dāng)上圖中的任何一個(gè)輸入(A或B)為低時(shí),都將有一只PMOS導(dǎo)通,從而將輸出Y拉高,因此該電路是“與非門(mén)”邏輯,那么“與門(mén)”邏輯就是在“與非門(mén)”后面加一級(jí)“非門(mén)”了,如下圖所示:

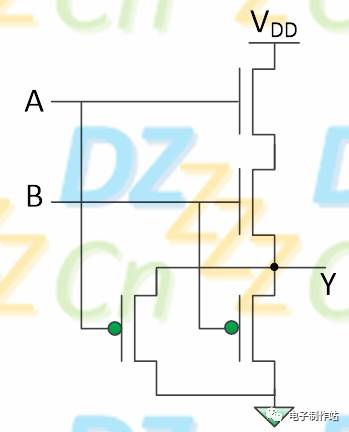

有些人就會(huì)叫起來(lái):編劇你腦殘了,這不是亂蓋嗎?我下面設(shè)計(jì)的電路不是更省邏輯嗎?

你自己看看,只有當(dāng)輸入A與B都為高電平時(shí),輸出Y才被上拉為高電平,而只要有任何一個(gè)輸入為低電平時(shí),輸出Y就被拉為低電平,不是嗎?我太有才了!你們電子制作站的老師水平真是太差了!

但是,對(duì)MOS管有較深理解的人都會(huì)知道,NMOS可以高效傳輸?shù)碗娖剑鳳MOS可以高效傳輸高電平,兩者配合可以達(dá)到軌對(duì)軌輸出,而相反卻不可以(會(huì)有損耗),因此你設(shè)計(jì)的邏輯電路從書(shū)本上看是合格的,但實(shí)際應(yīng)用中不會(huì)有這種電路。

這樣你發(fā)現(xiàn)了什么沒(méi)有?在CMOS集成電路設(shè)計(jì)中,構(gòu)建一個(gè)“與門(mén)”邏輯竟然比“與非門(mén)”邏輯還要多花費(fèi)兩個(gè)MOS晶體管,CMOS門(mén)在本質(zhì)上是反相位的,也就是說(shuō)每一個(gè)基本的邏輯門(mén)都自帶了一個(gè)邏輯非,所以說(shuō),在學(xué)校里老師讓你將復(fù)雜的表達(dá)式化成“與非”或“或非”邏輯,不僅僅是讓你考試拿分的一道題,而是在CMOS集成電路設(shè)計(jì)當(dāng)中,用“與非”、“或門(mén)”這樣的設(shè)計(jì)可以充分地利用CMOS門(mén)本身的“邏輯非”。

這么一個(gè)“與門(mén)”邏輯與“與非門(mén)”邏輯之間的差距雖然僅有兩個(gè)MOS管,但是在成千上萬(wàn)的大規(guī)模集成電路設(shè)計(jì)時(shí)(如奔騰處理器),省下來(lái)的面積就非常可觀了。

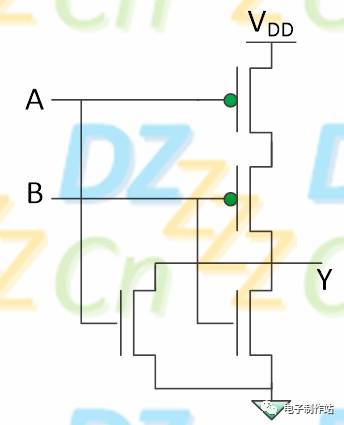

下面是“或非門(mén)”邏輯的結(jié)構(gòu),讀者有興趣可以推導(dǎo)一下

你可能認(rèn)為這只是巧合而已,那你可以看看更復(fù)雜的邏輯芯片的邏輯原理圖,大多數(shù)都是用“與非門(mén)”、“或非門(mén)”、“非門(mén)”,當(dāng)然,有些也不是,畢竟只是上層的邏輯原理框圖,但是底層的CMOS實(shí)現(xiàn)肯定是一樣的

這樣第一個(gè)問(wèn)題就已經(jīng)解答了,那么第二個(gè)問(wèn)題呢?首先要說(shuō)的是:插入的非門(mén)肯定是要花錢(qián)的,但是既然這么做,就一定有道理。有人說(shuō)輸入插入非門(mén)是為了整形,輸出插入非門(mén)是為了增強(qiáng)帶負(fù)載能力,難道“與非門(mén)”或“或非門(mén)”的帶負(fù)載能會(huì)比“非門(mén)”差?都是一樣的構(gòu)造,只有“非門(mén)”可以對(duì)輸入電平進(jìn)行整形?

其實(shí)插入“非門(mén)”的主要目的是為了提升速度,即優(yōu)化邏輯門(mén)的延時(shí)!蝦米?編劇你這次又被我抓到了吧?我插入兩個(gè)非門(mén)就多了兩級(jí)邏輯,不就更慢了嗎?地球人都知道呀!

But,我只想告訴你,這只是一般人的想法(我們是高逼格的人JJ),大多數(shù)人都會(huì)認(rèn)為每一級(jí)邏輯都有一個(gè)“門(mén)延時(shí)”,因此會(huì)通過(guò)計(jì)算總的邏輯級(jí)數(shù)來(lái)計(jì)算總的延時(shí),也就是說(shuō),邏輯級(jí)數(shù)越少的電路就是速度最快的,然而,門(mén)延時(shí)實(shí)際上取決于電氣努力(這個(gè)不好解釋?zhuān)肋@個(gè)名詞就行了),所以采用較少的邏輯級(jí)數(shù)往往會(huì)導(dǎo)致更大的延時(shí)(這有點(diǎn)類(lèi)似時(shí)序邏輯的“流水線”結(jié)構(gòu))。

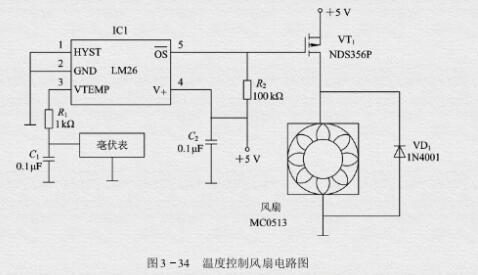

CMOS集成電路設(shè)計(jì)里有一個(gè)“最優(yōu)級(jí)數(shù)”的概念,不是這個(gè)專(zhuān)業(yè)的不需要深究,我們只舉個(gè)最簡(jiǎn)單的例子就可以說(shuō)明白這個(gè)問(wèn)題,如下圖所示:

這三個(gè)“非門(mén)”邏輯當(dāng)中哪個(gè)延時(shí)最呢?你可能認(rèn)為是第一個(gè),但實(shí)際上第二個(gè)方案是延時(shí)最小的,這就解釋了:為什么這些廠家都不要錢(qián)似的插入“非門(mén)”邏輯了吧?插入這么多的“非門(mén)”就是為了獲得更快的速度,然后賣(mài)個(gè)更好的價(jià)錢(qián),正所謂:天下熙熙,皆為利來(lái);天下攘攘,皆為利往,這個(gè)道理永遠(yuǎn)是正確的,在集成電路設(shè)計(jì)里也不例外。

-

集成電路

+關(guān)注

關(guān)注

5416文章

11923瀏覽量

366807 -

邏輯門(mén)

+關(guān)注

關(guān)注

1文章

142瀏覽量

24696 -

電平

+關(guān)注

關(guān)注

5文章

367瀏覽量

40367 -

MOS

+關(guān)注

關(guān)注

32文章

1338瀏覽量

96042

發(fā)布評(píng)論請(qǐng)先 登錄

構(gòu)建自己的邏輯門(mén)學(xué)習(xí)套件

線性代數(shù)相關(guān)的基本知識(shí)

邏輯門(mén)是什么?基礎(chǔ)數(shù)字邏輯門(mén)詳解

關(guān)于邏輯門(mén)的基本知識(shí)

關(guān)于邏輯門(mén)的基本知識(shí)

評(píng)論