首先文章中提出的第一種方法是開環(huán)的主從控制,控制電流源對電容充電產(chǎn)生三角波,然后用峰值監(jiān)測和保持電路來取得三角波的峰值,然后把峰值除以2得到峰值的一半,然而再與主定時電容器的三角波進行比較,從而得到主路delay 180°的地方發(fā)出去置位輔路。

在開環(huán)的主從控制中僅有主路的ZCD參與了周期刷新,輔路只是靠著周期一半的地方發(fā)出PWM,沒有ZCD的參與進去,這樣做的目的是為了最簡單的實現(xiàn)在BCM工作模式中變頻時保證180°的錯相輸出,但是可能會導致輔路進入CCM。

我用仿真軟件簡單的模擬了這個idea,在峰值監(jiān)測和保持中我用的二極管整流對電容充電的方式來抓到主路定時電容上的三角波的峰值,然后在乘以0.5進去,得到主路定時電容三角波的一半,在與主路進行比較得到主路delay 180°的時間信號,去置位輔路的PWM,可見:

輸出:

為了分析開環(huán)主從控制的穩(wěn)定性文章中引入了兩個擾動:一個主路TON的變化另外一個是輔助GS的開通點擾動,兩種情況都導致了開環(huán)的主從開始的時序會亂掉,會一直維持錯誤狀態(tài),當擾動結(jié)束后不能修正這種錯誤,導致輔路會進入CCM。

雖然說交錯的BCM可以使用解耦磁集成的方式來做PFC電感,通過相同的磁性材料和繞線結(jié)構(gòu)來保證主從的電感量處于非常接近的水平,但是這樣并不能排除驅(qū)動、負載變化、輸入變化時產(chǎn)生的擾動,以至于開環(huán)控制的主從并不能較好的應(yīng)用在實際的交錯BCM系統(tǒng)上。

我們再來考慮使用鎖相環(huán)的閉環(huán)控制方法,將主從兩路的的ZCD的之間差控制在180°的時間,論文中提出使用RS觸發(fā)器來抓到兩者之間的時間差的方波,然后用濾波器來將方波低通成直流量,然后通過閉環(huán)控制的方法去調(diào)整輔路的定時器的電壓斜坡的上升速度。

在閉環(huán)調(diào)節(jié)的作用下逐漸達到相位保持在180°,這種方法我之前在這篇文章中有過介紹,是ETH的KOLAR團隊進行交錯TCM的PFC做的實現(xiàn)方法,這個問題就是閉環(huán)調(diào)節(jié)需要時間,在負載動態(tài),開關(guān)周期長度發(fā)生變化時候,重新回到穩(wěn)態(tài)工作點所需要的時間較長,對于PFC這種持續(xù)在變頻的應(yīng)用確實不是很好的方法。

大多數(shù)BCM的PFC控制器內(nèi)部有設(shè)置最長周期時間,它是通過復位定時器來觸發(fā)PWM信號,如當輸出電壓非常接近設(shè)置電壓導致電感兩端沒有足夠的電壓去為電感電流放電,在當前的周期結(jié)束后,ZCD沒有抓到則系統(tǒng)會進到CCM運行,并且系統(tǒng)的工作頻率由內(nèi)部的復位定時器的時間長度來決定。

這種靠鎖相環(huán)去調(diào)節(jié)輔路的導通時間的方法并不能讓系統(tǒng)脫離出CCM模式。另外一個問題是當輔路進入CCM,并且主從相位差小于180°,則閉環(huán)會讓輔路的導通時間增大來增大相差,由于加大了導通時間這樣只會繼續(xù)增加了電感電流,并不能使得系統(tǒng)脫離CCM模式,反而會繼續(xù)惡化系統(tǒng)的工況導致發(fā)生炸雞的情況。

論文提出了一種新的實現(xiàn)方法,利用的是主從兩路相互影響的方法來解決BCM因為擾動進入CCM不能自己退出的問題。下圖是簡化的實現(xiàn)方法,對于每個BCM的開關(guān)周期都進行測量,并把它定為主從兩路的GS開啟到ZCD發(fā)生所持續(xù)的時間,并使用積分器上的電壓斜坡高度來表示開關(guān)周期的長度。

PS信號是兩個相位移動的標志,命名為PS1和PS2,它把主從兩路的開關(guān)周期的長度的一半的時間點的標志信號送給其它的通道。比如把主路上個周期的一半的時間長度作為PS2給到輔路的PWM觸發(fā)器的置位輸入,并在邏輯上與輔路的ZCD2進行AND操作。另外主路也是接受到輔路的上個開關(guān)周期一半的時間信號PS1與自己的ZCD1。

這里最關(guān)鍵是主從兩路的PWM觸發(fā)器的置位輸入是需要PS和ZCD一起置高才能開啟新的PWM輸出,這里是整個BCM變頻交錯實現(xiàn)的關(guān)鍵。另外一個更重要的是這個控制邏輯中存在的輸入信號先后邏輯,比如是PS1先發(fā)生ZCD1后發(fā)生則PWM由ZCD1觸發(fā),對于的PFC通道工作在BCM模式。如果ZCD1先發(fā)生,PS1晚一點產(chǎn)生,在這個時間內(nèi)PWM觸發(fā)器的置位為低,主路PWM會繼續(xù)處于關(guān)閉。并因為電感已經(jīng)ZCD,此時是電感與Coss進諧振的DCM狀。

當PS1和ZCD1都到位后,再開啟主路PWM。不管是主路還是輔路都需要參考相對于的上個周期的長度來進行PWM開關(guān),當ZCD1先發(fā)生而PS1還沒到位,說明輔路在上個開關(guān)周期的長度增長了,為了避免主路因為開關(guān)長度比輔路短一點可能會進入CCM問題,需要主路在DCM等待輔路的上個周期長度一半的標志信號PS1,用來實現(xiàn)兩路的周期長度平衡。

可知當系統(tǒng)處于完美的180deg交錯的穩(wěn)態(tài)運行時,PS1和PS2都分別等于上個開關(guān)周期的一半位置,并且ZCD的發(fā)生位置和PS幾乎同時出現(xiàn),再發(fā)出PWM,也就是下圖中的(n-1)的位置的運行情況。在(n)的位置輔路的導通時間增加了一點時長,PS1(n+1)是輔路上個周期(n)的長度。

在同時主路的ZCD1(n+1)發(fā)生,此時主路的PWM置位所需的兩個信號都已經(jīng)到位分別是PS1(n+1)和ZCD1(n+1),主路發(fā)出PWW,并得到主路上個周期的時間長度的一半PS2(n+1),可以看到PS2(n+1)先于ZCD2(n+1)產(chǎn)生。是因為在(n)時刻,輔路的ON TIME增加了,使得電流過的電流變大所以ZCD發(fā)生所需要的時間要晚于主路的PS2(n+1),所以這里由ZCD2(n+1)來刷新PWM周期,輔路以BCM模式工作。

其實輔路的周期長度已經(jīng)增加了PS1(n+2)的長度是變化了,我們可以看到即使主路的ZCD1(n+2)已經(jīng)產(chǎn)生,但是還需要等到輔路的上個周期長度PS1(n+2)走到,主路的PWM觸發(fā)的置位不能給出,主路的PWM全部OFF,進入DCM狀態(tài)等待PS1(n+2),然后主路發(fā)出PWM開始新的周期,這里主路由于等待了一會輔路的周期長度一半的標志信號PS1(n+2),從ZCD到GS開啟的時間長度也因為DCM等待時間也變長了PS2(n+2)這里就變得與輔路的PS1(n+2)一樣長。

這里輔路也是ZCD2(n+2)先產(chǎn)生,要等待主路的開關(guān)周期長度一半的標志PS2(n+2),也進入了DCM等待一下,然后再開啟的PWM。輔路的上個周期長度一半的標志PS1(n+3)恰好與ZCD1(n+3)同時發(fā)生,說明控制電路把主路和輔路都增加了周期時長,使系統(tǒng)再次達到了BCM的穩(wěn)態(tài)。論文中還分析其他擾動的工作情況,但是都因為主路和輔助相互的影響時間長度來調(diào)整到新的穩(wěn)態(tài),解決了進入CCM的問題,我就沒有放出來。

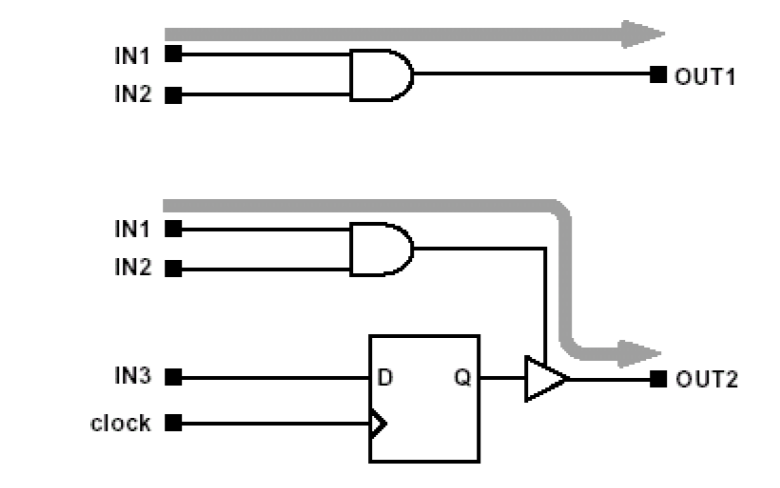

上圖只是為了方便進行原理性的分析,下圖論文給出了具體的邏輯實現(xiàn)電路:兩個相同參數(shù)的積分器和相同的峰值檢波除以2功能,目的是得到在電容上的斜坡電壓的一半的持續(xù)高電平波形,它用來表示主從的上個開關(guān)周期長度的一半的時間長度并送到PWM觸發(fā)器的S引腳的AND門上。它的分析過程可以參考上圖中的擾動分析方法。

運行波形:

測試實現(xiàn):

小結(jié):根據(jù)參考文獻的內(nèi)容學習了一種BCM交錯PFC的時序邏輯的實現(xiàn)方法,并分析了其他實現(xiàn)的優(yōu)缺點,對于理解BCM交錯PFC的控制有非常有益的效用。

-

電容器

+關(guān)注

關(guān)注

64文章

6525瀏覽量

101848 -

二極管

+關(guān)注

關(guān)注

148文章

10038瀏覽量

170267 -

PWM

+關(guān)注

關(guān)注

116文章

5364瀏覽量

217997 -

BCM

+關(guān)注

關(guān)注

12文章

127瀏覽量

53475 -

電容充電

+關(guān)注

關(guān)注

0文章

68瀏覽量

8832

發(fā)布評論請先 登錄

Sequential Logic Design principles--時序邏輯設(shè)計原則

什么是PFC

基于FPGA技術(shù)的RS 232接口的時序邏輯設(shè)計實現(xiàn)

邏輯設(shè)計是什么意思

中規(guī)模集成時序邏輯設(shè)計

時序邏輯設(shè)計原則 (Sequential Logic Des

時序邏輯設(shè)計實踐 (Sequential Logic Des

基于PLD芯片的時序邏輯設(shè)計與實現(xiàn)

FPGA視頻教程之FPGA設(shè)計中時序邏輯設(shè)計要點的詳細資料說明

華為FPGA硬件的靜態(tài)時序分析與邏輯設(shè)計

BCM交錯PFC的時序邏輯設(shè)計的藝術(shù)

BCM交錯PFC的時序邏輯設(shè)計的藝術(shù)

評論