一、上下拉電阻介紹

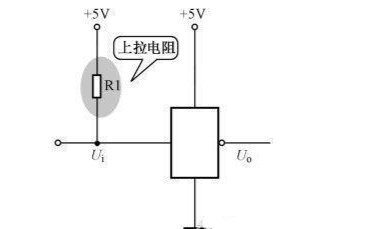

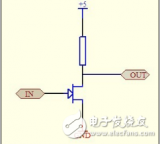

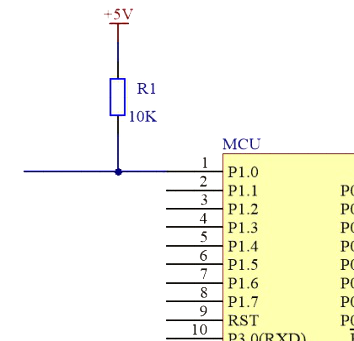

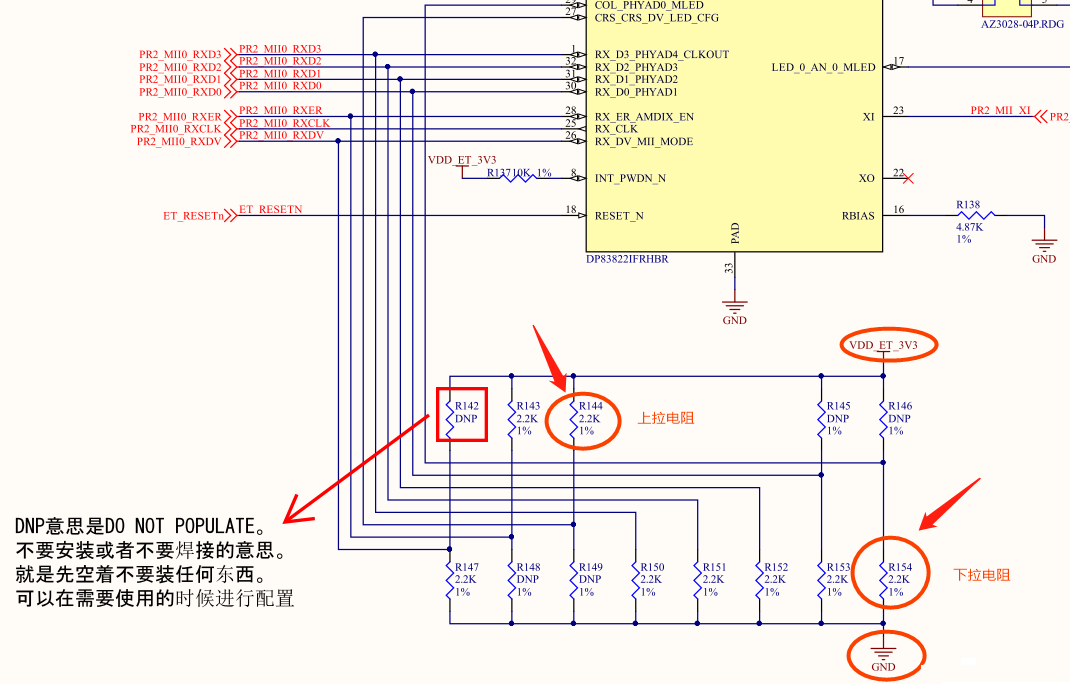

??上拉電阻:將一個(gè)不確定的信號(hào),通過一個(gè)電阻與電源VCC相連,固定在高電平。作用:上拉是對(duì)器件注入電流;灌電流;當(dāng)一個(gè)接有上拉電阻的IO端口設(shè)置為輸入狀態(tài)時(shí),它的常態(tài)為高電平。

??下拉電阻:將一個(gè)不確定的信號(hào),通過一個(gè)電阻與地GND相連,固定在低電平。作用:下拉是從器件輸出電流;拉電流。當(dāng)一個(gè)接有下拉電阻的IO端口設(shè)置為輸入狀態(tài)時(shí),它的常態(tài)為低電平。

??上拉電阻和下拉電阻2者共同的作用是:避免電壓的“懸浮”,造成電路的不穩(wěn)定。

??上拉(Pull Up )或下拉(Pull Down)電阻(兩者統(tǒng)稱為“拉電阻”)最基本的作用是:將狀態(tài)不確定的信號(hào)線通過一個(gè)電阻將其箝位至高電平(上拉)或低電平(下拉)。無(wú)論它的具體用法如何,這個(gè)基本的作用都是相同的,只是在不同應(yīng)用場(chǎng)合中會(huì)對(duì)電阻的阻值要求有所不同,從而也引出了諸多新的概念。

二、上下拉電阻作用

1、提高驅(qū)動(dòng)能力

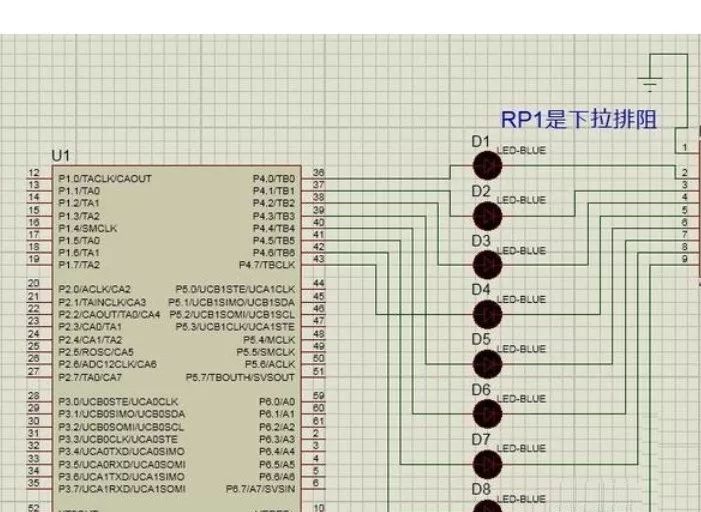

??例如,用單片機(jī)輸出高電平,但由于后續(xù)電路的影響,輸出的高電平不高,就是達(dá)不到VCC,影響電路工作,所以要接上拉電阻。下拉電阻情況相反,讓單片機(jī)引腳輸出低電平,結(jié)果由于后續(xù)電路影響輸出的低電平達(dá)不到GND,所以接個(gè)下拉電阻。

2、鉗位

??上拉就是將不確定的信號(hào)通過一個(gè)電阻鉗位在高電平,電阻同時(shí)起限流作用。下拉同理,也是將不確定的信號(hào)通過一個(gè)電阻鉗位在低電平。在單片機(jī)引腳電平不定的時(shí)候,讓后面有一個(gè)穩(wěn)定的電平。

??例如,如果你連接的單片機(jī)在上電以后,單片機(jī)引腳是輸入引腳而不是輸出引腳,那這時(shí)候的單片機(jī)電平也是不定的,下拉電阻的作用就是如果前面的單片機(jī)引腳電平不定的話,強(qiáng)制讓電平保持在低電平。

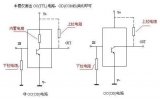

3、 提高輸出的高電平值

??例如,當(dāng)TTL電路驅(qū)動(dòng)CMOS電路時(shí),如果電路輸出的高電平低于CMOS電路的最低高電平(一般為3.5V),這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

4、 其它作用

??1、提高總線的抗電磁干擾能力,管腳懸空就比較容易接受外界的電磁干擾;

??2、長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾,加上、下拉電阻是電阻匹配,有效的抑制反射波干擾。

??3、如果電平用OC(集電極開路,TTL)或OD(漏極開路,CMOS)輸出,那么不用上拉電阻是不能工作的,這個(gè)很容易理解,管子沒有電源就不能輸出高電平了。

三、上下拉電阻比較

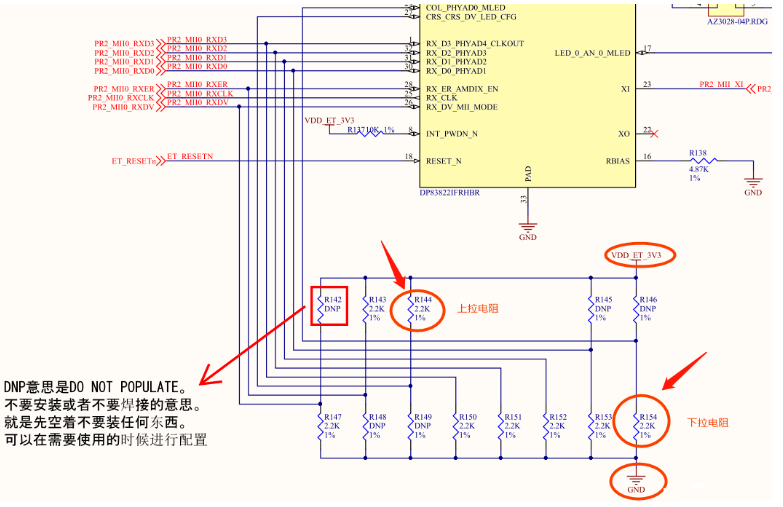

??需要注意的是,上拉電阻太大會(huì)引起輸出電平的延遲。(RC延時(shí))一般CMOS門電路輸出不能懸空,都是接上拉電阻設(shè)定成高電平。

??下拉電阻:和上拉電阻的原理差不多,只是拉到GND去而已。下拉電阻一般用于設(shè)定低電平或者是阻抗匹配。

??上拉是對(duì)器件輸入電流,下拉是輸出電流;上拉用來增大電流,下拉電阻是用來吸收電流。

四、上下拉電阻選用原則

??上拉電阻阻值的選擇原則包括:

??1、從節(jié)約功耗及芯片的灌電流能力考慮應(yīng)當(dāng)足夠大;電阻大,電流小。

??2、從確保足夠的驅(qū)動(dòng)電流考慮應(yīng)當(dāng)足夠小;電阻小,電流大。

??3、對(duì)于高速電路,過大的上拉電阻可能邊沿變平緩。

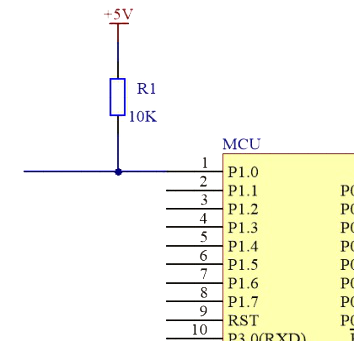

??綜合考慮以上三點(diǎn),通常在1k到10k之間選取。對(duì)下拉電阻也有類似道理。

??4、低功耗狀態(tài) 上拉下拉使用注意;帶上拉或者下拉的IO口,在低功耗狀態(tài),或者配置使用的常態(tài)時(shí),應(yīng)根據(jù)IO口的狀態(tài)進(jìn)行相關(guān)的設(shè)置。

??如果IO口沒有做好處理的話,它就會(huì)在暗地里偷走功耗。一般的IO的內(nèi)部或者外部都會(huì)有上下拉電阻,舉個(gè)例子,假如某個(gè)IO口有個(gè)10KΩ的上拉電阻,把引腳拉到3.3V,然而當(dāng)MCU進(jìn)入低功耗模式的時(shí)候,此IO口被設(shè)置成輸出低電平,根據(jù)歐姆定律,此引腳就會(huì)消耗3.3V/10K=0.33mA的電流,假如有四、五個(gè)這樣的IO口,那么幾個(gè)mA就會(huì)被損耗。所以在進(jìn)入低功耗之前,要逐個(gè)檢查IO口的狀態(tài):

??如果此IO口帶上拉,請(qǐng)?jiān)O(shè)置為高電平輸出或者高阻態(tài)輸入;

??如果此IO口帶下拉,請(qǐng)?jiān)O(shè)置為低電平輸出或者高阻態(tài)輸入;

??總之一句話,不要把上好的電流浪費(fèi)在產(chǎn)生熱量的功能上。

??IO口上拉與下拉電平與IC間的連接造成的相應(yīng)功耗的損失

??IO口的上下拉電阻消耗電流這一因素相對(duì)比較明顯,下邊咱來說一個(gè)不明顯的因素:IO口與外部IC相連時(shí)的電流消耗。假如某個(gè)IO口自帶上拉,而此與IO相連的IC引腳偏偏是自帶下拉的,那么無(wú)論這個(gè)引腳處于什么樣的電平輸出,都不可避免的產(chǎn)生一定的電流消耗。所以凡是遇見這一類的情況,首先需要閱讀外設(shè)IC的手冊(cè),確定好此引腳的的狀態(tài),做到心中有數(shù);然后在控制MCU睡眠之前,設(shè)置好MCU的IO口的上下拉模式及輸入輸出狀態(tài),要保證一絲兒電流都不要被它消耗掉。

文章出處:【微信公眾號(hào):愛搞研究的阿燦】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

電阻

+關(guān)注

關(guān)注

87文章

5605瀏覽量

174247 -

上拉電阻

+關(guān)注

關(guān)注

5文章

366瀏覽量

31039 -

下拉電阻

+關(guān)注

關(guān)注

4文章

152瀏覽量

20800 -

TTL

+關(guān)注

關(guān)注

7文章

530瀏覽量

71404

發(fā)布評(píng)論請(qǐng)先 登錄

什么是上拉電阻和下拉電阻_上拉電阻和下拉電阻的區(qū)別_上拉電阻的作用原理

數(shù)字電路中的上拉電阻和下拉電阻分析

上拉電阻與下拉電阻

上拉電阻和下拉電阻作用、區(qū)別和應(yīng)用

上拉電阻和下拉電阻作用、區(qū)別和應(yīng)用

評(píng)論