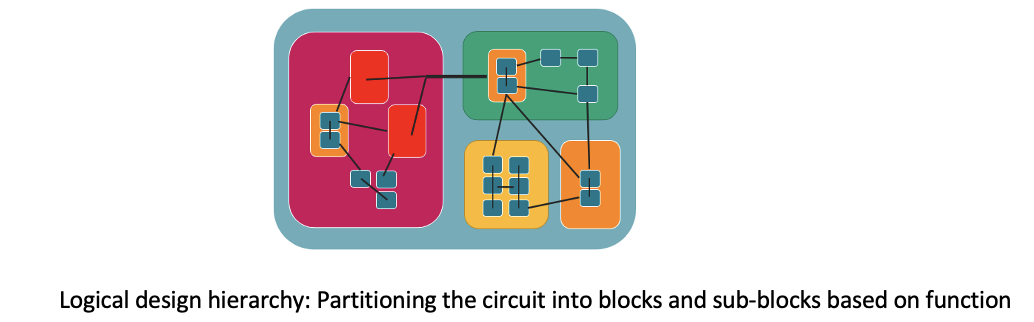

對相似事物進行分區(qū)和分組有助于人類分解一個大問題,以便更容易地理解它。使用命名約定標記組有助于通過目錄輕松訪問所需信息。電子電路設計師已將這一想法擴展到他們管理設計數(shù)據(jù)的方式中。

根據(jù)功能將大型子系統(tǒng)劃分為塊具有相同的目的。電路設計人員在設計的邏輯視圖上進行分區(qū)。在每個塊中再次劃分會導致設計層次結(jié)構的概念,這自電子電路和系統(tǒng)設計的早期就很普遍。設計人員通過識別重復的元素并將它們分組到小的子塊中,使層次結(jié)構受益,這樣子塊只需要構建一次,并且可以多次重復使用。

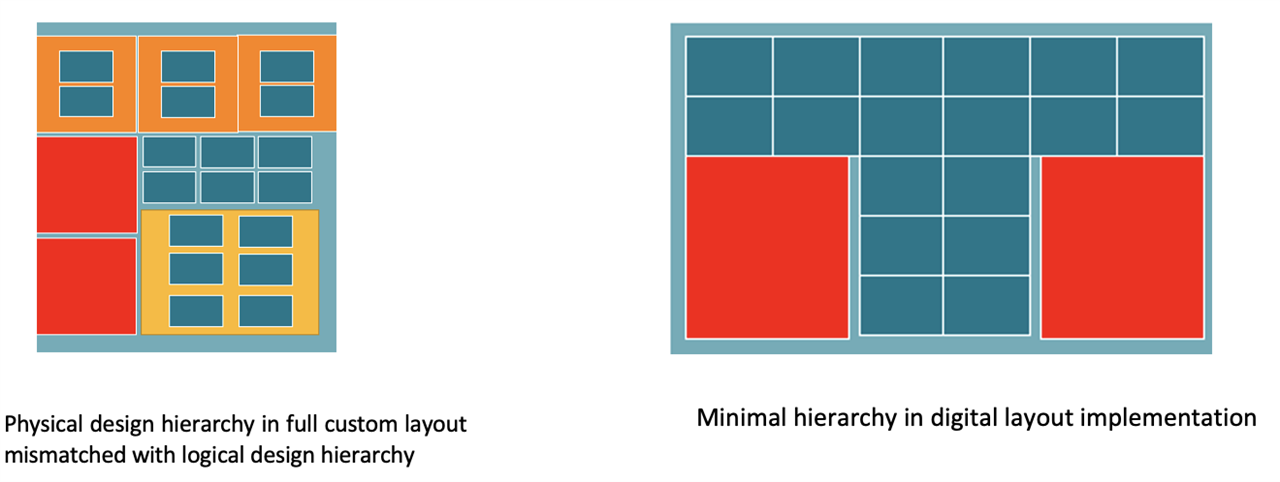

當設計完全手動時,盡可能多地使用設計層次結(jié)構來增加重用量。然而,隨著數(shù)字系統(tǒng)變得越來越大,優(yōu)化設計及其實現(xiàn)的工具變得更加智能,設計層次結(jié)構僅在RTL級別保持相關性,用戶在調(diào)試期間手動構建和理解設計。

層次結(jié)構在布局中不再變得至關重要,因為:

當工具可以快速輕松地重做工作時,不需要重用

當布局沒有層次結(jié)構時,工具具有更大的自由度來創(chuàng)建更好的結(jié)果質(zhì)量

由于在大型數(shù)字設計中無法目視檢查和調(diào)試布局,因此用戶依靠檢查器和自動化來驗證結(jié)果質(zhì)量,這在平面布局上更簡單

是時候在定制設計中采用類似的方法了嗎?

自動放置和路線

自定義塊的增長程度不如他們的數(shù)字表親,但在過去三十年中,實現(xiàn)它們的工具肯定變得更加智能。先進的工藝節(jié)點限制了選擇的自由,增加了設計規(guī)則的復雜性,為基于網(wǎng)格和基于行的布局方法鋪平了道路。通過自動將實例和連線捕捉到網(wǎng)格,可以更快地創(chuàng)建自定義布局。在基于行的布局結(jié)構上自動填充空白空間已變得可行,從而解決了密度規(guī)則合規(guī)性問題,即使對于設備級布局也是如此。

網(wǎng)格布局方法還簡化了自動放置和布線(P&R)問題。自動P&R產(chǎn)生出色的結(jié)果,因為布局變得更加結(jié)構化,路由發(fā)生在軌道上。如今,完全通過約束驅(qū)動的自動化來創(chuàng)建流片質(zhì)量、DRC 校正、匹配和對稱的模擬和自定義數(shù)字布局是可行的。布局設計人員就驅(qū)動工具的適當物理約束做出決策。Cadence Virtuoso Studio中的自動P&R流程將各種單獨的功能和引擎集成到一個無縫的可定制流程中,以滿足不同設計風格的布局創(chuàng)建。

由于工具可以使用約束重新創(chuàng)建布局,因此不再需要對布局進行分區(qū)以重用微小的子單元格。盡管如此,仍然需要許多自定義布局設計器來檢查自動化的結(jié)果,在出現(xiàn)故障時對其進行調(diào)試,并創(chuàng)建或更新約束以重新運行自動化。

并發(fā)布局編輯

與過去的其他數(shù)據(jù)庫一樣,OpenAccess 保留了一個設計作為文件存儲在磁盤上的限制,并且一次只能由一個人編輯。文件由在布局編輯器中打開它的第一個人鎖定。因此,即使大型自定義布局可以通過自動化工具實現(xiàn)扁平化,由多個用戶對其進行審查和修改也是一個挑戰(zhàn)。

Virtuoso Layout Suite(Virtuoso Studio的一部分)中的并發(fā)布局編輯功能優(yōu)雅地解決了這個問題。一個布局可以由區(qū)塊所有者劃分為多個部分,并分配給不同的用戶。用戶可以打開和編輯其分區(qū),而不會中斷其他人的工作。他們可以查看其他分區(qū)并根據(jù)需要引入更改。區(qū)塊所有者可以查看其他用戶在其相應分區(qū)上添加的更改,并將更改集成到原始布局中。區(qū)塊所有者還可以放棄一些編輯,并通知分區(qū)所有者接受這些編輯的挑戰(zhàn)。

設計規(guī)劃

盡管布局層次結(jié)構是不必要的,但分區(qū)仍然具有其重要性。在自定義布局中,電路的某些部分需要小心保護,使其免受其他部分的影響。并且有些部分需要保持在一起才能更好地匹配。由于電路設計人員手動將設計的邏輯表示形式創(chuàng)建為原理圖或網(wǎng)表,因此無法避免設計層次結(jié)構。但是,在布局中實現(xiàn)它們可能比將元素分組到邏輯層次結(jié)構中更好的方法。手動完成布局時,設計人員不關心將邏輯層次結(jié)構與物理層次結(jié)構匹配。相反,他們在布局中創(chuàng)建設計層次結(jié)構,并依靠布局與原理圖(LVS)來確保兩者匹配。事實上,由于這種不匹配的邏輯和物理層次結(jié)構,LVS工具在電路設計流程中的重要性仍然很高。

在邏輯和物理設計層次結(jié)構完美匹配的理想世界中,用戶可以依靠Virtuoso布局套件中的原理圖驅(qū)動布局檢查來確保設計始終保持LVS正確。

這個問題的正確解決方案是什么?

Virtuoso Layout Suite 中的虛擬層次結(jié)構概念允許布局設計人員在布局中創(chuàng)建與原理圖不同的元素分組,但仍保持 SDL 對應關系。使用虛擬層次結(jié)構,布局設計人員可以對設計進行分區(qū),并創(chuàng)建組和子組以分隔需要隔離的布局。從OpenAccess數(shù)據(jù)庫的角度來看,布局仍然是平面的,因為只有一個布局單元格視圖。虛擬層次結(jié)構有助于布局實施過程中的自動化工具。

結(jié)論

使用虛擬層次結(jié)構,布局設計人員可以選擇不同于邏輯設計層次結(jié)構的設計層次結(jié)構。可以對布局進行分區(qū),以指導自動化根據(jù)需要構造布局。將布局保留為單個單元視圖可確保 SDL 對應,從而保證 LVS 的正確性。由于用戶不會過度分區(qū)布局,因此自動P&R工具可以更自由地生成滿足用戶設置的所有約束的優(yōu)化布局。基于行的方法提高了結(jié)果質(zhì)量和工具運行時。

并發(fā)布局編輯解決了布局審查、調(diào)試和編輯問題,因為可以同時分配多個用戶來處理同一布局的不同部分。區(qū)塊所有者可以指派團隊的初級成員來查看布局并提出更改建議。最終,區(qū)塊所有者可以將各種用戶所做的工作吸收到原始布局中,而不會遇到任何麻煩。

審核編輯:郭婷

-

自動化

+關注

關注

29文章

5738瀏覽量

81580 -

DRC

+關注

關注

2文章

153瀏覽量

36922 -

LVS

+關注

關注

1文章

37瀏覽量

10120

發(fā)布評論請先 登錄

如何縮短Vivado的運行時間

如何檢查Linux服務器的運行時間

運行時軟件故障注入器的設計與實現(xiàn)

紫金橋組態(tài)軟件新的功能_運行時組態(tài)

Maxim發(fā)布最新基礎模擬收發(fā)器,旨在提高工業(yè)系統(tǒng)的正常運行時間

如何高效測量ECU的運行時間

Go運行時:4年之后

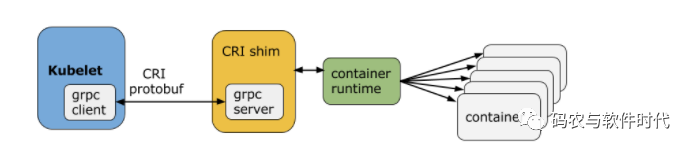

什么是Kubernetes容器運行時CRI

ch32v307記錄程序運行時間

Xilinx運行時(XRT)發(fā)行說明

設計層次結(jié)構提高結(jié)果質(zhì)量和工具運行時

設計層次結(jié)構提高結(jié)果質(zhì)量和工具運行時

評論