電子發燒友網報道(文/梁浩斌)SiC MOSFET的發展歷史其實相當長遠,全球SiC產業龍頭Wolfspeed的前身Cree公司,其創始人之一John Palmour在1987年申請了一項涉及在SiC襯底上生成MOS電容器的結構,這項專利后來被視為促成SiC MOSFET誕生的關鍵。

不過,由于襯底良率、制造工藝等問題,直到2011年SiC MOSFET才正式實現商業化,彼時的Cree推出了市場上第一款SiC MOSFET,采用平面柵結構的CMF20120D。到了2015年,羅姆率先實現溝槽柵結構SiC MOSFET的量產,這種結構更能夠發揮SiC材料的特性,工藝更復雜。經過10多年的發展,目前在SiC MOSFET的技術路線上,溝槽柵已經被認為是更有優勢的方向。

平面柵和溝槽柵有哪些區別?

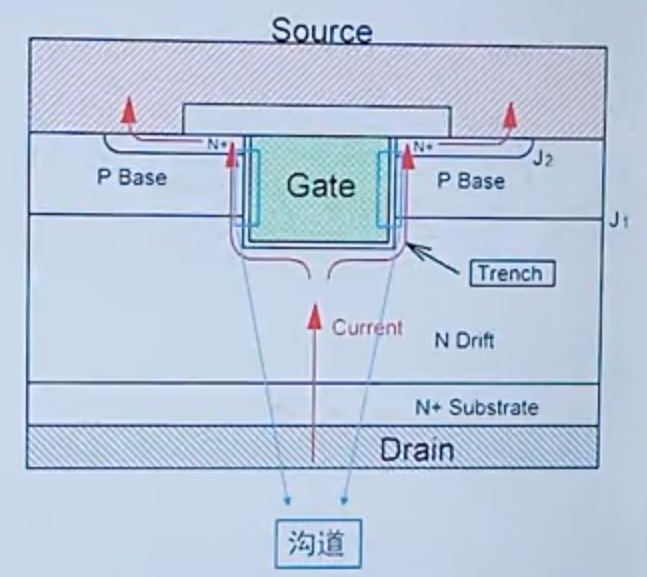

從結構上看,最明顯的特征是,平面結構的SiC MOSFET是指柵極電極和源極電極在同一水平面上,也就是呈現“平面”分布,溝道與襯底平行。平面柵工藝相對簡單,容易實現較好的柵氧化層質量,有較強的抗電壓沖擊能力,實際應用中可靠性更高,在過載工況下也不容易被損壞。

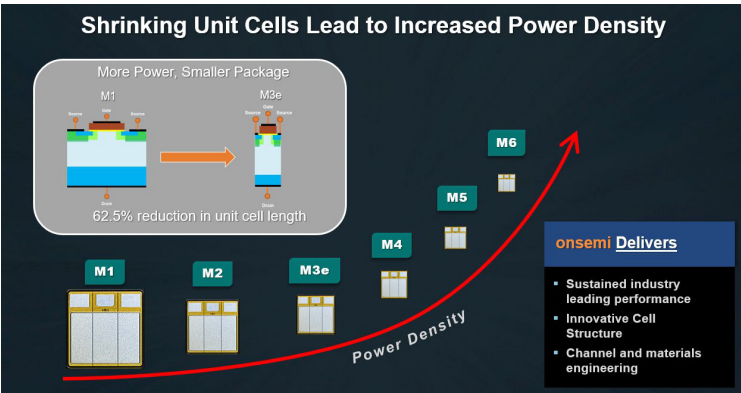

不過相對地,對于MOSFET而言,器件導通能力取決于元胞間距,元胞間距越小、密度越高,導通電阻以及開關損耗就越低,同時還能提高器件的耐壓能力,降低器件尺寸,提升功率密度。但平面柵由于柵極是橫向,所以一定程度上限制了元胞間距的縮小,為了進一步縮小元胞間距,溝槽柵結構取代平面柵就成了目前的功率芯片廠商的產品趨勢。

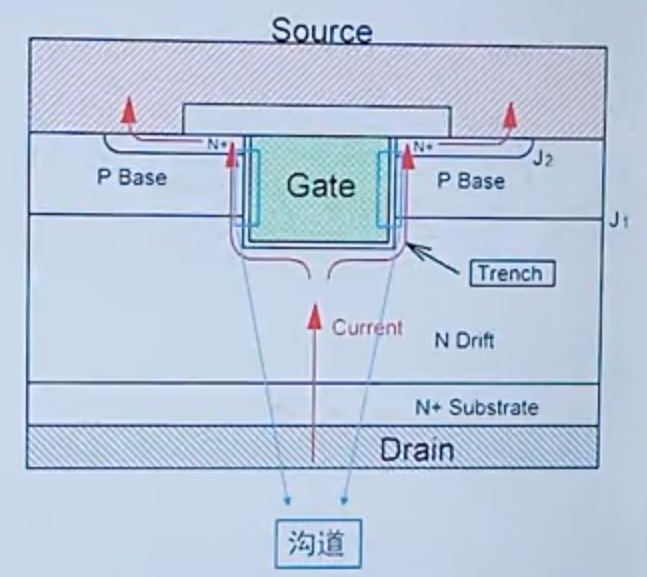

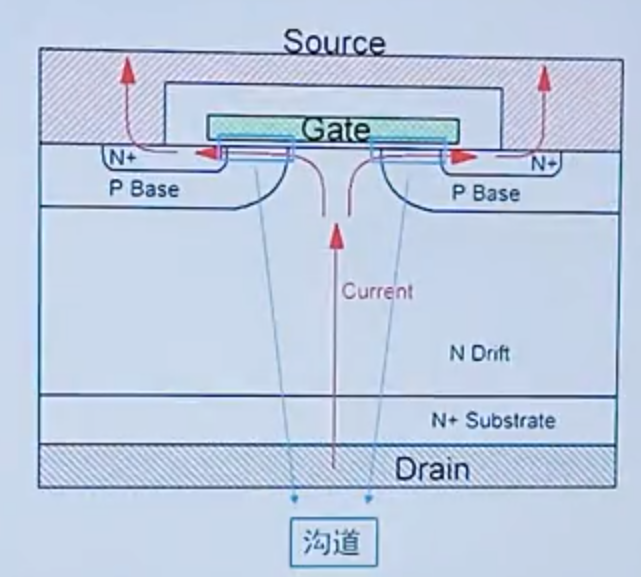

溝槽柵結構 圖源:基本半導體

溝槽柵結構是指柵極電極位于源極電極下方,在半導體材料中形成一個“溝槽”。同時也能從上圖中看到,溝槽柵結構中的溝道和柵極是垂直于襯底的,這也是與平面柵結構的一個顯著區別,正因為這樣的結構,可以讓功率芯片的元胞間距大幅縮小,在性能上展現出比平面柵SiC MOSFET更低的導通電阻、更強的開關性能、更低的導通損耗等。

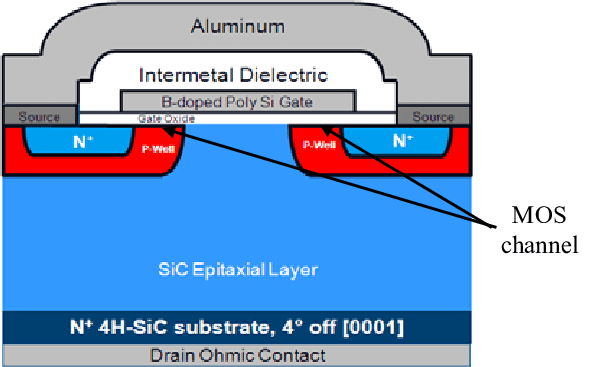

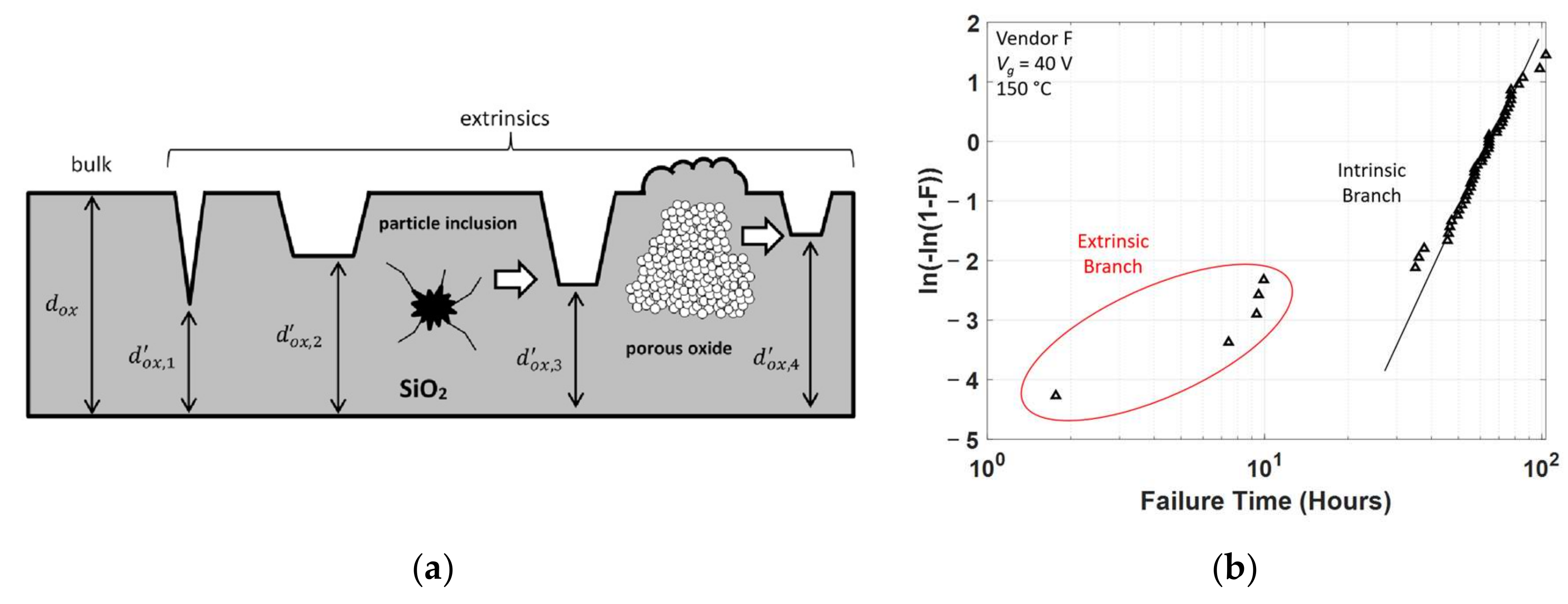

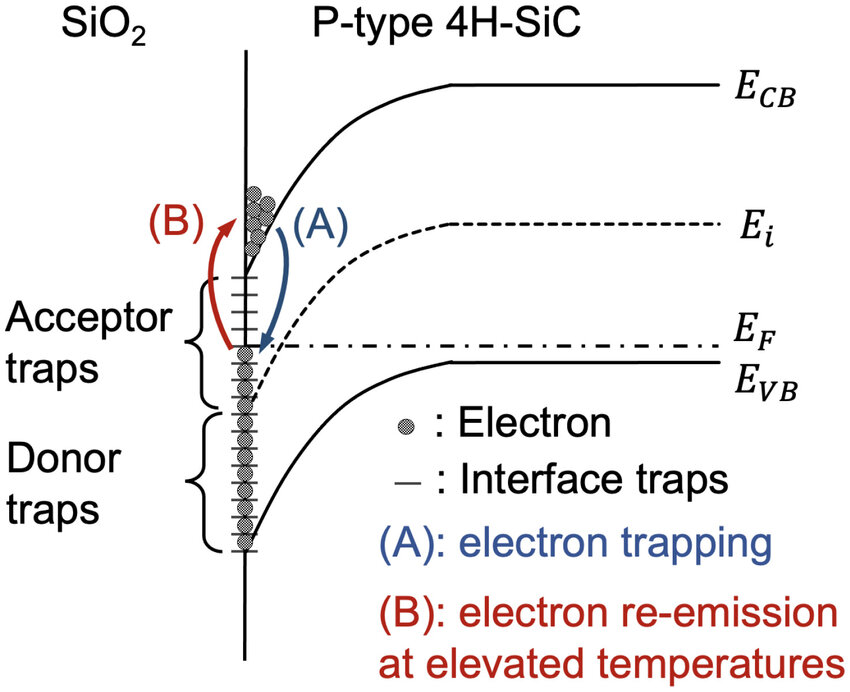

但溝槽柵也不是完全沒有缺點。結構上溝槽柵SiC MOSFET需要在基板上挖出溝槽,將柵極埋入形成垂直溝道,工藝顯然相比平面柵更復雜,良率、單元一致性都較差。同時,溝槽柵SiC MOSFET中的二氧化硅柵極所承受的電場強度比在硅基IGBT/MOSFET中高很多,因此柵極氧化層的可靠性會存在一些問題。當然,這些問題可以通過改進柵極氧化工藝等方式解決,或是通過不同的結構設計改善柵極底部電場集中的問題。

溝槽柵SiC MOSFET發展現狀

羅姆作為最早量產SiC MOSFET的廠商,在2010年率先量產平面柵SiC MOSFET之后,在2015年的第三代產品上又再一次奪得先機,率先量產雙溝槽結構的第三代產品。正如上文的溝槽柵結構示意圖中一樣,SiC MOSFET一般是單溝槽結構,即只有柵極溝槽;羅姆開發出的雙溝槽MOSFET即同時具有源極溝槽和柵極溝槽。

前文我們也提到,為了充分利用SiC材料的高擊穿能力,需要改善柵極氧化物處電場集中的問題。羅姆在官方介紹中表示,SiC MOSFET通過采用雙溝槽的結構,在測試中可以實現比羅姆第二代平面柵SiC MOSFET降低約50%的導通電阻,同時輸入電容降低35%,提升了開關性能。

羅姆2021年推出最新的第四代SiC MOSFET,進一步改進了雙溝槽結構,成功在改善短路耐受時間的前提下,使導通電阻比第三代產品又降低約40%;同時通過大幅降低柵漏電容,成功地使開關損耗比以第三代產品降低約50%。按照其產品路線圖,預計2025年和2028年推出的第五代和第六代產品的導通電阻將會分別再降低30%。

英飛凌的SiC MOSFET采用了不對稱的半包溝槽結構,與羅姆幾乎是目前業界唯二量產上車的SiC MOSFET溝槽設計。這種不對稱的半包溝槽結構能夠在獨特的晶面上形成溝道,并可以使用較厚的柵極氧化層,實現很低的導通電阻,并提高了可靠性。英飛凌在2016年推出了第一代CoolSiC系列SiC MOSFET,并在2022年更新了第二代產品,相比第一代增強了25%-30%的載電流能力。

目前量產溝槽型SiC MOSFET的國際廠商還包括富士、三菱電機、住友電工、日本電裝等,還有更多比如ST、博世、安森美等廠商,都有相關布局,ST計劃在2025年推出其首款溝槽型SiC MOSFET產品。從國際廠商的布局來看,溝槽柵SiC MOSFET會是未來更具競爭力的方案。

國內方面,安海半導體、芯塔電子、芯長征科技、中車時代等都已經有相關的專利技術等布局,目前溝槽柵SiC MOSFET的專利競爭較大,特別是日系廠商比如電裝、羅姆、富士電機等較為強勢。國內廠商入局相對較晚,但相對布局較前的廠商可能會擁有更大的發揮空間。

小結:

總而言之,提高SiC MOSFET性能的幾個重要指標,包括更小的元胞間距、更低的導通電阻、更低的開關損耗、更高的可靠性(柵極氧化保護),幾乎都指向了溝槽柵結構。從2015年第一款量產溝槽柵SiC MOSFET產品推出到現在過去了8年時間,但市面上能夠推出量產產品的廠商并不算多,在目前整體SiC市場持續高速增長的時期,提前布局合適的技術路線,才有機會在未來新的應用市場上占得先機。

不過,由于襯底良率、制造工藝等問題,直到2011年SiC MOSFET才正式實現商業化,彼時的Cree推出了市場上第一款SiC MOSFET,采用平面柵結構的CMF20120D。到了2015年,羅姆率先實現溝槽柵結構SiC MOSFET的量產,這種結構更能夠發揮SiC材料的特性,工藝更復雜。經過10多年的發展,目前在SiC MOSFET的技術路線上,溝槽柵已經被認為是更有優勢的方向。

平面柵和溝槽柵有哪些區別?

從結構上看,最明顯的特征是,平面結構的SiC MOSFET是指柵極電極和源極電極在同一水平面上,也就是呈現“平面”分布,溝道與襯底平行。平面柵工藝相對簡單,容易實現較好的柵氧化層質量,有較強的抗電壓沖擊能力,實際應用中可靠性更高,在過載工況下也不容易被損壞。

不過相對地,對于MOSFET而言,器件導通能力取決于元胞間距,元胞間距越小、密度越高,導通電阻以及開關損耗就越低,同時還能提高器件的耐壓能力,降低器件尺寸,提升功率密度。但平面柵由于柵極是橫向,所以一定程度上限制了元胞間距的縮小,為了進一步縮小元胞間距,溝槽柵結構取代平面柵就成了目前的功率芯片廠商的產品趨勢。

溝槽柵結構 圖源:基本半導體

溝槽柵結構是指柵極電極位于源極電極下方,在半導體材料中形成一個“溝槽”。同時也能從上圖中看到,溝槽柵結構中的溝道和柵極是垂直于襯底的,這也是與平面柵結構的一個顯著區別,正因為這樣的結構,可以讓功率芯片的元胞間距大幅縮小,在性能上展現出比平面柵SiC MOSFET更低的導通電阻、更強的開關性能、更低的導通損耗等。

但溝槽柵也不是完全沒有缺點。結構上溝槽柵SiC MOSFET需要在基板上挖出溝槽,將柵極埋入形成垂直溝道,工藝顯然相比平面柵更復雜,良率、單元一致性都較差。同時,溝槽柵SiC MOSFET中的二氧化硅柵極所承受的電場強度比在硅基IGBT/MOSFET中高很多,因此柵極氧化層的可靠性會存在一些問題。當然,這些問題可以通過改進柵極氧化工藝等方式解決,或是通過不同的結構設計改善柵極底部電場集中的問題。

溝槽柵SiC MOSFET發展現狀

羅姆作為最早量產SiC MOSFET的廠商,在2010年率先量產平面柵SiC MOSFET之后,在2015年的第三代產品上又再一次奪得先機,率先量產雙溝槽結構的第三代產品。正如上文的溝槽柵結構示意圖中一樣,SiC MOSFET一般是單溝槽結構,即只有柵極溝槽;羅姆開發出的雙溝槽MOSFET即同時具有源極溝槽和柵極溝槽。

前文我們也提到,為了充分利用SiC材料的高擊穿能力,需要改善柵極氧化物處電場集中的問題。羅姆在官方介紹中表示,SiC MOSFET通過采用雙溝槽的結構,在測試中可以實現比羅姆第二代平面柵SiC MOSFET降低約50%的導通電阻,同時輸入電容降低35%,提升了開關性能。

羅姆2021年推出最新的第四代SiC MOSFET,進一步改進了雙溝槽結構,成功在改善短路耐受時間的前提下,使導通電阻比第三代產品又降低約40%;同時通過大幅降低柵漏電容,成功地使開關損耗比以第三代產品降低約50%。按照其產品路線圖,預計2025年和2028年推出的第五代和第六代產品的導通電阻將會分別再降低30%。

英飛凌的SiC MOSFET采用了不對稱的半包溝槽結構,與羅姆幾乎是目前業界唯二量產上車的SiC MOSFET溝槽設計。這種不對稱的半包溝槽結構能夠在獨特的晶面上形成溝道,并可以使用較厚的柵極氧化層,實現很低的導通電阻,并提高了可靠性。英飛凌在2016年推出了第一代CoolSiC系列SiC MOSFET,并在2022年更新了第二代產品,相比第一代增強了25%-30%的載電流能力。

目前量產溝槽型SiC MOSFET的國際廠商還包括富士、三菱電機、住友電工、日本電裝等,還有更多比如ST、博世、安森美等廠商,都有相關布局,ST計劃在2025年推出其首款溝槽型SiC MOSFET產品。從國際廠商的布局來看,溝槽柵SiC MOSFET會是未來更具競爭力的方案。

國內方面,安海半導體、芯塔電子、芯長征科技、中車時代等都已經有相關的專利技術等布局,目前溝槽柵SiC MOSFET的專利競爭較大,特別是日系廠商比如電裝、羅姆、富士電機等較為強勢。國內廠商入局相對較晚,但相對布局較前的廠商可能會擁有更大的發揮空間。

小結:

總而言之,提高SiC MOSFET性能的幾個重要指標,包括更小的元胞間距、更低的導通電阻、更低的開關損耗、更高的可靠性(柵極氧化保護),幾乎都指向了溝槽柵結構。從2015年第一款量產溝槽柵SiC MOSFET產品推出到現在過去了8年時間,但市面上能夠推出量產產品的廠商并不算多,在目前整體SiC市場持續高速增長的時期,提前布局合適的技術路線,才有機會在未來新的應用市場上占得先機。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

SiC

+關注

關注

31文章

3141瀏覽量

64333

發布評論請先 登錄

相關推薦

熱點推薦

為何必須通過TDDB(時間相關介質擊穿)方法檢驗國產SiC MOSFET的柵氧可靠性水平

應用場景,分析HTGB(高溫柵偏)實驗的局限性,以及為何必須通過TDDB(時間相關介質擊穿)方法檢驗國產SiC MOSFET的柵氧可靠性水平

SiC碳化硅MOSFET驅動電壓的限制源于柵氧可靠性與器件性能之間的權衡

碳化硅(SiC)MOSFET的Vgs正負驅動電壓限制的根本原因源于其柵氧化層(通常為SiO?)的電場耐受能力和界面特性,需在柵氧可靠性與器件性能之間進行權衡。以下是具體分析: 傾佳電子

SiC MOSFET 開關模塊RC緩沖吸收電路的參數優化設計

0? 引言SiC-MOSFET 開關模塊(簡稱“SiC 模塊”)由于其高開關速度、高耐壓、低損耗的特點特別適合于高頻、大功率的應用場合。相比 Si-IGBT, SiC-MOSFET 開關速度更快

發表于 04-23 11:25

國產SiC碳化硅MOSFET廠商絕口不提柵氧可靠性的根本原因是什么

部分國產SiC碳化硅MOSFET廠商避談柵氧可靠性以及TDDB(時間相關介電擊穿)和HTGB(高溫柵偏)報告作假的現象,反映了行業深層次的技

碳化硅(SiC)MOSFET的柵氧可靠性成為電力電子客戶應用中的核心關切點

背后涉及材料特性、工藝挑戰、應用場景的嚴苛性以及產業鏈成熟度的多重博弈。 客戶的電力電子研發工程師在與國產SiC MOSFET供應商交流時首先聚焦于柵氧可靠性問題,這一現象也確實反映了對國產碳化硅功率器件市場亂象魚龍混雜

如何測試SiC MOSFET柵氧可靠性

隨著電力電子技術的飛速發展,碳化硅(SiC)金屬氧化物半導體場效應晶體管(MOSFET)因其優異的性能,如高開關速度、低導通電阻和高工作溫度,逐漸成為高頻、高效功率轉換應用的理想選擇。然而,S

溝槽型SiC MOSFET的結構和應用

碳化硅(SiC)作為第三代半導體材料,因其出色的寬禁帶、高臨界擊穿電場、高電子飽和遷移速率和高導熱率等特性,在新能源、智能電網以及電動汽車等多個領域展現出廣闊的應用前景。其中,溝槽型SiC

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

具有決定性的影響。因此,深入理解柵極氧化層的特性,并掌握其可靠性測試方法,對于推動碳化硅 MOSFET的應用和發展具有重要意義。今天的“SiC科普小課堂”將聚焦于“柵極氧化層”這一新話題:“什么是柵極

發表于 01-04 12:37

又一大廠確定下一代SiC MOSFET采用溝槽設計

電子發燒友網報道(文/梁浩斌)2024年上半年,安森美發布了第二代1200V SiC MOSFET產品,在這款產品上采用了最新的面向高開關性能的M3S工藝平臺(M3平臺還有另一個分支M3T,主要針對

SiC MOSFET和SiC SBD的區別

SiC MOSFET(碳化硅金屬氧化物半導體場效應晶體管)和SiC SBD(碳化硅肖特基勢壘二極管)是兩種基于碳化硅(SiC)材料的功率半導體器件,它們在電力電子領域具有廣泛的應用。盡

我國首次突破溝槽型碳化硅MOSFET芯片制造技術:開啟半導體產業新篇章

展現出巨大的應用潛力。近日,國家第三代半導體技術創新中心(南京)宣布成功攻關溝槽型碳化硅MOSFET芯片制造關鍵技術,這不僅標志著我國在半導體高端制造領域取得了重

首次量產至今8年時間,溝槽柵SiC MOSFET的發展現狀如何?

首次量產至今8年時間,溝槽柵SiC MOSFET的發展現狀如何?

評論