題目說(shuō)明

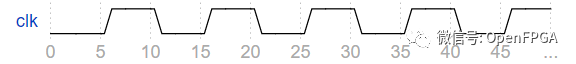

編寫(xiě)一個(gè)創(chuàng)建模塊dut實(shí)例(具有任何實(shí)例名稱(chēng))的測(cè)試平臺(tái),并創(chuàng)建一個(gè)時(shí)鐘信號(hào)來(lái)驅(qū)動(dòng)模塊的clk輸入。時(shí)鐘周期為 10 ps。時(shí)鐘應(yīng)初始化為零,其第一個(gè)轉(zhuǎn)換為 0 到 1。

模塊端口聲明

moduletop_module();

題目解析

生成clock有很多種方式,常見(jiàn)的就是forever和always。

timeunit1ps; timeprecision1ps; moduletop_module(); logicclk; dutu1_dut( .clk(clk) ); initialbegin clk<=?1'b0?; ????end ???? ????always?#5?clk?<=?~clk?; ? endmodule

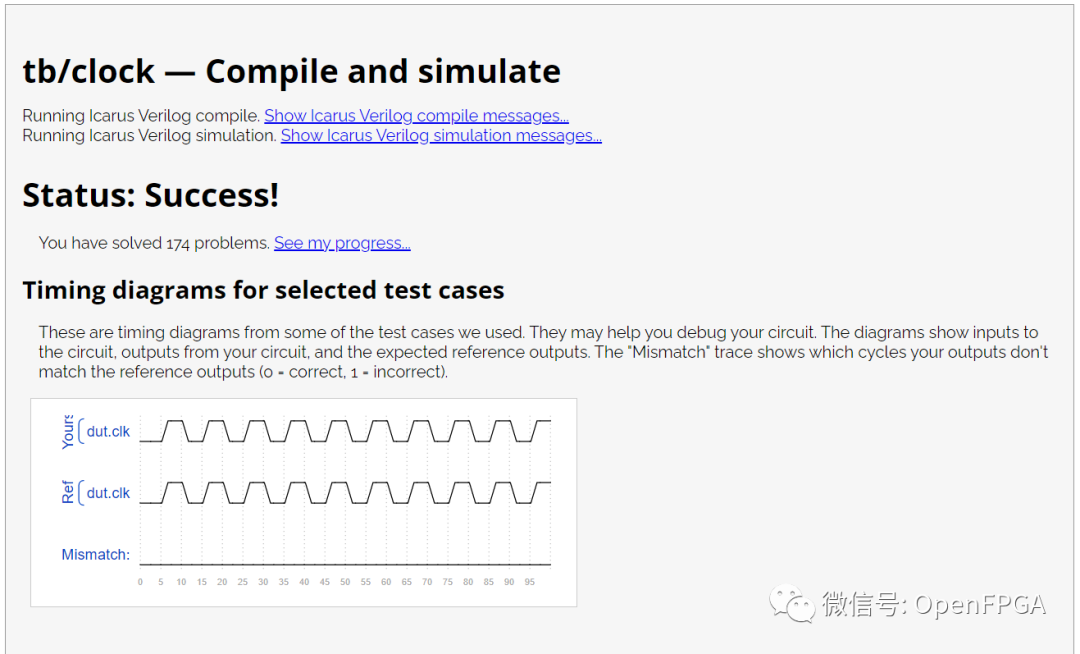

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

Problem 174-tb1

題目說(shuō)明

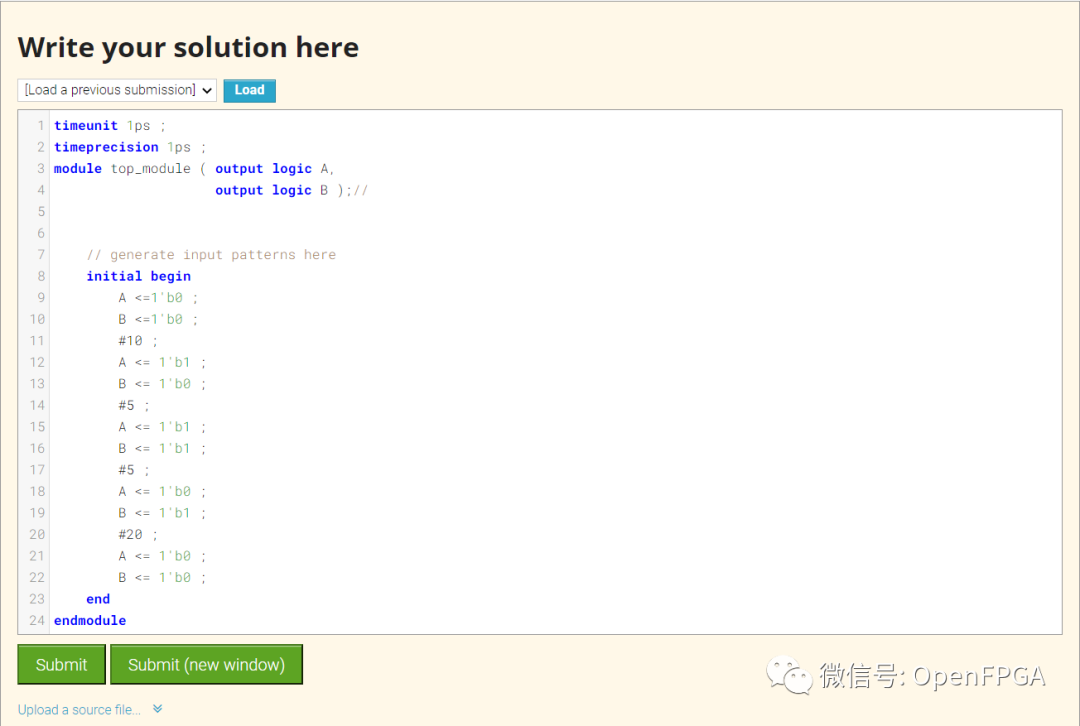

創(chuàng)建一個(gè) Verilog 測(cè)試臺(tái),它將為輸出 A 和 B 生成以下波形

模塊端口聲明

moduletop_module(outputregA,outputregB);

題目解析

initial+# n即可。

timeunit1ps; timeprecision1ps; moduletop_module(outputlogicA, outputlogicB);// //generateinputpatternshere initialbegin A<=1'b0?; ????????B?<=1'b0?; ????????#10?; ????????A?<=?1'b1?; ????????B?<=?1'b0?; ????????#5?; ????????A?<=?1'b1?; ????????B?<=?1'b1?; ????????#5?; ????????A?<=?1'b0?; ????????B?<=?1'b1?; ????????#20?; ????????A?<=?1'b0?; ????????B?<=?1'b0?; ????end endmodule

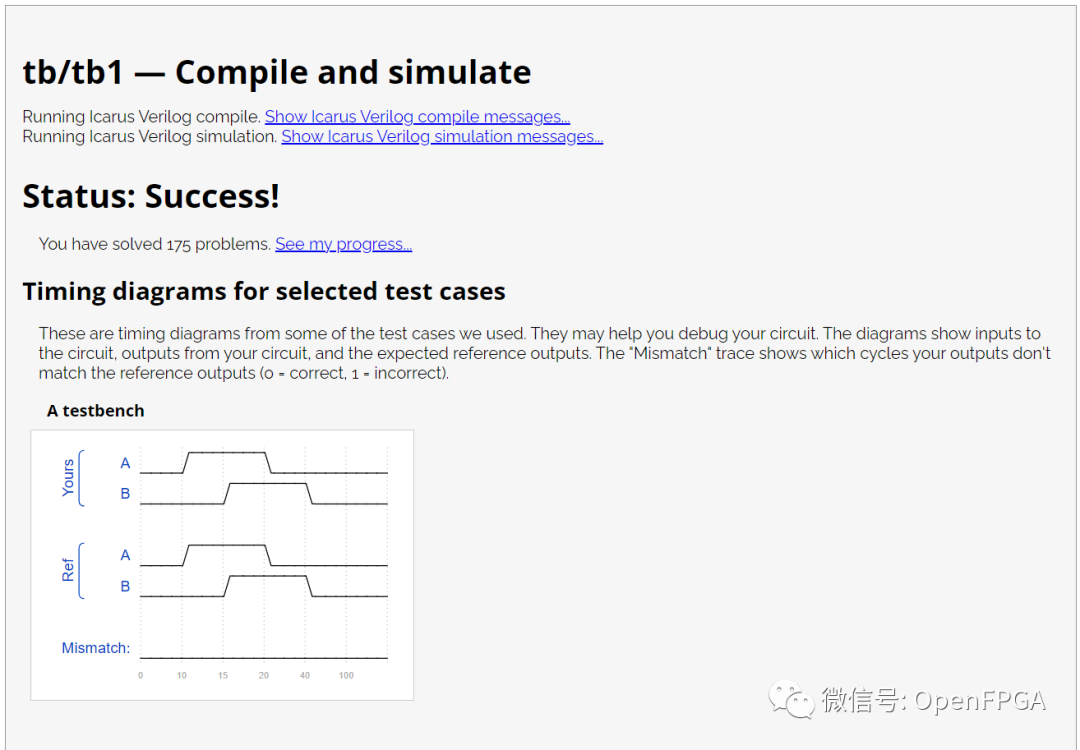

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

Problem 175-and

題目說(shuō)明

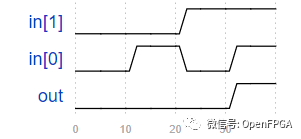

給給定的與門(mén)寫(xiě)測(cè)試文件,波形參考下圖。

模塊端口聲明

moduletop_module();

題目解析

和上一題類(lèi)似。

timeunit1ps; timeprecision1ps; moduletop_module(); logic[1:0]in; wirelogicout; andgateu_andgate( .in(in), .out(out) ); initialbegin in<=?2'b00?; ????????#10?; ????????in?<=?2'b01?; ????????#10?; ????????in?<=?2'b10?; ????????#10?; ????????in?<=?2'b11?; ????end?? ???????? endmodule

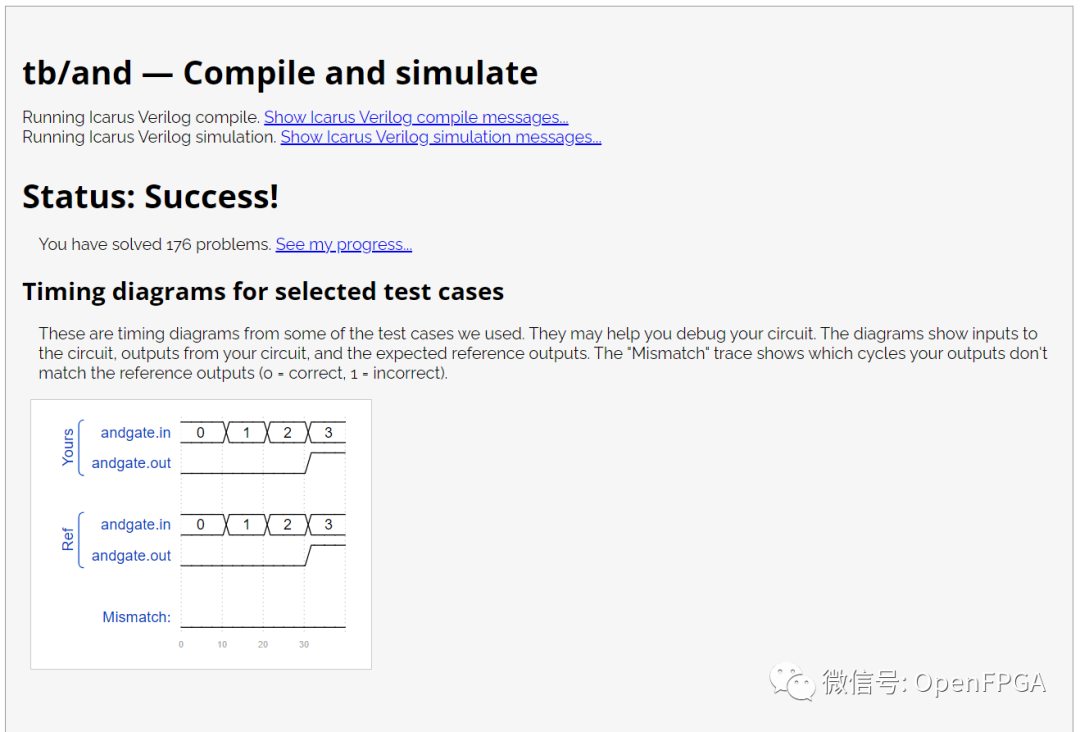

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

Problem 176-tb2

題目說(shuō)明

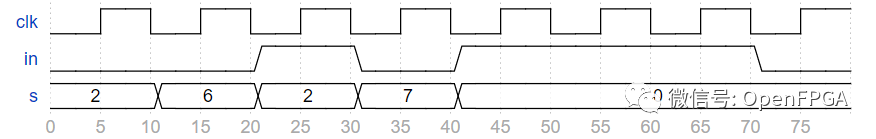

給定一個(gè)q7電路,按照下圖編寫(xiě)testbench:

模塊端口聲明

moduletop_module();

題目解析

timeunit1ps; timeprecision1ps; moduletop_module(); logicclk; logicin; logic[2:0]s; wirelogicout; q7u1_q7( .clk(clk), .in(in), .s(s), .out(out) ); initialbegin clk<=?1'b0?; ????????forever ????????#5?clk?<=?~clk?; ????end ???? ????initial?begin ????????in?<=?1'b0?; ????????s??<=?3'd2?; ????????#10?; ????????in?<=?1'b0?; ????????s??<=?3'd6?; ????????#10?; ????????in?<=?1'b1?; ????????s??<=?3'd2?; ????????#10?; ????????in?<=?1'b0?; ????????s??<=?3'd7?; ????????#10?; ????????in?<=?1'b1?; ????????s??<=?3'd0?; ????????#30?; ????????in?<=?1'b0?; ????????s??<=?3'd0?; ????end ???????? endmodule

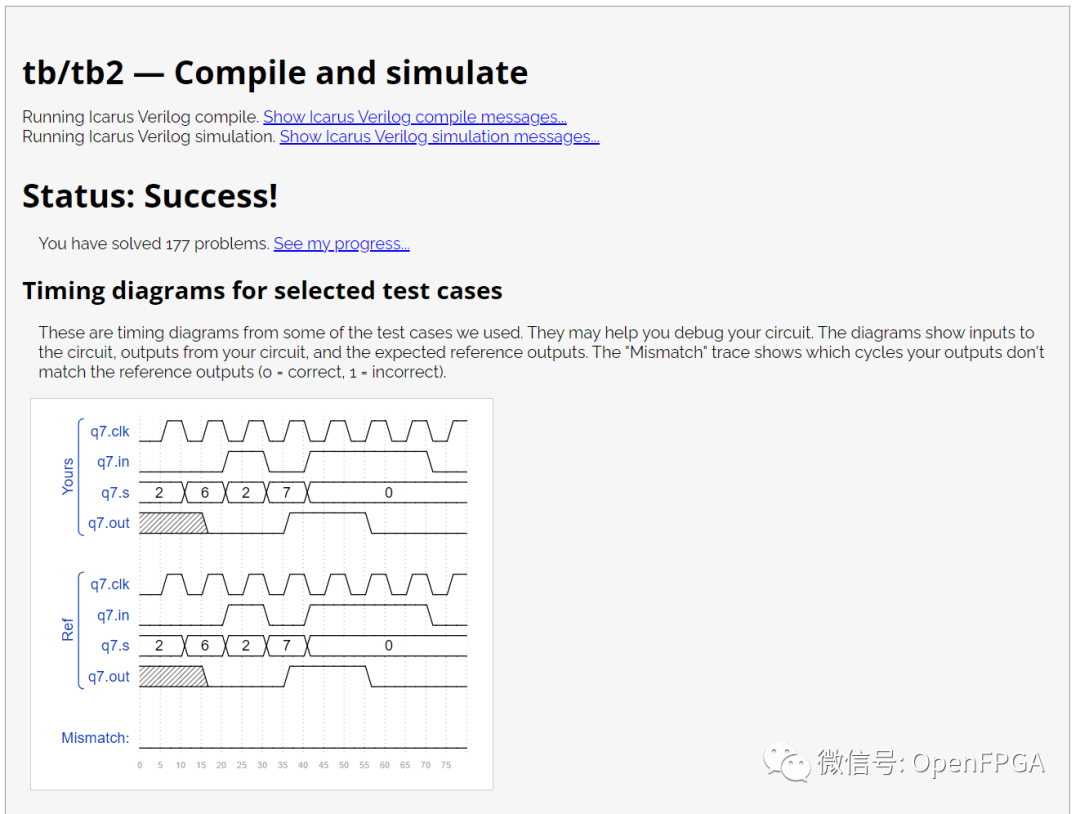

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

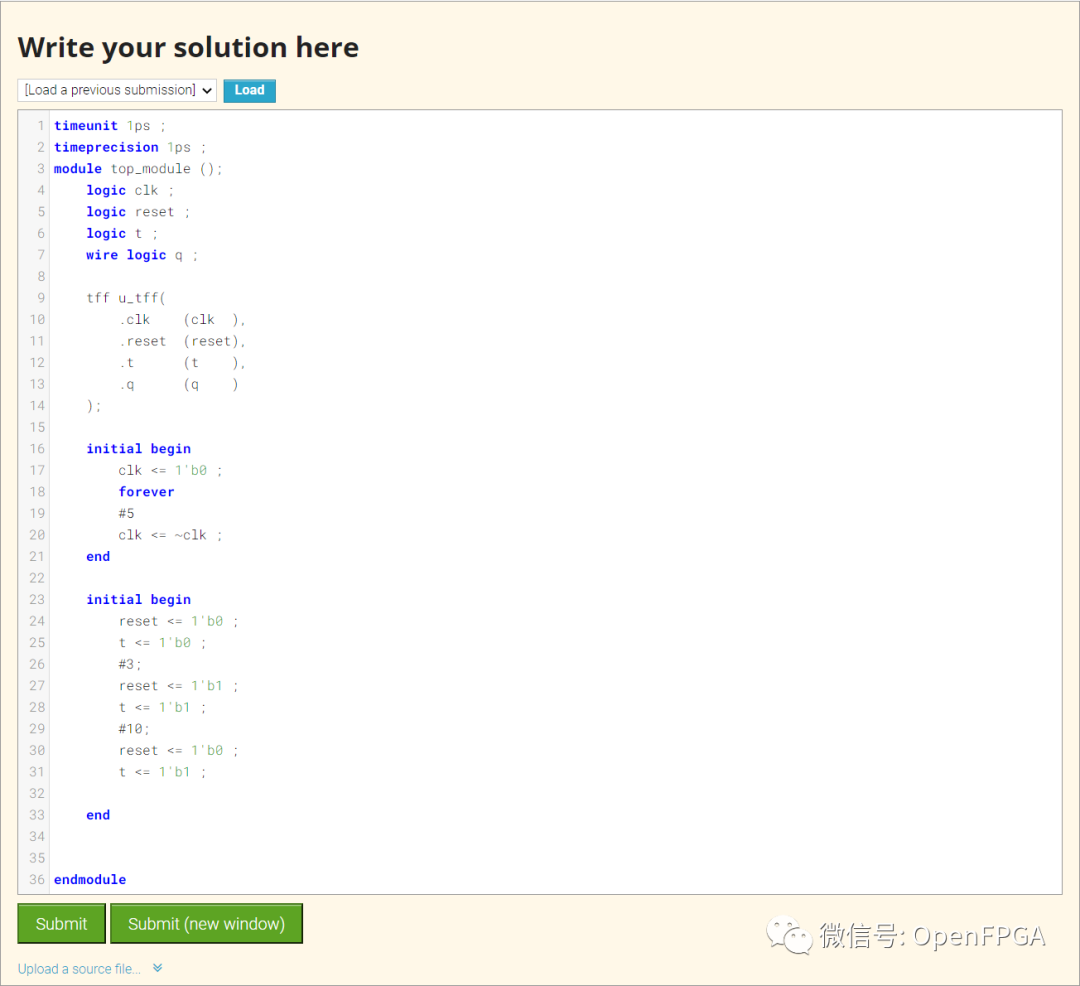

Problem 177-tff

題目說(shuō)明

給題目中給定的tff編寫(xiě)測(cè)試文件。

模塊端口聲明

moduletop_module();

題目解析

timeunit1ps; timeprecision1ps; moduletop_module(); logicclk; logicreset; logict; wirelogicq; tffu_tff( .clk(clk), .reset(reset), .t(t), .q(q) ); initialbegin clk<=?1'b0?; ????????forever ????????#5 ????????clk?<=?~clk?; ????end ???? ????initial?begin ????????reset?<=?1'b0?; ????????t?<=?1'b0?; ????????#3; ????????reset?<=?1'b1?; ????????t?<=?1'b1?; ????????#10; ????????reset?<=?1'b0?; ????????t?<=?1'b1?; ????end ? endmodule

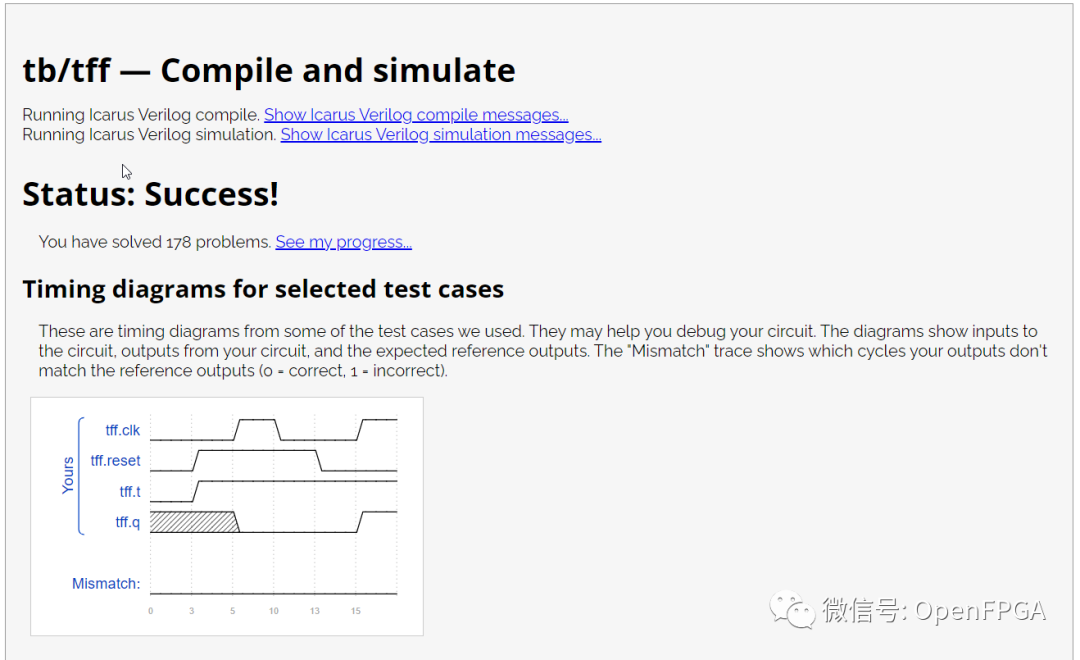

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對(duì)比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

審核編輯:劉清

-

Verilog

+關(guān)注

關(guān)注

28文章

1365瀏覽量

111686 -

HDL

+關(guān)注

關(guān)注

8文章

330瀏覽量

47782 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

464瀏覽量

29038 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17498

原文標(biāo)題:HDLBits: 在線學(xué)習(xí) SystemVerilog(二十四)-Problem 163-177(TestBench)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

如何在PetaLinux流程外創(chuàng)建模塊

阿里云云效功能升級(jí),支持快速創(chuàng)建多個(gè)應(yīng)用的獨(dú)立測(cè)試環(huán)境

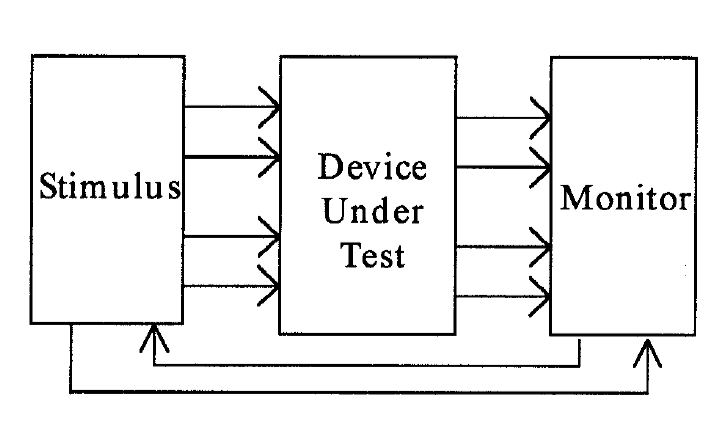

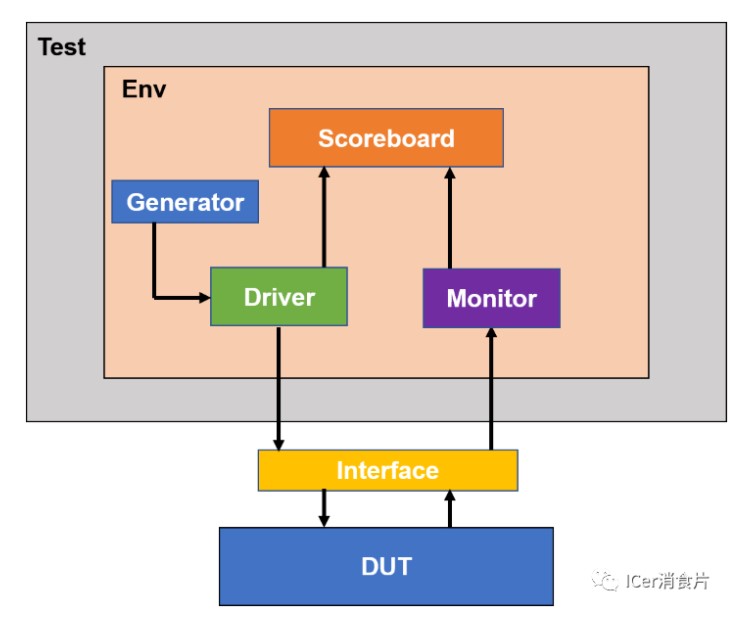

FPGA固件開(kāi)發(fā)- 測(cè)試平臺(tái)的編寫(xiě)

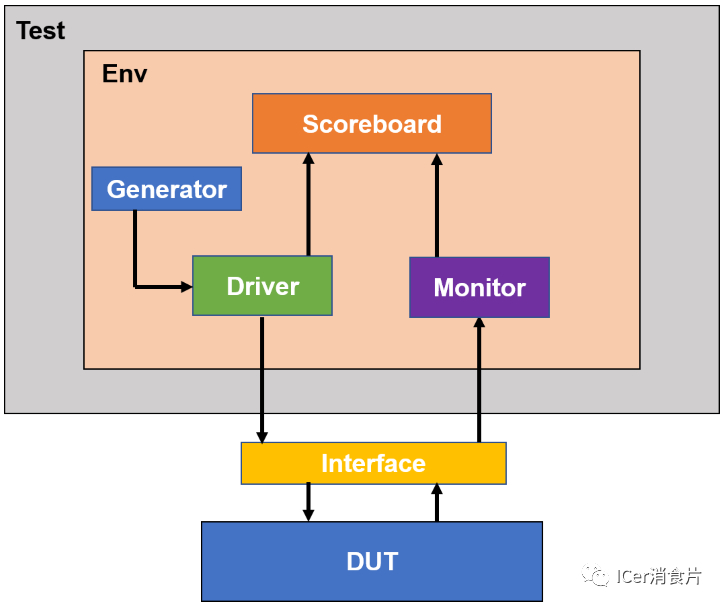

數(shù)字IC驗(yàn)證之“構(gòu)成uvm測(cè)試平臺(tái)的主要組件”(4)連載中...

Simulink建模仿真實(shí)例快速入門(mén)

Verilog HDL硬件描述語(yǔ)言_建模實(shí)例

PCB設(shè)計(jì):網(wǎng)絡(luò)分析儀測(cè)試DUT出現(xiàn)2個(gè)差不多的阻抗?

VHDL測(cè)試平臺(tái)編寫(xiě)綜述

使用物聯(lián)網(wǎng)平臺(tái)創(chuàng)建一個(gè)溫度警報(bào)系統(tǒng)

對(duì)DUT輸入定向或隨機(jī)的激勵(lì)

DUT 和 testbench 連接教程

SOLIDWORKS曲面建模實(shí)例

芯片驗(yàn)證需要圍繞DUT做什么?

可重用的驗(yàn)證組件中構(gòu)建測(cè)試平臺(tái)的步驟

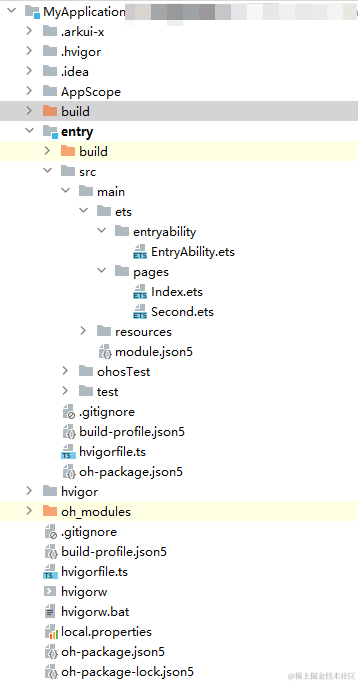

鴻蒙ArkUI-X跨平臺(tái)開(kāi)發(fā):【 編寫(xiě)第一個(gè)ArkUI-X應(yīng)用】

編寫(xiě)一個(gè)創(chuàng)建模塊dut實(shí)例的測(cè)試平臺(tái)

編寫(xiě)一個(gè)創(chuàng)建模塊dut實(shí)例的測(cè)試平臺(tái)

評(píng)論