1 運行平臺

硬件:CRD500數字信號處理板

系統:win7/64(推薦);win7/32;win10/64

軟件:Quartus13.1/ModelSimSE 10.1c/Verilog HDL/Matlab2014a

2 主要功能及性能指標

2.1 主要功能

1)可產生ASK、FSK、PSK、單頻信號、三角波、鋸齒波、方波

2)載波頻率、調制參數等波形參數可設置

3)可通過串口設置信號參數

2.2 主要性能指標

1)系統時鐘:50MHz

2)串口協議:9600bps波特率、1位起始位、8位數據位、1位停止位、無校驗位

3)載波頻率范圍:1MHz~4.75MHz可變,步進250kHz

4) 基帶信號碼速率范圍:100kHz~475kHz,步進25kHz

5)三角波頻率范圍: 6kHz~98kHz,共16種頻率可設置

6) 鋸齒波頻率范圍: 12kHz~195kHz,共16種頻率可設置

7)方波頻率范圍:50kHz~237.5kHz,步進12.5kHz

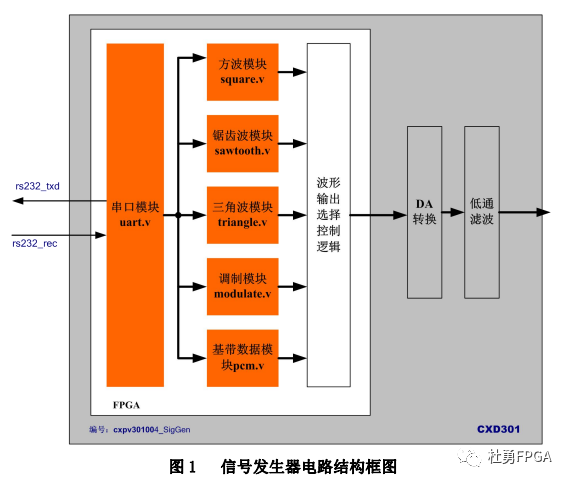

3 程序結構框圖說明

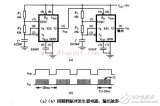

信號發生器電路程序主要串口通信模塊(uart.v)、方波模塊(square.v)、鋸齒波模塊(sawtooth.v)、三角波模塊(triangle.v)、基帶數據模塊(pcm.v)和調制模塊(modulate.v)組成。

uart.v模塊完成與計算機之間的串口通信,接收串口發出的指令,并將接收到的指令回送至計算機,驗證指令傳輸的正確性。串口接收的指令送至各信號波形產生模塊,產生相應參數的信號波形。

方波模塊(square.v)、鋸齒波模塊(sawtooth.v)、三角波模塊(triangle.v)分別根據指令參數產生方波、鋸齒波和三角波信號。基帶數據模塊產生8比特循環的基帶數據11111010,并將基帶數據送至調制模塊modulate.v。modulate.v模塊產生正弦波、ASK、PSK和FSK信號。

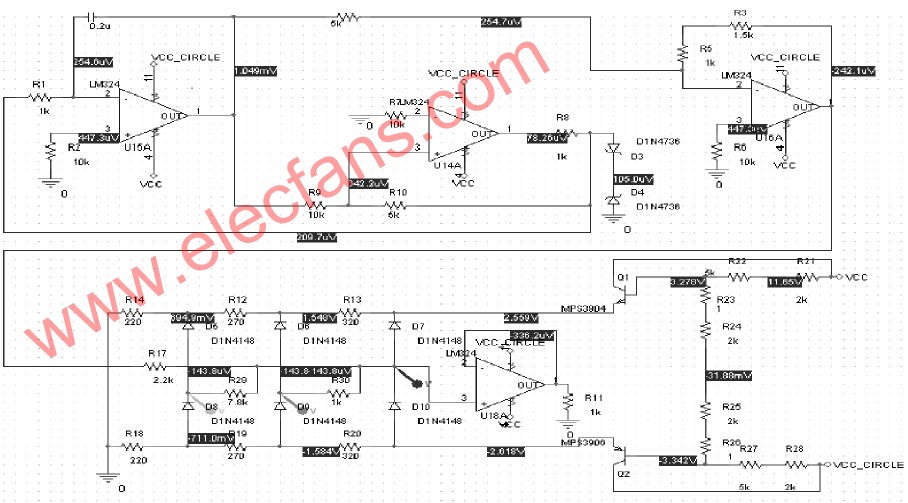

波形輸出選擇控制邏輯根據串口指令輸出對應的波形信號,經信號處理板上的DA轉換及濾波電路后,形成模擬波形輸出。

審核編輯:劉清

-

濾波電路

+關注

關注

47文章

650瀏覽量

70354 -

FSK

+關注

關注

14文章

115瀏覽量

58928 -

信號發生器

+關注

關注

28文章

1551瀏覽量

110149 -

串口通信

+關注

關注

34文章

1635瀏覽量

56524 -

PSK

+關注

關注

1文章

27瀏覽量

21182

原文標題:信號發生器電路(Quartus/Verilog/CRD500)

文章出處:【微信號:杜勇FPGA,微信公眾號:杜勇FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

信號發生器電路簡析

信號發生器電路簡析

評論