本文主要給大家分享一下PCIe5.0的發(fā)展歷程、以及在設計、仿真中一些挑戰(zhàn)和如何進行仿真。--蔣修國

1、PCIE 發(fā)展歷程及PCIE 5.0的發(fā)布

作為PC系統(tǒng)中最重要的總線, PCI Express由Intel于2001年提出,用于替代PCI總線,以滿足更高的帶寬和吞吐量需求。

由上面的圖表可以看到,為了滿足日益增長的信息傳遞速率,每一代PCIE標準在速度上都幾乎是成倍增長。

目前,由于 PCIE 4.0擁有相較于前代PCIE 3.0兩倍的16GT/s傳輸速率,其被廣泛應用于超算,企業(yè)級高速存儲,網(wǎng)絡設備等產品中。而去年年中,AMD發(fā)布了支持PCIE4.0的7nm銳龍3000系列處理器,正式將PCIE4.0帶入了消費級平臺。

隨著人工智能技術的飛速發(fā)展,對運算能力的需求不斷提升,高速總線也面臨著更大的挑戰(zhàn)。因此,在PCIE 4.0發(fā)布僅僅兩年后,PCI-SIG便于2019年5月發(fā)布了PCIE 5.0規(guī)范。相比較之前PCIE 4.0的16GT/s,PCIE5.0 將信號速率翻倍到了32GT/s,x16雙工帶寬更是接近128GB/s。極高的信號速率,使得PCIE5.0能夠更好的支持對吞吐量要求高的高性能設備,如用于AI的GPU,網(wǎng)絡設備等等。

2019年底,Intel便出貨了支持PCIE 5.0的Agilex FPGA,也拉開了PCIE 5.0時代的大幕。

2、PCIE 5.0主要指標

由于速率的翻倍,PCIE 5.0在均衡,損耗等指標上,與前代均有較大差別。

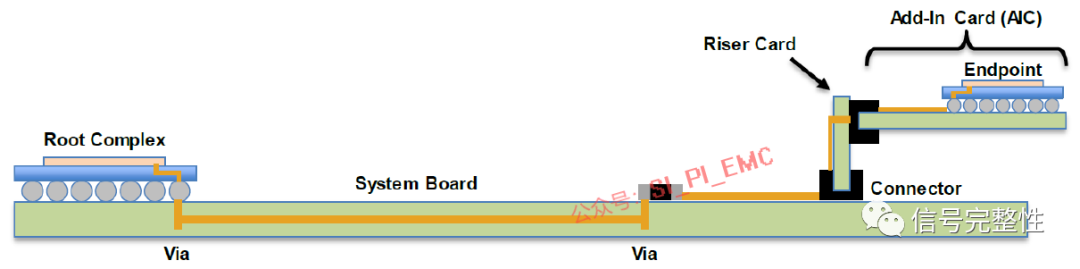

(1)、拓撲結構

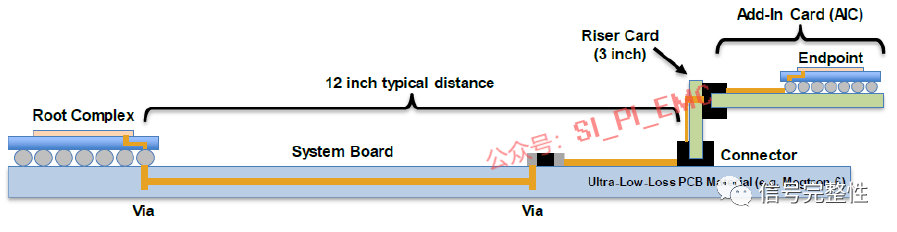

上圖展示了基本的雙連接器PCIE拓撲結構,這種結構被廣泛應用于服務器、存儲和加速器系統(tǒng)。

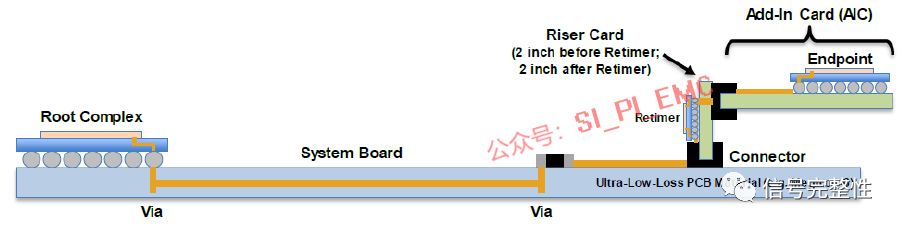

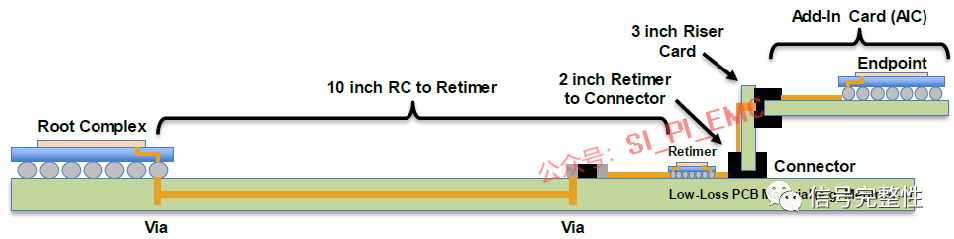

在PCIE 5.0中,當線路損耗過大,或使用多個連接器時,可以在信號拓撲中加入Re-timer以提高系統(tǒng)信號質量。關于加入Re-timer后的拓撲結構,在之后的章節(jié)會有具體的介紹。

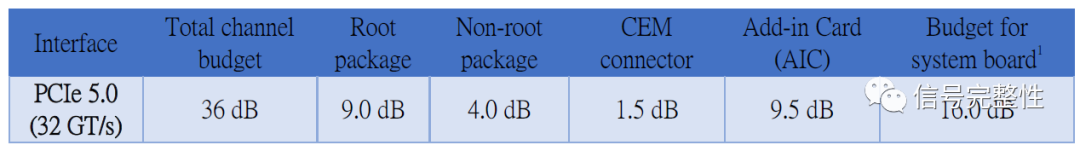

(2)、損耗

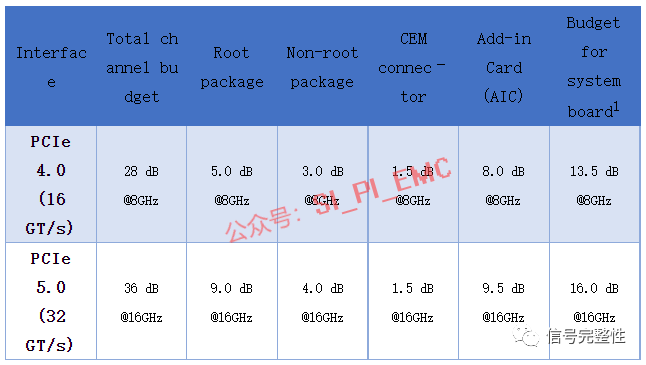

上述拓撲結構中包括各種損耗組件,而PCIe 5.0已經(jīng)為這些組件制定了如下的損耗預算。可以看到,整體通道的損耗在16GHz時不能高于36dB。

1System Board budget includes the baseboard,riser card, the baseboard-to-riser-card, and PCIe card electromechanical (CEM)form factor connectors.

(3)、均衡

PCIE 5.0在發(fā)射端和接收端都使用了均衡技術來提高信號質量。

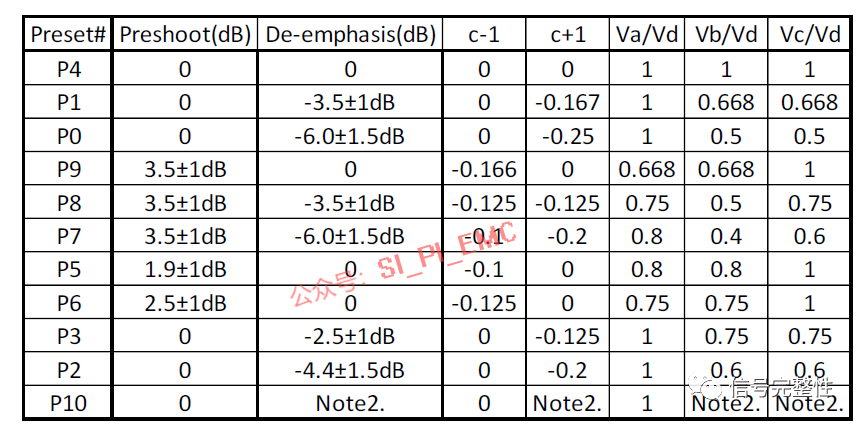

A.Tx EQ

在發(fā)射機端,PCIE 5.0沿用了PCIE 4.0的三階FIR濾波器(如下圖所示),通過對信號高頻分量的抬高和低頻分量的減少來彌補這一影響。

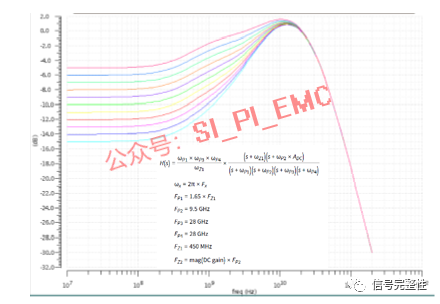

B.RX EQ

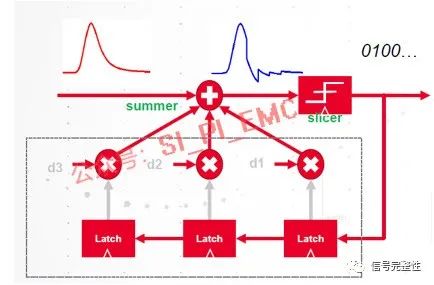

與Tx均衡不同,在接收端,PCIE 5.0對PCIE 4.0的均衡進行了升級,二階CTLE和三階DFE被用來替換前代的一階CTLE和二階DFE,以應對更高的信號速率,使閉合的眼圖張開。通過CTLE可以減小由更高頻通道損耗造成的影響。而DFE則可以進一步減少ISI帶來的影響。

2-order CTLE

3-tap DFE

通過使用以上技術,也促使PCIE 5.0在PCIE 4.0的基礎上實現(xiàn)了速度翻倍(這并不是是唯二的技術),同時,其信號延遲和編碼開銷也大幅優(yōu)化。

3、PCIE 5.0 設計面對的挑戰(zhàn)

(1)、無源通道設計

在2.2中介紹到PCIE 5.0對整體信道的損耗有嚴格的要求。下表中對比了PCIE4.0在16GT/s速率下,與PCIE 5.0在32GT/s速率下的損耗要求。

可以看到,雖然PCIE 5.0的速率提高了一倍,損耗要求卻沒有下降太多。這意味對設計的損耗控制要求提高了幾乎一倍。使用低損耗或超低損耗的材料的固然使減少損耗的一個方法,但其在降低了損耗的同時,也大大提高了產品的成本。如果能夠在使用較低成本材料的同時,通過對疊層,傳輸線結構的調整,達到符合要求的通道性能,無疑能使產品獲得更大的競爭力。平衡成本與性能之間的關系,將成為工程師們不得不面對的挑戰(zhàn)。

(2)、Repeater使用

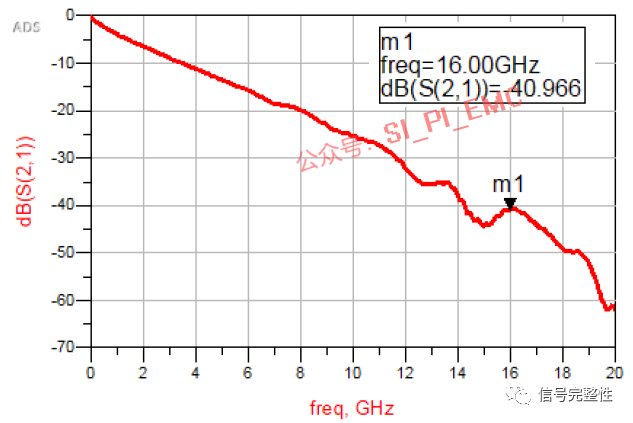

PCIe 4.0對通道損耗的要求是8GHz小于28dB,而PCIE5.0則是16GHz小于36dB,若大于這些值,接收機不能保證可以正確地解出信號。控制損耗固然是解決方法之一,但對于損耗過大的設計,受到產品結構,尺寸和成本的限制,留給工程師的優(yōu)化空間往往十分有限,因此Repeater被使用來給予看似絕望的設計一線生機。

Repeater的目的是為了避免抵達接收機的信號惡化太嚴重以至于無法被正確識別,在信道中提前對信號做處理。以PCIe 5.0為例,因成本的考慮不能用太貴的板材,若初步的通道設計差損48dB@16GHz,為了讓信號可以正確地傳送,可以選擇在通道中間加上Repeater,這樣就可以把通道的設計拆成兩半,Repeater和RX各分擔24dB@16GHz的差損。關于Repeater的使用我們會在后面作更深入的探討。

Repeater是由一個RX加上TX芯片所組成,而依信號處理方式的不同分為兩類,Retimer和Redriver。

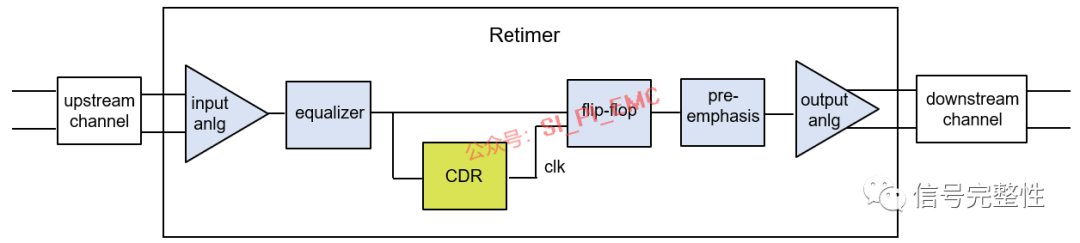

A.Retimer

有CDR(Clock Data Recovery,時鐘恢復),若TX到該Retimer之前的通道設計符合Retimer的規(guī)范,則信號可以被正確的還原,之前的通道損耗和抖動都可以被Retimer消除,因此就像TX的位置被移動到Retimer,對SI工程師來說,信號就可以走得更遠了。

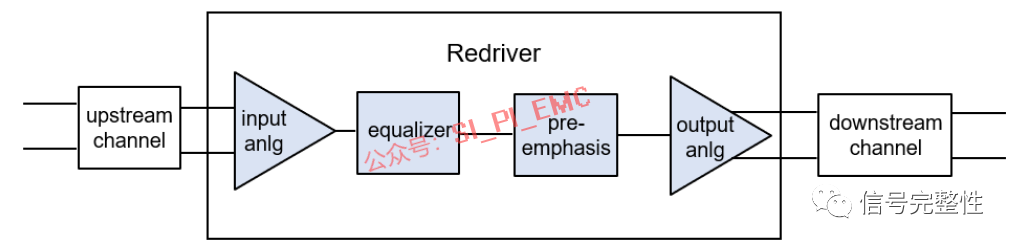

B. Redriver

沒有CDR,因此只能補償信號的衰減,無法去除抖動。

4、應對PCIE5.0設計挑戰(zhàn)

針對以上提到的設計難題,就需要一套非常完整的仿真方案來解決。

(1)、無源通道設計

在前面介紹到,無源通道的損耗是PCIE 5.0設計中的一大挑戰(zhàn)。為了平衡成本與性能,工程師需要進行大量的預研,在layout之前評估出適合的PCB材料,傳輸線和疊層結構等。在使設計符合協(xié)議要求的同時,盡可能降低產品的成本。

而針對設計完成的layout,工程師需要準確的提取其中的S參數(shù),用于驗證通道損耗是否符合設計要求。由于PCIE 5.0的奈奎斯特頻率高達16GHz,工程師需要一款能夠在高頻情況下準確高效提取通道S參數(shù)的工具。

在ADS中,CILD和SIPro兩個工具,可以分別滿足layout前、后的設計驗證要求。

A.傳輸線結構設計(Pre-layout)

工程師在正式layout之前,需要預先確定設計的疊層,材料和走線結構。為了控制產品的成本,超低損耗材料往往無法很普遍的被使用。受到材料的約束,工程師更需要通過合理的疊層和線寬,線間距設置,降低通道的損耗。

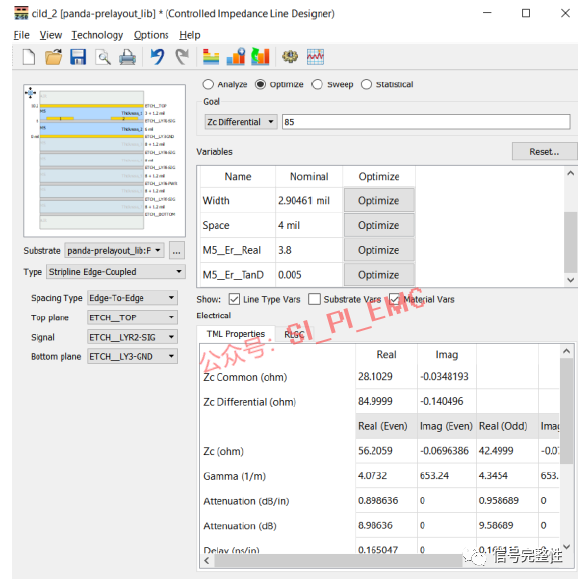

這里,以Dk=3.8, Df=0.005的低損耗材料,core/pp介質厚度3/6mil,85ohm阻抗為例,對比不同的傳輸線線寬與線間距對損耗的影響。

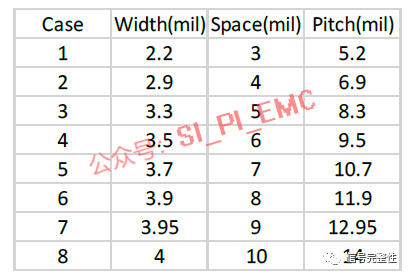

在ADS中,CILD是專門用于在layout前構建傳輸線結構,并仿真其主要參數(shù)的工具。在CILD中,可以通過設定目標阻抗,使用優(yōu)化模式自動優(yōu)化出符合阻抗要求的線寬和線間距。如下圖中,統(tǒng)計出了8種不同的線寬及線間距組合。

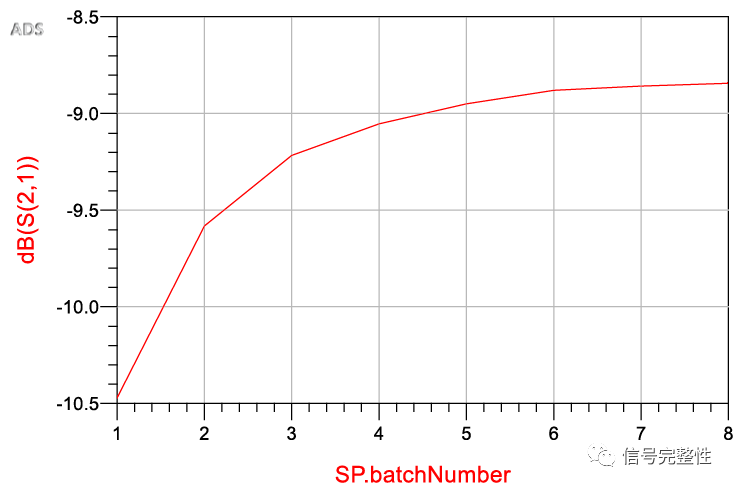

CILD的傳輸線模型還可以導入ADS原理圖中,通過Batch Simulation對各種線寬線間距的組合進行掃描。如下圖所示,對8種傳輸線結構都進行了仿真,得到了16GHz時的損耗。可以發(fā)現(xiàn)隨著線寬的增寬,傳輸線的損耗逐步下降。4/10的情況下,相較2.2/3損耗下降了超過1.5dB。 考慮到case 4~7的pitch雖然增加了近50%,但是損耗僅減小了0.3dB。選擇Case4或Case5的情況進行l(wèi)ayout,既減少了損耗,又可以保證足夠的走線空間。

除了線寬與線間距,CILD也可以考慮材料參數(shù)和疊層的變化。通過ADS CILD的使用,用戶可以對傳輸線結構進行快速評估,獲得設計參考。

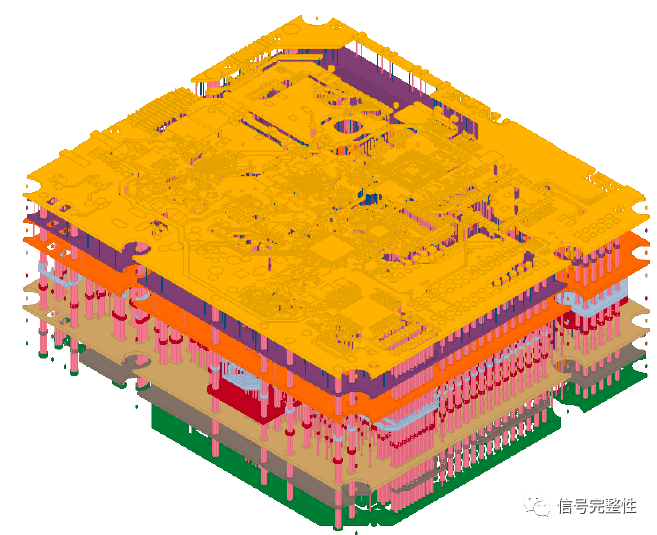

B.Layout EM驗證(Post-layout)

完成layout之后,工程師需要使用電磁仿真工具提取PCB的S參數(shù)對設計進行驗證。由于PCIE 5.0的高速率,工程師使用的電磁仿真工具需要能在高頻段也能快速準確提取出S參數(shù)。同時,設計中往往會使用背鉆來解決過孔stub的問題,因此也要求電磁仿真器能準確提取該部分信息。

ADS SIPro是一款專用于PCB仿真的電磁仿真工具。其使用獨有的混合算法,可以快速提取信號走線(包含過孔)的頻域模型,驗證設計完成的layout性能。這一頻域模型可以直接轉換成ADS 的原理圖,用于電路仿真,如時域瞬態(tài)仿真,通道仿真等。同時,ADS 提供了過孔設計工具ViaDesigner,使用FEM進行過孔結構的仿真設計。

(2)、Repeater應用

前文提到過Repeater的工作原理,工程師往往需要判斷Repeater的使用時機和方式。通過ADS 通道仿真器,可以對是否使用Repeater以及Repeater的擺放位置進行規(guī)劃與驗證。

A.是否需要使用Repeater

這里提供兩種判斷方式,方法I比較簡單但較粗糙,方法II適用于獲得芯片的AMI模型的情況,可以得到很接近真實的眼圖,建議初期先用方法I做系統(tǒng)規(guī)劃,再用方法II來驗證。

I.損耗評估法

通過S參數(shù)仿真,比較通道損耗(包括封裝)和PCIe規(guī)范的損耗標準,若通道損耗超過標準,則建議使用Repeater。

II.統(tǒng)計眼圖法

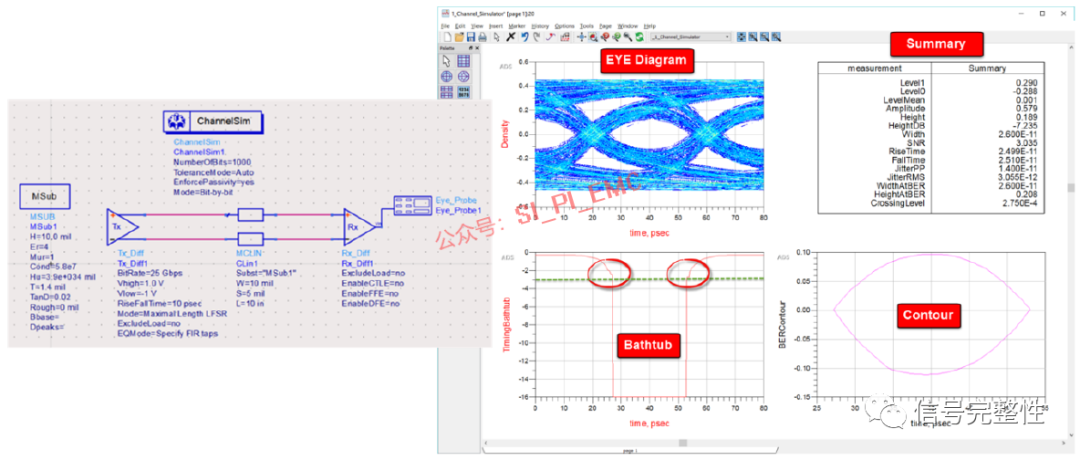

ADS通道仿真器(ChannelSim),用于分析經(jīng)過通道后的信號質量。通道仿真器具有兩種模式,Bit-by-bit和Statistical,是目前串行接口鏈路的主流仿真工具。

以下探討是否有AMI模型的判斷方式。

-沒有AMI模型

把通道的S參數(shù)帶入通道仿真器(ChannelSim),并設定PCIe協(xié)會對芯片規(guī)范的Jitter和EQ(De-emphasis, CTLE, DFE),找出最好的EQ組合,若該組合不能符合協(xié)會訂定的眼圖張開標準(5.0, 眼高15mV,眼寬0.3UI),建議使用Repeater。

-有AMI模型

不用自己設定Jitter和EQ,且眼圖張開標準有可能會比協(xié)會訂定的還寬松(例如眼高10mV,眼寬0.2UI,比協(xié)會規(guī)范的EYE MASK還小),這取決于RX芯片的算法能力,建議參考RX AMI模型的應用文件。若仿真得到的眼圖張開不能符合該RX AMI建議的值,建議使用Repeater。

B.Repeater的擺放位置

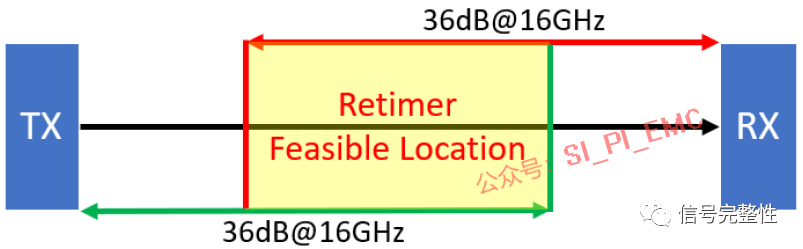

Retimer

由于Retimer送出的信號已經(jīng)將信號時鐘對準,可以把Retimer位置視為新的TX位置,并針對協(xié)會對損耗的規(guī)范來擺放Retimer。通過損耗評估法,得到以下的黃色區(qū)間是適合擺放Retimer的位置,在該區(qū)間符合TX to Retimer和Retimer to RX之間的通道差損小于36dB@16GHz。

一旦決定Retimer的位置后,可以將兩段S參數(shù)(TX to Retimer和Retimer to RX)連同Retimer AMI模型用通道仿真器來判斷最后RX的眼圖是否符合該RX的要求,若不符合要求,可以前后調整一下Retimer位置后,再用通道仿真驗證,直到RX的眼圖符合該RX的要求為止。

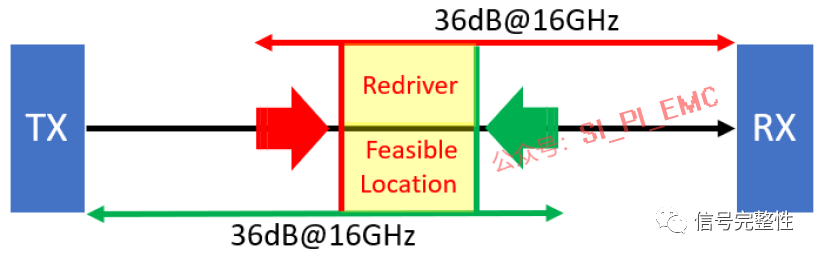

Redriver

由于沒有CDR,因此在評估時無法將Redriver的位置視為新的TX位置,因為從Redriver送出的信號會帶有之前信道累積的Jitter。有了這樣的認知,我們在判斷Redriver的位置就應該更加保守,類似下圖。

確定位置后,一樣也需要透過信道仿真器來判斷RX的眼圖是否符合RX規(guī)范。

Repeater加在Baseboard還是Riser Card上?

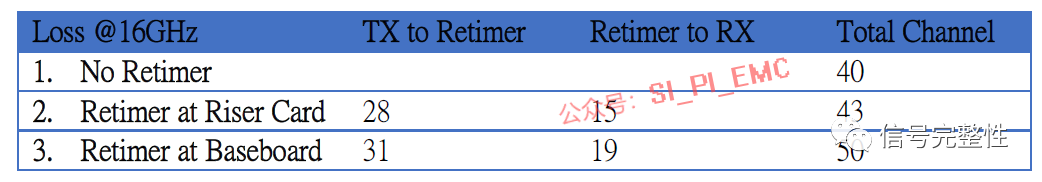

以下兩種常見的Repeater擺放位置(Topology 2 and 3),最后仿真結果也都遠優(yōu)于協(xié)會規(guī)范,這表示在系統(tǒng)設計上還有許多優(yōu)化空間,例如可以選擇較低成本的板材,或是走線可以走得更長。

Topology 1 - 無Retimer,Baseboard用Ultra-Low-Loss板材

Topology 2 - Retimer加在Riser card上,Baseboard用Ultra-Low-Loss板材

Topology 3 - Retimer加在Baseboard上,Baseboard用Low-Loss板材

(5)、PCIe 5.0仿真實例

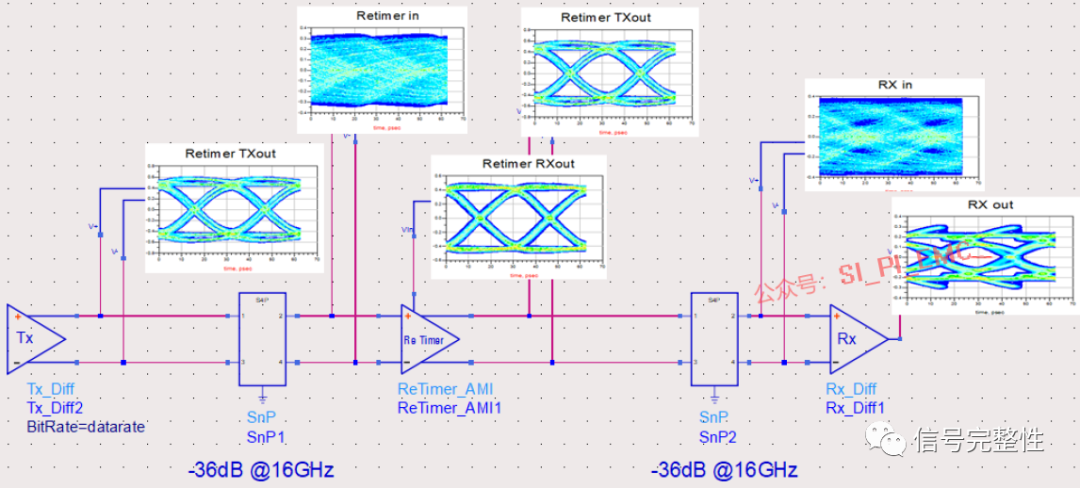

以下是我們基于PCIe 5.0的規(guī)范設定的Retimer測試模板。通過仿真結果我們可以看到,即使進到Retimer前的眼圖已經(jīng)完全關閉(Retimer in),但通過CDR以及均衡器的處理,再次送出張開的眼睛(Retimer TXout),來協(xié)助RX正確地顯示眼圖(RX out)。

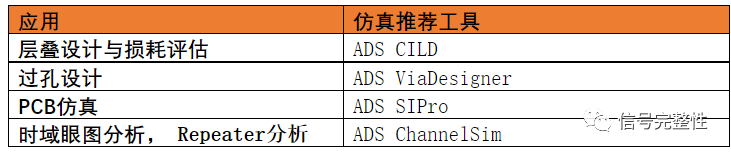

(6)、PCIe5.0仿真推薦配置

審核編輯:湯梓紅

-

仿真

+關注

關注

51文章

4234瀏覽量

135284 -

PCI

+關注

關注

5文章

678瀏覽量

131413 -

總線

+關注

關注

10文章

2947瀏覽量

89324 -

PCIe

+關注

關注

16文章

1322瀏覽量

84641 -

PCIe5.0

+關注

關注

0文章

29瀏覽量

1597

原文標題:PCIe 5.0 設計面臨的挑戰(zhàn)以及仿真案例

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

硬盤開啟PCIe 5.0時代

移動電視射頻技術面臨什么挑戰(zhàn)

機器開發(fā)人員面臨哪些軟件挑戰(zhàn)以及硬件挑戰(zhàn)?如何去應對這些挑戰(zhàn)?

PCIe 4.0 SSD尚未起飛,就要迎戰(zhàn)速度翻倍的5.0

PCIe 5.0時代正式拉開序幕

什么是 PCIe 5.0? PCIe 5.0規(guī)范以及挑戰(zhàn)

microchip全新的PCIe 5.0交換芯片怎么樣

是德科技發(fā)布新款端到端的PCIe5.0/6.0測試解決方案

泰克PCIe Gen 5 Tx一致性測試解決方案

PCIe 5.0之PCB設計及挑戰(zhàn)

PCIe 5.0 SSD不用風扇會怎么樣?

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

PCIe 5.0設計面臨的挑戰(zhàn)以及仿真案例

PCIe 5.0設計面臨的挑戰(zhàn)以及仿真案例

評論