作者:David Brandon and John Cavey

殘余相位噪聲測量消除了外部噪聲源(如電源或輸入時鐘)的影響,而絕對相位噪聲測量則包括來自這些源的噪聲。殘余相位噪聲設置可隔離并測量器件的附加相位噪聲。利用這些信息,設計人員可以選擇信號鏈中的單個器件,以滿足整個系統的相位噪聲要求。本文包括時鐘器件的相位噪聲圖,以突出顯示殘余相位噪聲設置的屬性。它還演示了如何使用器件的附加相位噪聲來識別信號鏈中噪聲相關問題的來源。

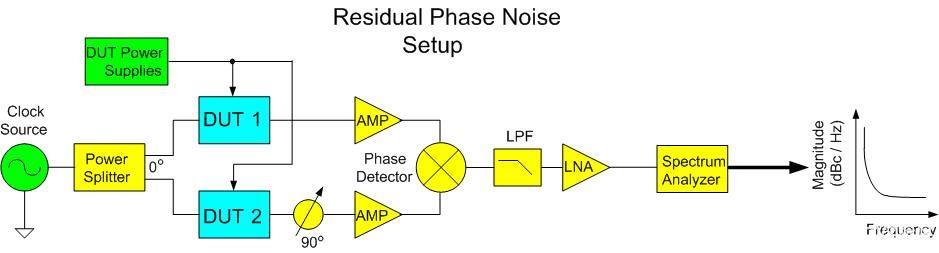

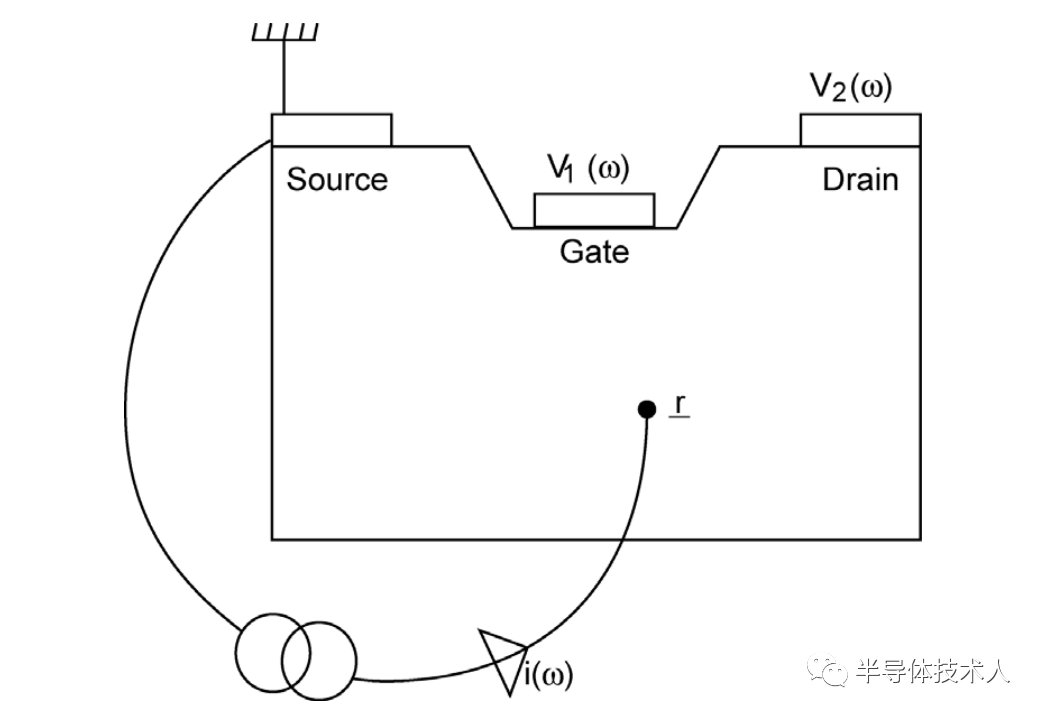

圖1顯示了用于測量被測器件(DUT)的加性相位噪聲的設置。請注意,使用了兩個 DUT;每個都連接到一個公共電源和輸入時鐘。這些常見噪聲源引起的相位噪聲在每個DUT輸出端都是相關的。輸出相位噪聲可以通過簡單地將鑒相器建模為增益為K的模擬乘法器來得出帕金森:

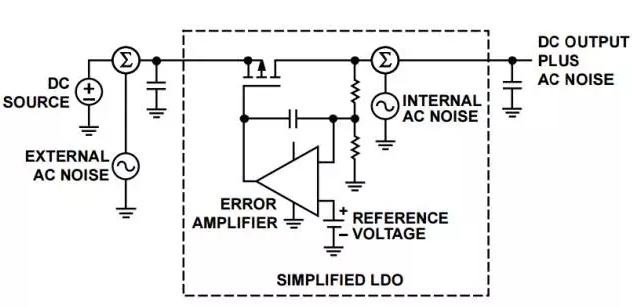

其中 E1 是放大的 DUT1 輸出信號,E2是放大和延遲的 DUT2 輸出信號,EC1和 EC2是信號功率,θM1和 θM2是相位噪聲的幅度,ΩC是載波頻率,ωM是失調頻率。疊加適用,因此在考慮來自外部源的相位噪聲時,可以忽略DUT固有的相位噪聲。如果 DUT1 和 DUT2 具有相同的過量相傳遞函數,則 θ 的部分M1由于時鐘源和電源等于θ的部分M2由于通用的時鐘源和電源。這種現象,即供應推動,簡單地描述為:

這樣,相位調制的幅度由電源上的電壓噪聲和KP(以弧度/V為單位的推力增益)的乘積給出。如果DUT1和DUT2具有等效的推力增益,理論上這些噪聲源在鑒相器的輸出端被消除,只留下兩個DUT的不相關噪聲用于測量。

固有的DUT噪聲可以通過一些額外的假設來確定。由于器件噪聲引起的均方根相位誤差通常非常小,因此我們可以使用小角度近似將輸出載波的表達式重寫為:

鑒相器的輸出已經解調,因此可以稱為基帶信號。一旦確定了鑒相器增益和輸入信號功率,就可以計算出實際相位噪聲,假設放大器相位噪聲貢獻可以忽略不計。每個DUT固有的噪聲是不相關的,因此它們的貢獻相等,均方根和是測量的輸出相位噪聲。因此,我們從頻譜分析儀測量的相位噪聲中減去3 dB(以dBc/Hz為單位),以確定每個DUT的貢獻。這表示相位噪聲功率相對于信號功率:

當進行非常敏感的相位噪聲測量時,放大器的噪聲貢獻可能很大。放大器的殘余相位噪聲是通過從電路中移除DUT1和DUT2并將功率分配器輸出直接施加到放大器來測量的。放大器輸入信號功率的幅度和壓擺率必須與實際的DUT輸出信號相似。使用上述程序,從測量的DUT相位噪聲中減去測量的放大器相位噪聲,以獲得精確的DUT相位噪聲。同樣,放大器的增益和噪聲系數必須盡可能相似。

請注意,需要時鐘的 DUT 將具有具有一定噪聲量的前端放大器。因此,由于放大器輸入端的閾值不確定性,具有低壓擺率的時鐘源可能會無意中增加DUT的相位噪聲貢獻。使用正弦時鐘源時,應使用最大允許幅度來最大化壓擺率。

圖1.殘余相位噪聲測量設置。

測試設置的基本細節

使用圖 1 中的測試設置,兩個具有相同部件號的 DUT 由單個 1 GHz 源計時。這些器件設置為將時鐘頻率除以四分頻以產生 250MHz 輸出。此外,兩個輸出信號的相對相位偏移了90°(正交),以最小化直流時出現的下變頻信號電平。DUT信號由低噪聲放大器(LNA)放大,以增加測量系統的動態范圍(放大器貢獻的相位噪聲足夠小,可以忽略不計)。放大器輸出被發送到平衡混頻器(鑒相器)。鑒相器混合兩個信號,在其輸出端產生和差積。總和積用低通濾波器濾除。剩余的差積構成下變頻至直流(相位噪聲)的 250MHz 輸出信號。LNA提供了足夠的增益來克服頻譜分析儀的本底噪聲限制。

消除公共時鐘源相位噪聲

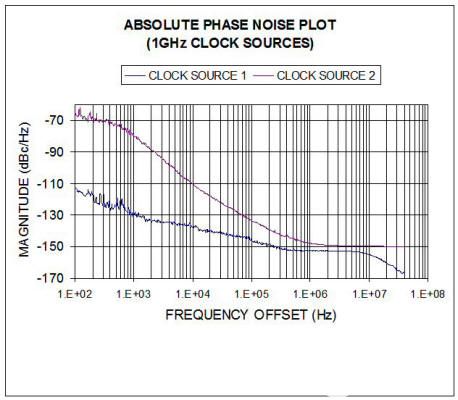

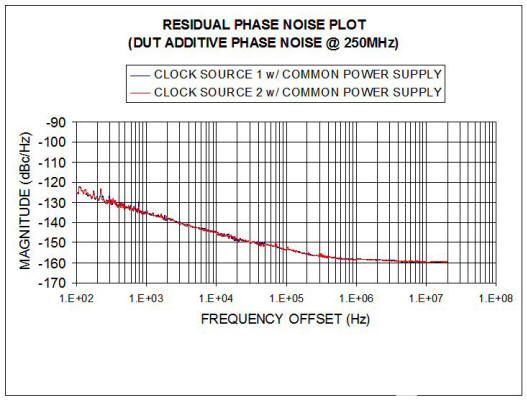

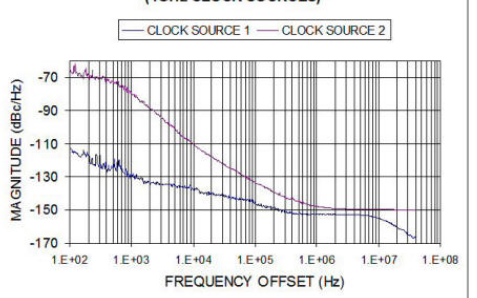

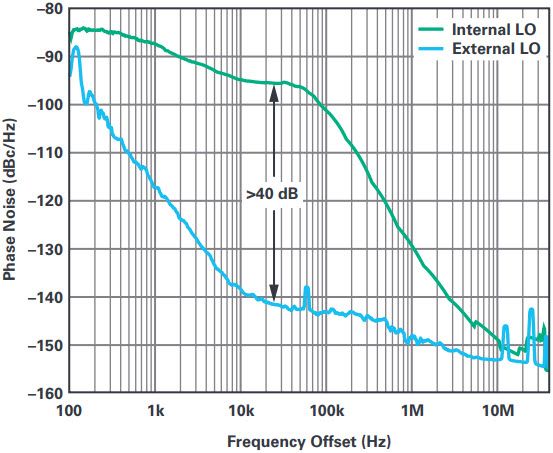

圖2顯示了兩個時鐘源的絕對相位噪聲測量結果,這兩個時鐘源的相位噪聲特性非常不同。理論上,兩個時鐘源都不應影響使用殘余相位噪聲設置測量的DUT加性相位噪聲。圖3證實了這一理論。繪制了兩個獨立的殘余相位噪聲測量值,每個時鐘源一條跡線。兩條走線幾乎重疊,證明殘余相位噪聲設置消除了公共時鐘源噪聲。在絕對相位噪聲設置中,不會消除此噪聲。事實上,如果DUT是理想的(無附加相位噪聲),則其絕對相位噪聲曲線將與圖2中的曲線相匹配(但由于四倍頻率轉換,因此低12 dB)。歸一化為250 MHz載波時,時鐘源2在92 kHz偏移時表現出–1 dBc/Hz相位噪聲,而與時鐘源2相關的測得DUT相位噪聲在135 kHz時為–1 dBc/Hz。因此,殘余相位測量抑制了大約40 dB的輸入時鐘相位噪聲。

圖2.兩個不同時鐘源的絕對相位噪聲測量。

圖3.時鐘源對殘余相位噪聲測量幾乎沒有影響。

消除常見電源噪聲

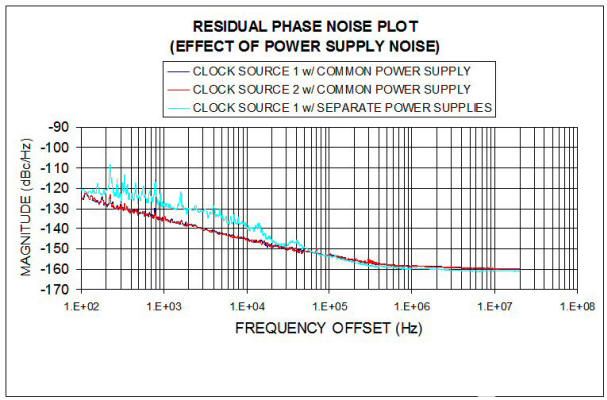

圖 3 使用公共電源連接,如圖 1 所示。圖4顯示了為每個DUT使用單獨的噪聲電源的效果。不相關的電源噪聲會導致近端相位噪聲大幅增加。

圖4.殘余相位噪聲測量可顯示公共電源和獨立電源的影響。

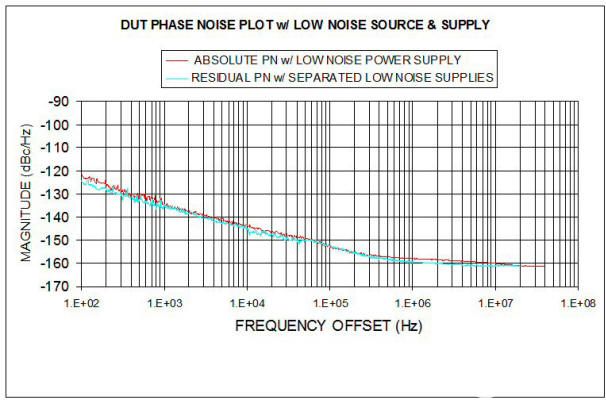

圖5顯示了使用低噪聲電源的絕對相位噪聲測量結果。低噪聲電源的絕對相位噪聲和單獨的低噪聲電源的殘余相位噪聲表現出良好的一致性。電源相位噪聲在殘余相位噪聲測量中被消除,但在絕對相位噪聲測量中不會被消除。

圖5.通過低噪聲電源改善近載波相位噪聲

殘余相位噪聲測量是一種有價值的技術,用于識別作為系統設計一部分的單個組件的相位噪聲貢獻。使用這種方法,外部噪聲源(如輸入時鐘和電源)在每個DUT輸出端相互關聯,因此可以有效地消除。此外,通過對這些元件執行額外的殘余相位噪聲測量,可以考慮DUT殘余噪聲測量中使用的緩沖器或放大器的相位噪聲貢獻。結合殘余和絕對相位噪聲測量是識別系統設計中主要噪聲源的有效方法。所提供的測量數據在分頻器上獲取,展示了殘余相位噪聲測量的概念和實用性,并量化了噪聲輸入時鐘和電源的影響。通過此評估,系統設計人員可以根據實際測量數據得出輸入時鐘源和電源的規格。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18244瀏覽量

254823 -

放大器

+關注

關注

145文章

14089瀏覽量

216097 -

濾波器

+關注

關注

162文章

8051瀏覽量

180840

發布評論請先 登錄

電路中常見的內部噪聲及外部噪聲源

殘余相位噪聲測量從外部噪聲源中提取DUT噪聲

殘余相位噪聲測量從外部噪聲源中提取DUT噪聲

評論