介紹

本應用筆記概述了在DS3184中配置時鐘速率適配器(CLAD)功能。此處的信息適用于其他Maxim器件,如DS3181、DS3182和DS3183。DS318x(DS3181、DS3182、DS3183和DS3184)將ATM小區/HDLC數據包處理器與DS3/E3成幀器和LIU集成在一起,將ATM小區或數據包映射/解映射為最多四條DS3/E3物理銅線,每個端口具有DS3成幀(C位或M23)、E3成幀(G.751或G.832)或清通道數據流。

DS318x中的CLAD用于從CLKA引腳上的單個時鐘基準輸入創建多個內部所需的DS3、E3或STS-1時鐘。應用于 CLKA 的時鐘頻率必須是以下之一:

DS3 (44.736兆赫)

E3 (34.368兆赫)

STS-1 (51.84兆赫)

給定其中一個時鐘,將生成另外兩個時鐘。如果需要,內部生成的時鐘可通過輸出引腳CLKB和CLKC驅動,以供外部使用。

包層功能特點

DS318x的CLAD可以從單個輸入基準時鐘產生內部所需的DS3 (44.736MHz)、E3 (34.368MHz)和STS-1 (51.84MHz)時鐘。該輸入參考時鐘可以是 51.84MHz、44.736MHz 或 34.368MHz。這些內部推導的時鐘可用作LIU和抖動衰減器的基準,并可在片外傳輸以供外部系統使用。

配置包層

如果使用DS318x的LIU,CLAD為DS318x的接收LIU提供時鐘。DS318x的CLAD由GL中的CLAD位配置。CR2 寄存器。在這種情況下,用戶必須向CLKA引腳提供DS3、E3或STS-1時鐘。

用戶必須向CLKA引腳提供三種頻率速率(DS3、E3、STS-1)中的至少一種。CLAD[3:0] 位通知 PLL 施加到引腳的頻率。圖1所示為DS318x的CLAD模塊。

圖1.用于DS318x的復合模塊。

應用于LIU和發射器的CLAD輸出時鐘的選擇由FM位(位于PORT。CR2)。CLAD 提供了最大的靈活性。應用程序可以提供三種時鐘速率中的任何一種,并使用 CLAD 提供所需的時鐘速率。

CLAD 也可以禁用,所有三個時鐘都使用 CLKA、CLKB 和 CLKC 引腳作為輸入從外部供電。當CLAD被禁用時,三個參考時鐘(DS3、E3和STS-1)將施加到CLKA、CLKB和CLKC引腳上。如果不需要這三個頻率中的任何一個,則無需將其施加到CLAD時鐘引腳。

CLAD 的 CLAD 模式輸入由 CLAD[3:0] 控制位(位于 GL.CR2寄存器),用于確定哪些引腳是輸入和輸出,以及哪個引腳上的時鐘速率。詳情請參閱表 1。

當 CLAD[3:0] = 00XX 時,PLL電路被禁用,輸入時鐘引腳(CLKA、CLKB和CLKC)上的信號用作內部LIU參考時鐘。當 CLAD[3:0] = (01XX 或 10XX 或 11XX) 時,將啟用無、一個或兩個 PLL 電路,以生成所需的時鐘,具體取決于位于 PORT 中的 CLAD[3:0] 位、成幀模式 (FM[5:0]) 和線路模式控制位 (LM[2:0]。CR2)。

線路模式位選擇主端口接口操作模式。如果CLAD輸出時鐘引腳或LIU的參考時鐘不需要時鐘速率,則用于產生該時鐘的PLL將被禁用并斷電。

復合配置寄存器

下面介紹了配置 CLAD 所需的兩個寄存器。

寄存器名稱: GL.CR2 寄存器說明: 全局控制寄存器 2

寄存器地址: 004h

| 位# | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| 名字 | - | - | - | G8KRS2 | G8KRS1 | G8KRS0 | G8K0S | G8KIS |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 位# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名字 | - | - | - | - | CLAD3 | CLAD2 | CLAD1 | CLAD0 |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 3 到 0:包層 IO 模式 [3:0](包層 [3:0])

這些位控制 CLAD 時鐘 IO 引腳 CLKA、CLKB 和 CLKC。這些寄存器位控制哪個時鐘用于從LIU中的線路中恢復RX時鐘。有關更多詳細信息,請參閱表 1。

| GL..CR2 | CLKA PIN | CLKB 引腳 | CLKC PIN |

| 包層[3:0] | |||

| 00 XX | DS3時鐘輸入 | E3 時鐘輸入 | STS-1 時鐘輸入 |

| 01 00 | DS3時鐘輸入 | 低輸出 | 低輸出 |

| 01 01 | DS3時鐘輸入 | E3 時鐘輸出 | 低輸出 |

| 01 10 | DS3時鐘輸入 | 低輸出 | STS-1 時鐘輸出 |

| 01 11 | DS3時鐘輸入 | STS-1 時鐘輸出 | E3 時鐘輸出 |

| 10 00 | E3 時鐘輸入 | 低輸出 | 低輸出 |

| 10 01 | E3 時鐘輸入 | DS3時鐘輸出 | 低輸出 |

| 10 10 | E3 時鐘輸入 | 低輸出 | STS-1 時鐘輸出 |

| 10 11 | E3 時鐘輸入 | STS-1 時鐘輸出 | DS3時鐘輸出 |

| 11 00 | STS-1 時鐘輸入 | 低輸出 | 低輸出 |

| 11 01 | STS-1 時鐘輸入 | E3 輸出 | 低輸出 |

| 11 10 | STS-1 時鐘輸入 | 低輸出 | DS3時鐘輸出 |

| 11 11 | STS-1 時鐘輸入 | DS3時鐘輸出 | E3 時鐘輸出 |

CLAD 為接收 LIU 提供參考時鐘。接收 LIU 根據用戶通過成幀模式 (FM) 位選擇的模式選擇時鐘頻率。FM 位選擇主要的成幀操作模式。如果使用端口選擇,則CLAD輸出也可用作傳輸時鐘源。CR3.CLADC寄存器位。

寄存器名稱:端口。CR3

寄存器說明: 端口控制寄存器 3

寄存器地址: (0, 2, 4, 6)44h

| Bit # | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

| Name | - | - | RCLKS | RSOFOS | RPFPE | TCLKS | TSOFOS | TPFPE |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Name | P8KRS1 | P8KRS0 | P8KREF | LOOPT | CLADC | RFTS | TFTS | TLTS |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

位 3:CLAD 傳輸時鐘源控制 (CLADC)

該位用于使CLAD時鐘成為內部傳輸時鐘的源。此位的功能以其他控制位為條件。

0 = 根據需要

將 CLAD 時鐘用于傳輸時鐘 1 = 不要將 CLAD 時鐘用于傳輸時鐘(如果未啟用環回,則 TCLKIn 是源)

結論

Maxim DS318x器件可用于創建多個時鐘作為LIU參考時鐘或為用戶應用發送時鐘。創建和發送多個時鐘的決定應根據設計人員在其應用板中的需求做出。

審核編輯:郭婷

-

Maxim

+關注

關注

8文章

859瀏覽量

88334 -

寄存器

+關注

關注

31文章

5421瀏覽量

123300 -

適配器

+關注

關注

9文章

2024瀏覽量

69290

發布評論請先 登錄

藍牙適配器有什么功能呢?

DS325X、DS316X、DS317X和DS318X中時鐘

DS325X、DS316X、DS317X和DS318X中時鐘

網絡適配器,什么是網絡適配器

光纖適配器是什么_光纖適配器的作用介紹

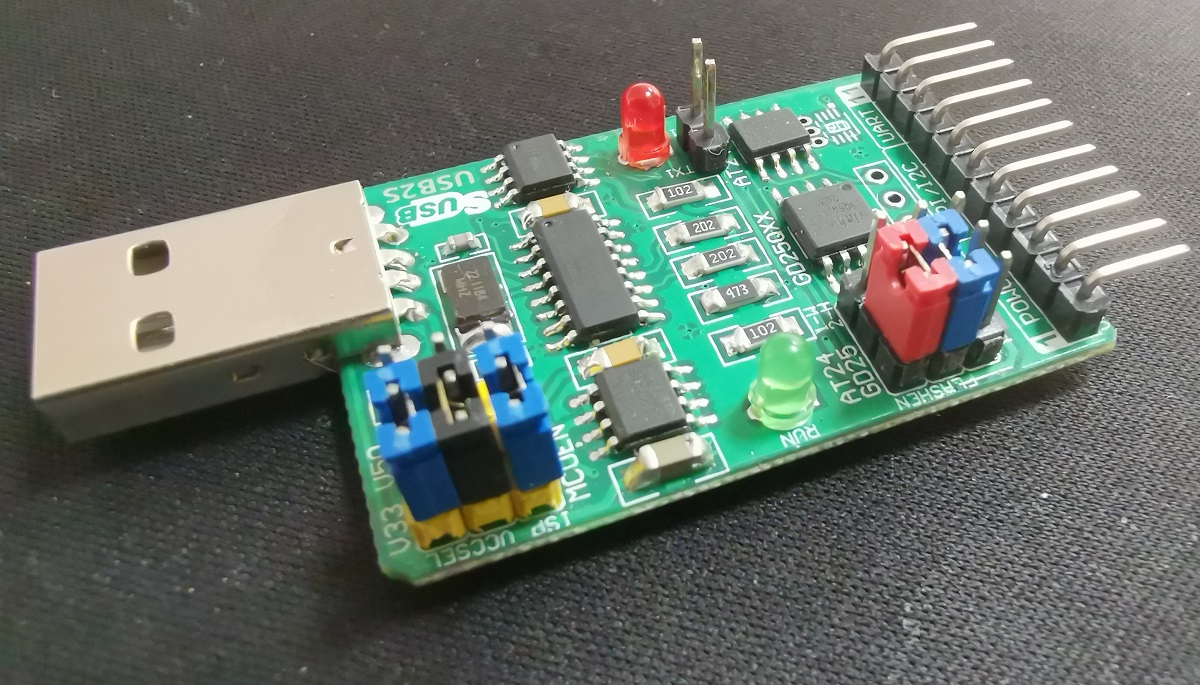

可編程USB轉串口適配器開發板時鐘芯片參數讀取與修改

DS3184 DS3184 - (Maxim Integrated) - 專用 IC

如何配置DS3184中的時鐘速率適配器(CLAD)功能

如何配置DS3184中的時鐘速率適配器(CLAD)功能

評論