02. 源同步時(shí)序系統(tǒng)

針對(duì)普通時(shí)鐘系統(tǒng)存在著限制時(shí)鐘頻率的弊端,人們?cè)O(shè)計(jì)了一種新的時(shí)序系統(tǒng),稱(chēng)之為源同步時(shí)序系統(tǒng)。它最大的優(yōu)點(diǎn)就是大大提升了總線的速度,在理論上信號(hào)的傳送可以不受傳輸延遲的影響。下面我們來(lái)看看這種源同步時(shí)鐘系統(tǒng)的結(jié)構(gòu)。

1.源同步系統(tǒng)的基本結(jié)構(gòu)

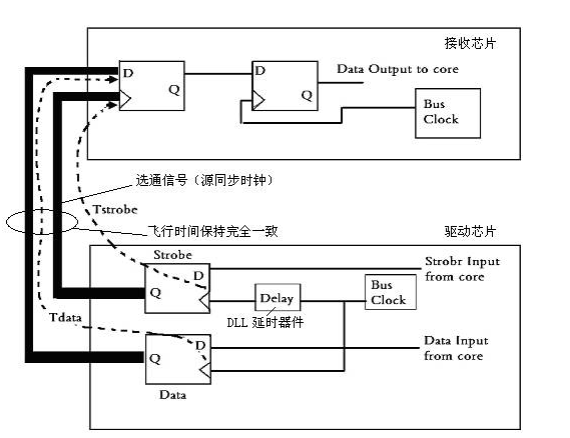

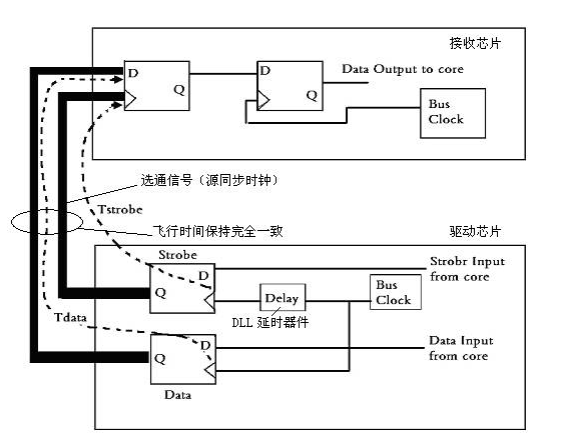

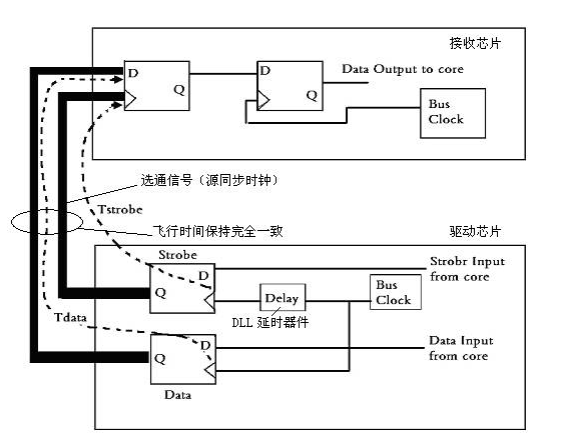

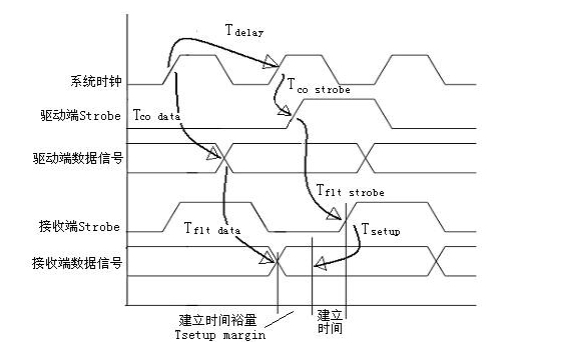

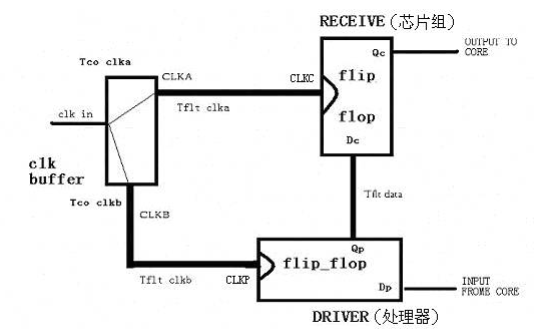

上圖是一個(gè)基本的源同步時(shí)鐘系統(tǒng)的結(jié)構(gòu)示意圖。可以看到,驅(qū)動(dòng)芯片在發(fā)送數(shù)據(jù)信號(hào)的同時(shí)也產(chǎn)生了選通信號(hào)(Strobe),而接收端的觸發(fā)器由該選通信號(hào)脈沖控制數(shù)據(jù)的讀取,因此,這個(gè)選通信號(hào)也可以稱(chēng)為源同步時(shí)鐘信號(hào)。

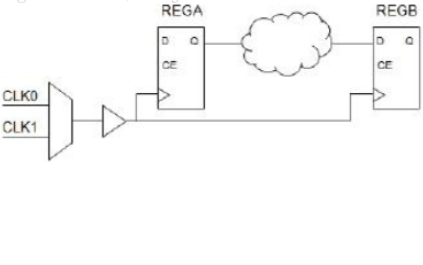

源同步時(shí)鐘系統(tǒng)中,數(shù)據(jù)和源同步時(shí)鐘信號(hào)是同步傳輸?shù)模覀儽WC這兩個(gè)信號(hào)的飛行時(shí)間完全一致,這樣只要在發(fā)送端的時(shí)序是正確的,那么在接收端也能得到完全正確的時(shí)序。整個(gè)系統(tǒng)在時(shí)序上的穩(wěn)定性完全體現(xiàn)在數(shù)據(jù)和選通信號(hào)的匹配程度上,包括傳輸延遲的匹配,器件性能的匹配等等,只要兩者條件完全相同,那么我們就可以保證系統(tǒng)的時(shí)序絕對(duì)正確,而對(duì)系統(tǒng)的最高時(shí)鐘頻率沒(méi)有任何限制。

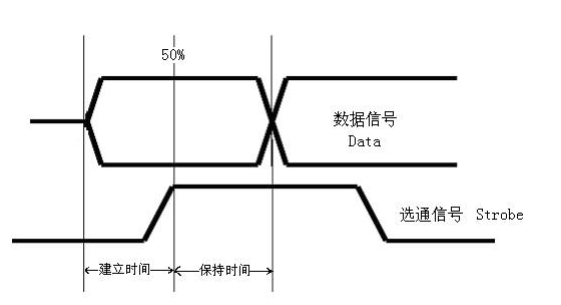

當(dāng)然,對(duì)于任何數(shù)據(jù)接收來(lái)說(shuō),一定的建立和保持時(shí)間都是必須滿(mǎn)足的,源同步時(shí)鐘系統(tǒng)也同樣如此,主要體現(xiàn)在數(shù)據(jù)信號(hào)和選通信號(hào)之間的時(shí)序要求上。最理想的情況就是選通信號(hào)能在數(shù)據(jù)信號(hào)的中央部分讀取,如圖下圖所示,這樣才能保證最充分的建立和保持時(shí)間。

為了保證選通信號(hào)和數(shù)據(jù)信號(hào)相對(duì)保持正確的時(shí)序,在源同步時(shí)鐘系統(tǒng)中是通過(guò)驅(qū)動(dòng)芯片內(nèi)部的數(shù)字延時(shí)器件DLL來(lái)實(shí)現(xiàn)(見(jiàn)下圖),而不是通過(guò)PCB走線來(lái)控制,因?yàn)橄啾容^而言,DLL器件能做到更為精確的延時(shí),同時(shí)還可以受芯片電路控制,調(diào)節(jié)起來(lái)更為方便。

2.源同步時(shí)序要求

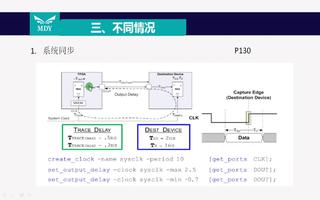

前面已經(jīng)提到源同步時(shí)鐘系統(tǒng)設(shè)計(jì)中最重要的一點(diǎn)就是保證data和strobe信號(hào)之間的偏移(Skew)最小,引起這些誤差的最主要的因素就是實(shí)際系統(tǒng)中各器件的時(shí)序參數(shù)Tco的不同,此外還有布線上引起的差異,為了更好地說(shuō)明這些Skew對(duì)時(shí)序的具體影響,下面我們還是通過(guò)時(shí)序圖分析的方法來(lái)計(jì)算一下源同步時(shí)鐘系統(tǒng)中信號(hào)的建立時(shí)間裕量和保持時(shí)間裕量。

首先考慮建立時(shí)間裕量:

和普通時(shí)序分析的方法一下,我們也是從建立時(shí)間環(huán)的角度考慮,參考下面的結(jié)構(gòu)圖,我們可以作出驅(qū)動(dòng)端和接收端的時(shí)序示意圖(下圖)。

Tdata = Tco_data +Tflt_data

Tstrobe = Tco strobe + Tflt strobe + Tdelay

其中,Tco和Tflt分別代表數(shù)據(jù)/選通信號(hào)在器件的內(nèi)部延遲和信號(hào)傳輸?shù)娘w行時(shí)間,Tdelay是指數(shù)據(jù)信號(hào)和選通信號(hào)之間的延遲,由系統(tǒng)內(nèi)DLL延時(shí)器件決定,圖中假設(shè)為一個(gè)時(shí)鐘周期。

將上式帶入建立時(shí)間裕量的計(jì)算公式:Tsetup margin = Tclk – Tdata– Tsetup可以得到:

Tsetup margin =(Tco strobe + Tflt strobe + Tdelay)- (Tco data+ Tflt data) – Tsetup

如果我們將數(shù)據(jù)和Strobe信號(hào)在器件內(nèi)的延時(shí)差異定義為T(mén)vb;將PCB走線引起的延時(shí)差異定義為T(mén)pcb skew:

Tvb = Tco data– (Tco strobe + Tdelay)

Tpcb skew = Tflt data – Tflt strobe

這樣可以得到一個(gè)簡(jiǎn)單的建立時(shí)間裕量方程:

Tsetup margin = - Tvb – Tsetup – Tpcb skew (1.6.5)

注意:公式1.6.5中Tvb是一個(gè)負(fù)值,從公式中可以看出,如果數(shù)據(jù)和選通信號(hào)的Tco相同的話,其大小就是- Tdelay ,也就說(shuō)明數(shù)據(jù)信號(hào)必須提前于選通信號(hào)發(fā)送。

再考慮保持時(shí)間裕量,如下圖所示,同樣分析可以得到:

再考慮保持時(shí)間裕量,如圖1-6-12,同樣分析可以得到:

Thold margin = (Tco data + Tflt data + Tdelay) – (Tco strobe +Tflt strobe) – Thold

如果定義:Tva = Tco data – Tco strobe + Tdelay 為正值;Tpcb skew定義不變。則保持時(shí)間裕量的計(jì)算公式為:

Thold margin = Tva – Thold – Tpcb skew (1.6.6)

在公式1.6.5和1.6.6中,兩個(gè)重要的參數(shù)是Tvb和Tva,Tvb表示“Valid before”,即數(shù)據(jù)在選通脈沖前有效存在的時(shí)間;Tva表示“Valid after”,指選通信號(hào)脈沖之后數(shù)據(jù)仍然有效持續(xù)的時(shí)間。這兩個(gè)時(shí)序參數(shù)一般都可以在器件的datasheet上會(huì)找到。

和普通時(shí)鐘系統(tǒng)相比,源同步總線在PCB布線的設(shè)計(jì)上反而更為方便,設(shè)計(jì)者只需要嚴(yán)格保證線長(zhǎng)的匹配就行了,而不用太多的考慮信號(hào)走線本身的長(zhǎng)度。當(dāng)然,盡管源同步數(shù)據(jù)傳輸在理論上突破了頻率的限制,但隨著頻率的提高,在控制Skew上也變得越來(lái)越困難,尤其是一些信號(hào)完整性因素帶來(lái)的影響也越發(fā)顯得突出,而且目前的高速系統(tǒng)設(shè)計(jì)中,往往綜合應(yīng)用了普通時(shí)鐘和源同步時(shí)鐘技術(shù),比如對(duì)于地址/控制信號(hào)采用普通時(shí)鐘總線,而高速的數(shù)據(jù)傳輸則是采用源同步總線。這些對(duì)于高速PCB設(shè)計(jì)分析人員來(lái)說(shuō)是一個(gè)非常嚴(yán)峻的挑戰(zhàn)。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613939 -

pcb

+關(guān)注

關(guān)注

4351文章

23405瀏覽量

406612 -

時(shí)序

+關(guān)注

關(guān)注

5文章

397瀏覽量

37772 -

源同步時(shí)序

+關(guān)注

關(guān)注

0文章

2瀏覽量

5278

原文標(biāo)題:FPGA知識(shí)匯集-源同步時(shí)序系統(tǒng)

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA案例解析:針對(duì)源同步的時(shí)序約束

FPGA知識(shí)匯集-FPGA時(shí)序基礎(chǔ)理論

FPGA知識(shí)匯集-FPGA系統(tǒng)時(shí)序理論

FPGA時(shí)序分析

源同步時(shí)序系統(tǒng)之基本結(jié)構(gòu)

ETD第14期:SDR源同步接口時(shí)序約束方法

FPGA沙龍:SDR源同步接口時(shí)序約束方法沙龍精彩內(nèi)容回顧!

FPGA實(shí)戰(zhàn)演練邏輯篇55:VGA驅(qū)動(dòng)接口時(shí)序設(shè)計(jì)之2源同步接口

FPGA時(shí)序約束OFFSET

詳解FPGA的時(shí)序以及時(shí)序收斂

使用時(shí)鐘PLL的源同步系統(tǒng)時(shí)序分析

基于Cadence的源同步時(shí)序仿真

FPGA重要設(shè)計(jì)思想及工程應(yīng)用之時(shí)序及同步設(shè)計(jì)

時(shí)序約束步驟:系統(tǒng)同步與源同步

FPGA時(shí)序約束的常用指令與流程詳細(xì)說(shuō)明

FPGA知識(shí)匯集-源同步時(shí)序系統(tǒng)

FPGA知識(shí)匯集-源同步時(shí)序系統(tǒng)

評(píng)論