module single_port_rom(/*autoarg*/

Outputs

q,

Inputs

clk

);

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 8;

input [ADDR_WIDTH-1:0] addr;

input clk;

output reg [DATA_WIDTH-1:0] q;

reg [DATA_WIDTH-1:0] rom[2**ADDR_WIDTH-1:0];

initial begins

rom);

rom);

end

always @ (posedge clk)begin

q <= rom[addr];

end

endmodule

系統(tǒng)函數(shù)$readmemh和$readmemb分別用來(lái)讀取十六進(jìn)制文件和二進(jìn)制文件。貌似沒(méi)有讀十進(jìn)制的。txt中的數(shù)據(jù)每行一個(gè)不需要逗號(hào)和最后一個(gè)數(shù)據(jù)后面的分號(hào),數(shù)據(jù)格式對(duì)應(yīng)。更多使用可以查詢IEEE的Verilog語(yǔ)法手冊(cè)。例化方式和rom IP一樣可參數(shù)化配置任意大小

single_port_rom

#(

.DATA_WIDTH(DATA_WIDTH),

.ADDR_WIDTH(ADDR_WIDTH)

)

u_sin(/*autoinst*/

// Outputs

.q (dout[DATA_WIDTH-1:0]),

// Inputs

.addr (addra[ADDR_WIDTH-1:0]),

.clk (clk));

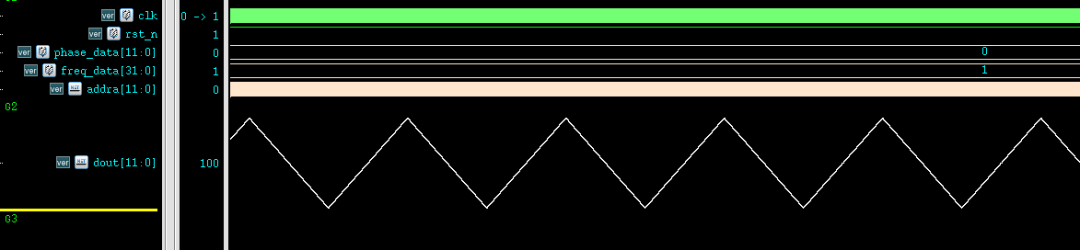

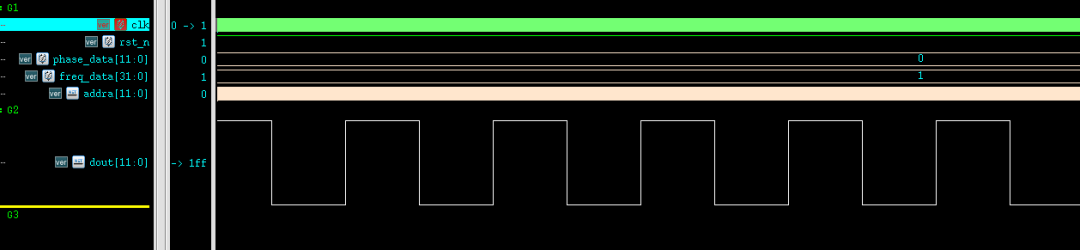

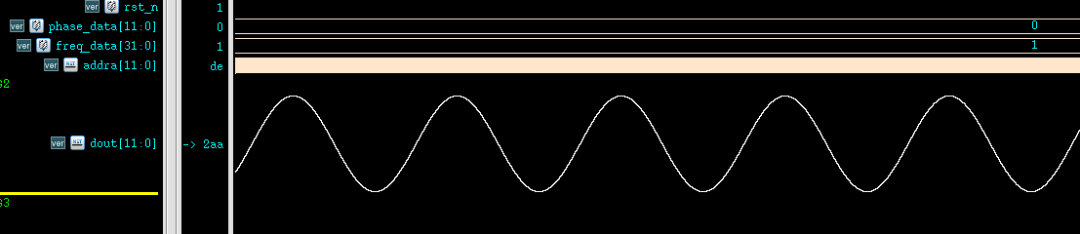

整了三個(gè)波形,仿真能跑起來(lái)。

?

?

?

?

?將設(shè)計(jì)電路參數(shù)化可重復(fù)使用,構(gòu)建自己的代碼庫(kù),搭建起你的數(shù)字積木。

?

?

?

?

?將設(shè)計(jì)電路參數(shù)化可重復(fù)使用,構(gòu)建自己的代碼庫(kù),搭建起你的數(shù)字積木。

審核編輯 :李倩

-

asic

+關(guān)注

關(guān)注

34文章

1242瀏覽量

121960 -

ROM

+關(guān)注

關(guān)注

4文章

578瀏覽量

86977 -

Verilog

+關(guān)注

關(guān)注

28文章

1365瀏覽量

111771

原文標(biāo)題:為了方便仿真這樣寫(xiě)個(gè)ROM

文章出處:【微信號(hào):IP與SoC設(shè)計(jì),微信公眾號(hào):IP與SoC設(shè)計(jì)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Simcenter Flotherm BCI-ROM技術(shù):與邊界條件無(wú)關(guān)的降階模型可加速電子熱設(shè)計(jì)

為了方便仿真這樣寫(xiě)個(gè)ROM

為了方便仿真這樣寫(xiě)個(gè)ROM

評(píng)論