傳統(tǒng)上,同步采樣逐次逼近寄存器(SAR) ADC被視為是對(duì)主要由能源客戶提出的提供保護(hù)繼電器應(yīng)用的需求的響應(yīng)。在輸配電網(wǎng)絡(luò)中,保護(hù)繼電器監(jiān)測(cè)電網(wǎng),以盡快對(duì)任何故障情況(過(guò)壓或過(guò)流)作出反應(yīng),避免造成嚴(yán)重?fù)p壞。

圖1. 電源監(jiān)控應(yīng)用中的典型信號(hào)鏈。為簡(jiǎn)潔起見(jiàn),僅顯示一個(gè)相位。

抗混疊濾波器

輸入保護(hù)

圖2. AD7606輸入箝位保護(hù)特性。

在生產(chǎn)中執(zhí)行增益校準(zhǔn),也就是說(shuō),生產(chǎn)的每個(gè)系統(tǒng)均需通過(guò)校準(zhǔn)程序測(cè)試,存儲(chǔ)校準(zhǔn)系數(shù),然后使用這些系數(shù)來(lái)消除增益誤差。這與ADC在IC層面執(zhí)行的操作相似,但是是在系統(tǒng)層面。 對(duì)每個(gè)ADC樣本使用固定的校正因子。因?yàn)橄乱还?jié)給出的分析很詳細(xì)地講解了系統(tǒng)增益誤差,所以數(shù)字主機(jī)控制器會(huì)使用消除系統(tǒng)增益誤差的因子來(lái)乘以從ADC中獲取的每個(gè)樣本。后文稱之為后端校準(zhǔn)。

PGA的增益取決于反饋電阻(RFB),它可以編程設(shè)置模擬輸入范圍和輸入阻抗(RIN),這個(gè)值是固定的,典型值為1 MΩ。這些電阻經(jīng)過(guò)調(diào)整,可以正確設(shè)置PGA增益,將±10 V或±5 V的模擬輸入信號(hào)(AIN+/-)縮放到ADC輸入范圍,即±4.4 V,如圖3所示。

圖3. AD7606內(nèi)部PGA。僅以±10 V范圍為例。

圖4. AD7606的模擬輸入(VX+和VX-)前面的串聯(lián)電阻會(huì)改變系統(tǒng)增益。

圖5. PGA輸出的幅度隨RFILTER的增大而減小。(a) 顯示PGA輸出(單位:V),(b) 顯示PGA輸出電壓(FS的百分比)。

圖6. 系統(tǒng)增益誤差(FS的%),與AD7606中的外部RFILTER電阻(1 MΩ輸入阻抗)呈函數(shù)關(guān)系。

圖7. 因?yàn)檩斎胱杩垢?5 MΩ),所以AD7606B的PGA輸出幅度受外部RFILTER的影響更小。

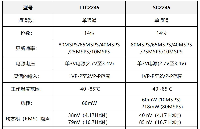

在AD7606B項(xiàng)目開(kāi)發(fā)期間,指定的三款產(chǎn)品的輸入阻抗和分辨率如表1所示。

圖8. 基于輸入阻抗(RIN)的系統(tǒng)增益誤差(FS的%)比較。

連接零電平(ZS)輸入,測(cè)量失調(diào)誤差。 消除這種失調(diào)。 連接滿量程(FS)輸入,測(cè)量增益誤差。 消除增益誤差。

但是,在這種情況下,因?yàn)榭梢酝ㄟ^(guò)公式5清楚了解該系統(tǒng)增益誤差,所以可以通過(guò)對(duì)數(shù)據(jù)實(shí)施后期處理,從控制器這一端輕松消除這種誤差,也就是說(shuō),增加一個(gè)校準(zhǔn)因子(K)來(lái)恢復(fù)公式4中引入的誤差,使得得出的系統(tǒng)增益在經(jīng)過(guò)校準(zhǔn)之后,變得與公式3中定義的理想增益類似。

圖10. 后端校準(zhǔn)誤差取決于實(shí)際RIN值。

圖11. 片內(nèi)校準(zhǔn)模塊。僅以一側(cè)通道為例。

圖12. 片內(nèi)校準(zhǔn)模塊,按照通道。

RFILTER比RIN小得多,且分立式電阻公差一般也優(yōu)于內(nèi)部1 MΩ輸入阻抗公差。 在后端校準(zhǔn)和片內(nèi)校準(zhǔn)方案中,都會(huì)用到RFILTER公差導(dǎo)致的誤差。 用戶可以通過(guò)使用公差更低的分立式電阻來(lái)最小化RFILTER公差。

圖13. RFILTER分立式電阻公差對(duì)片內(nèi)校準(zhǔn)功能精度的影響(最糟糕情況下)。

輸入阻抗產(chǎn)生的影響

假設(shè)基準(zhǔn)電壓源和基準(zhǔn)電壓源緩沖器都是理想的。沒(méi)有去除與2.5 V基準(zhǔn)電壓源或4.4 V基準(zhǔn)電壓源緩沖器輸出之間的偏差。 假設(shè)在寫入值下,該電阻是理想的,即使存在1%的公差。沒(méi)有去除與預(yù)期電阻值之間的偏差。 沒(méi)有從測(cè)量值中去除失調(diào)誤差,包括AD7606x失調(diào)誤差或前端電阻之間的不匹配。

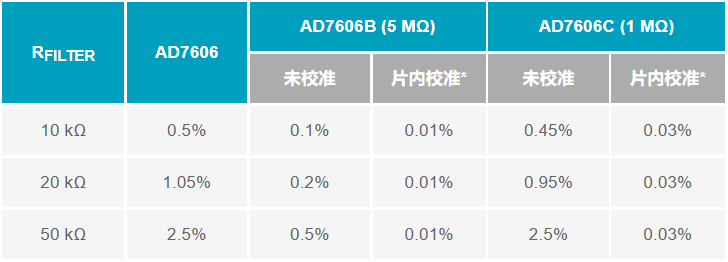

表2. 在給定RFILTER下,不同泛型(校準(zhǔn)和未校準(zhǔn)狀態(tài)下)的總誤差(%)

圖16. AD7606C-16的實(shí)際結(jié)果與理論分析結(jié)果之間的比較。

片內(nèi)校準(zhǔn)與后端校準(zhǔn)(測(cè)試結(jié)果)

如圖17a所示,UUT #1可以出色完成校準(zhǔn),可與片內(nèi)校準(zhǔn)相媲美。這意味著它的實(shí)際輸入阻抗(RIN)非常接近典型值。 UUT #2至#4顯示出一定偏差,這意味著實(shí)際輸入阻抗(RIN)稍微高于典型值。 片內(nèi)校準(zhǔn)(在所有4個(gè)圖中,以深藍(lán)色顯示)保持所有裝置和RFILTER值的總誤差均低于0.03%。

圖17. 四個(gè)AD7606C-18單元之間的片上校準(zhǔn)和后端校準(zhǔn)比較。

原文標(biāo)題:同步SAR模數(shù)轉(zhuǎn)換器的片內(nèi)校準(zhǔn)優(yōu)勢(shì)詳解

文章出處:【微信公眾號(hào):亞德諾半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

亞德諾

+關(guān)注

關(guān)注

6文章

4680瀏覽量

16235

原文標(biāo)題:同步SAR模數(shù)轉(zhuǎn)換器的片內(nèi)校準(zhǔn)優(yōu)勢(shì)詳解

文章出處:【微信號(hào):analog_devices,微信公眾號(hào):analog_devices】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

EV10AS940單芯片通道模數(shù)轉(zhuǎn)換器(ADC)

LTC2245和國(guó)產(chǎn)模數(shù)轉(zhuǎn)換器SC2245特征以及應(yīng)用優(yōu)勢(shì)分享

請(qǐng)問(wèn)模數(shù)轉(zhuǎn)換器ADS8344的多通道采樣是同步的嗎?

國(guó)產(chǎn)16位SAR模數(shù)轉(zhuǎn)換器SC1461替換AD7793用于智能發(fā)射機(jī)

ADS9110逐次逼近寄存器(SAR)模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS9120逐次逼近寄存器(SAR)模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS8372 SAR型模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS8867逐次逼近寄存器(SAR)模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS8885逐次逼近寄存器(SAR)模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS8863逐次逼近寄存器(SAR)模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS8862微功耗、微型、單端輸入、SAR模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS1110精密、連續(xù)自校準(zhǔn)模數(shù)轉(zhuǎn)換器(ADC)英文手冊(cè)

ADS1112精密、連續(xù)自校準(zhǔn)模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

逼近型模數(shù)轉(zhuǎn)換器特點(diǎn)和應(yīng)用

ADS1110精密、連續(xù)自校準(zhǔn)模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

同步SAR模數(shù)轉(zhuǎn)換器的片內(nèi)校準(zhǔn)優(yōu)勢(shì)詳解

同步SAR模數(shù)轉(zhuǎn)換器的片內(nèi)校準(zhǔn)優(yōu)勢(shì)詳解

評(píng)論