高級測試設計 (DFT) 技術通過提高順序翻牌的可控性和可觀察性,提供高效的測試解決方案,以應對更高測試成本、更高功耗、測試面積和較低幾何尺寸下的引腳數。這反過來又提高了SoC的良率,可靠性和可測試性是當今ASIC世界的重要因素。

SoC 只不過是在單個硅襯底上集成多個處理器內核、微控制器、接口、DSP(數字信號處理器)和存儲器的集成電路。在這個時代,它是任何數字系統中最重要的部分之一,因為它有助于節省電力、成本和空間。

核心只不過是 SoC 設計公司的知識產權或 IP 核。SoC 設計公司提供內核測試,SoC 設計人員提供對芯片上嵌入的內核的測試訪問。它是通過插入帶有測試邏輯的包裝器結構來插入包裝鏈的層次結構級別。我們可以最大限度地減少核心測試問題,并減少SoC的頂級引腳數。

本文簡要介紹了分層DFT技術的重要性,該技術利用包裝鏈來克服測試大型SoC設計的問題。它 顯著 減少 了 ATPG 測試 時間、 內存 占用 量 和 引腳 數。最終,它縮短了上市時間。

測試核心包裝器

對于DFT,可以在SoC級集成之前單獨測試每個內核。在執行集成時,當它們配置為內部測試模式時,內核的內部邏輯可以單獨測試,也可以成組測試。但是,當配置為外部測試模式時,可以測試內核的周圍邏輯。通過這樣做,我們主要關注的是將SoC測試劃分為不同的配置,以大大減少模式生成工作量,從而減少測試時間。

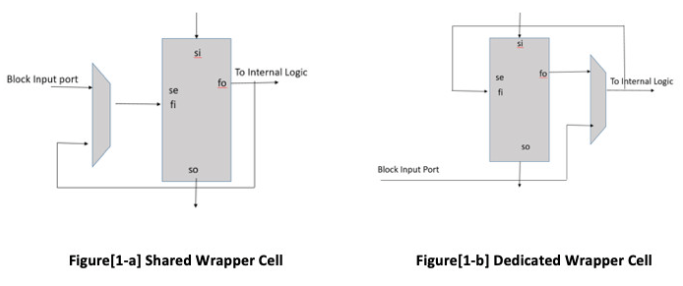

包裝單元結構

測試包裝器模式

向內或向內測試模式

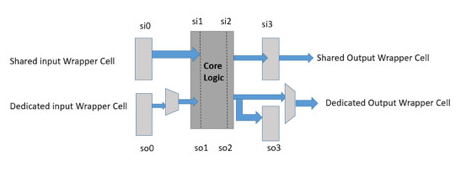

在 INTEST 模式下,通過驅動來自輸入包裝單元的輸入,我們測試分區并通過輸出包裝單元捕獲輸出。這是通過禁用核心外部的掃描鏈來完成的。它有助于使用 ATPG 對分區核心進行隔離測試。在捕獲期間,輸入包裝器單元使用單獨的輸入包裝器掃描啟用信號移動,從而避免從分區外部捕獲 x。而輸出包裝單元捕獲分區的內部狀態。

(圖 [2]:向內(測試)模式)

向外或EXTEST模式

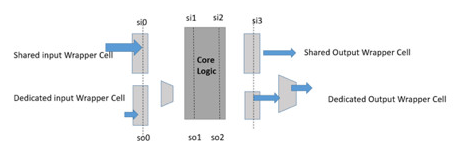

在 EXTEST 模式下,封裝器被啟用并配置為驅動和捕獲設計之外的數據。它基本上通過在此模式下繞過內部鏈來禁用內部鏈。因此,它也減少了ATPG測試時間。要測試分區和解包邏輯之間的頂級邏輯,我們可以使用此模式。在捕獲階段,值由分區外部的輸入包裝單元捕獲,輸出包裝單元在捕獲期間移動,以避免從分區的非驅動內部掃描鏈內部捕獲 x。

(圖 [3]:向外(測試)模式)

分層DFT方法

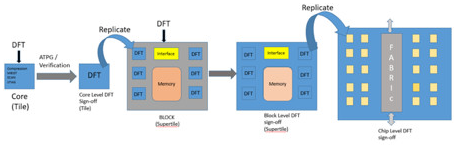

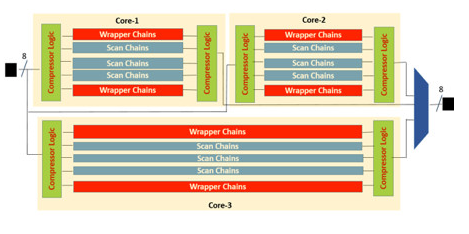

(圖 [4]:分層 DFT 實現(從內核到芯片級別))

大型設計問題,如工具內存、大型 ATPG 運行時間和引腳限制,可以通過分層 DFT 技術解決。在這種方法中,芯片可以分成多個較小的部分或內核,可以有效地訪問和處理。由于在內核級別生成模式,它導致引腳數量、內存和測試運行時間的減少。也可以并行運行內核。

每當內核配置為內部模式時,輸入包裝器都會啟動到內核中,輸出包裝器會觀察內核輸出。在這種情況下,將測試包裝器邊界內的核心邏輯。所有鏈都連接到壓縮器,它生成核心級別模式,可以重新定位到頂層。它還有助于合并多個內核的模式。對于外部模式,所有包裝鏈都連接到核心邊界,并為頂層生成模式。當涉及到全芯片級時,所有包裝鏈和頂級鏈都連接到頂級壓縮器。

分層 DFT 流

(圖 [5]:測試訪問機制)

圖 5 顯示,頂級引腳在各個內核級壓縮機邏輯和頂級壓縮機邏輯之間共享。它導致執行分層DFT的頂級芯片引腳減少。 單個內核可以單獨測試,也可以并行測試以減少測試時間。掃描在塊級別插入。當模塊在頂層組裝時,鏈可以通過以下兩種方式之一連接:串聯或直接連接到I / O。在級聯掃描鏈方法中,來自一個塊的掃描鏈與來自另一個塊的鏈連接。

分層DFT的優點/缺點:

使用分層 DFT 的一些優點是:

通過使用自動化工具,我們可以在SoC級別組裝核心級鏈。

如果核心級鏈是平衡的,那么工具將很容易平衡SOC級鏈。

通過維護有限數量的針腳,掃描鏈是可以管理的。

它提供了更多核心級通道。

ATPG 運行時間更短,需要的內存更少,從而顯著縮短了測試時間。

一些缺點是:

當設計包含多個時鐘邊沿并在上升沿和下降沿之間來回移動時引起移位問題時,當掃描鏈穿過內核時觸發翻牌。

為了避免時序問題,我們必須通過使用鎖定鎖存器來處理內核級和SoC級的不同時鐘域。

如果出現這種情況,在單核級別引發的時序問題可能會損壞所有其他內核,因為鏈在多個內核中使用。

在本文中,我們探討了包裝體的重要性和包裝細胞的類型。如前所述,包裝器的特征和功能訪問以及包裝器對不同塊的訪問。我們已經看到了使用包裝器的分層DFT方法以及圍繞核心邏輯的包裝單元的互連。最后,我們提到了包裝器生成以及如何使用包裝器內核最小化面積和性能影響。分層核心包裝器具有廣泛的工業用途,我們已經介紹了使用包裝單元的結果。eInfochips成功地為大型SoC提供了DFT解決方案,為大多數客戶使用分層DFT實現。

審核編輯:郭婷

-

微控制器

+關注

關注

48文章

7896瀏覽量

153600 -

處理器

+關注

關注

68文章

19785瀏覽量

233291 -

存儲器

+關注

關注

38文章

7625瀏覽量

166252

發布評論請先 登錄

打開我的電腦網頁不是最大化新窗口

[轉]LabVIEW實現窗口最大化和最小化

labview能否實現生成EXE文件后界面最大化?

labview 編寫的應用程序,怎么設置最大化后居中顯示

最大化電池操作時間

如何實現產品專利權最大化資料下載

分層DFT技術如何實現在最大化SoC

分層DFT技術如何實現在最大化SoC

評論