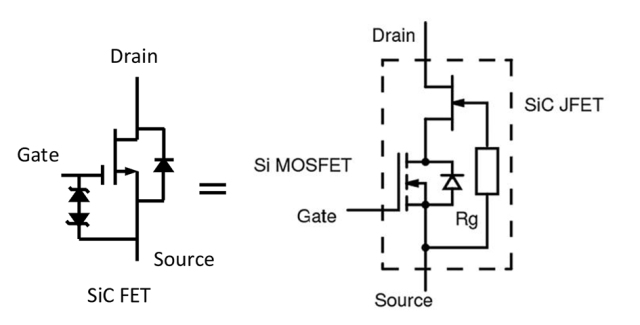

碳化硅 (SiC) MOSFET 的快速開關(guān)速度、高額定電壓和低導(dǎo)通 RDS(on) 使其對(duì)電源設(shè)計(jì)人員極具吸引力,這些設(shè)計(jì)人員不斷尋找提高效率和功率密度的方法,同時(shí)保持系統(tǒng)簡(jiǎn)單性。

然而,由于其快速開關(guān)速度會(huì)產(chǎn)生高漏源電壓(VDS)尖峰和較長(zhǎng)的振鈴持續(xù)時(shí)間,因此它們會(huì)引入EMI,尤其是在高電流水平下。

了解 VDS尖峰和振鈴

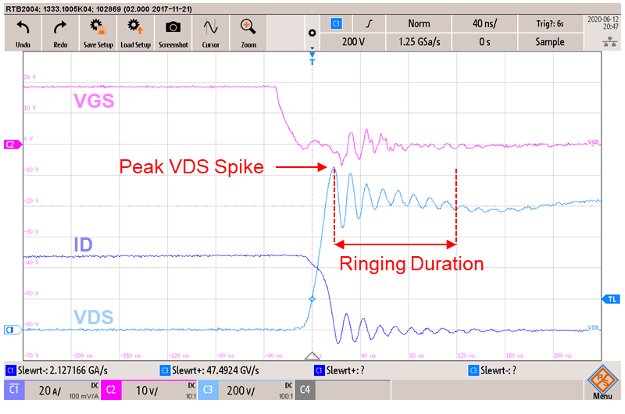

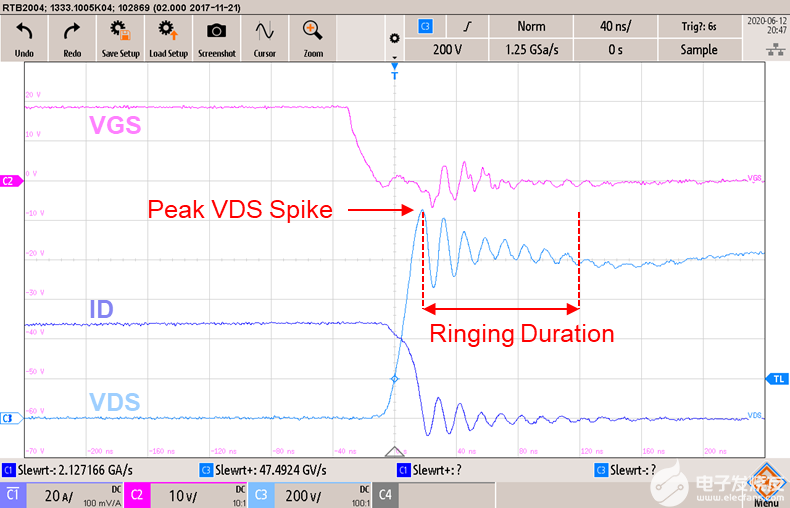

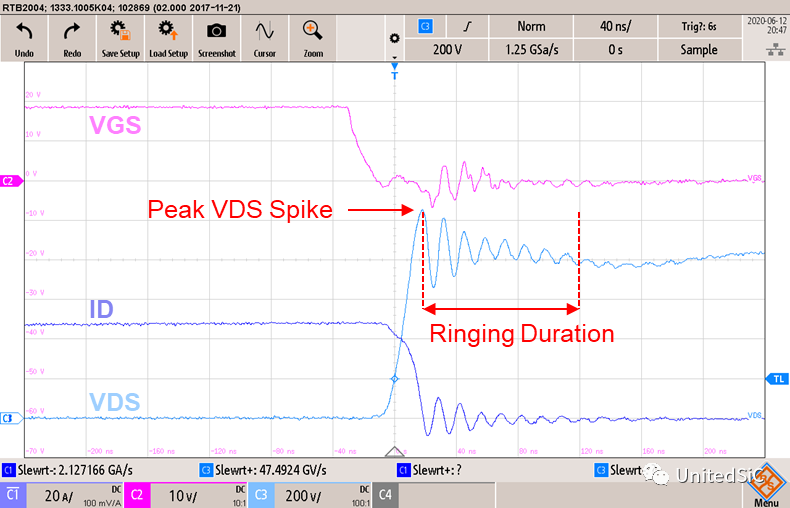

寄生電感是V的主要原因DS碳化硅 MOSFET 的尖峰和振鈴。從關(guān)斷波形(圖1)來看,柵源電壓(VGS)為18V至0V。關(guān)斷的漏極電流(ID)為50A,VDS為800V。SiC MOSFET 的快速開關(guān)速度可產(chǎn)生高V DS尖峰和較長(zhǎng)的振鈴持續(xù)時(shí)間。該尖峰降低了器件處理雷電條件或負(fù)載突然變化的設(shè)計(jì)裕量,并且長(zhǎng)振鈴持續(xù)時(shí)間會(huì)引入EMI。在高電流水平下,這一事件更加明顯。

圖1.VDS尖峰和關(guān)斷時(shí)振鈴,采用 SiC MOSFET (1200V 40mOhm)

常見的EMI抑制技術(shù)

抑制EMI的傳統(tǒng)方法是降低通過器件的電流流速(dI/dt),這是通過使用高柵極電阻(RG)來實(shí)現(xiàn)的。但高RG會(huì)顯著增加開關(guān)損耗,并且在效率和EMI之間存在折衷。

抑制EMI的另一種方法是降低電源環(huán)路雜散電感。然而, 為了實(shí)現(xiàn)這一目標(biāo), PCB的布局需要更小, 電感更少封裝。然而,最小化電源環(huán)路是有限的,并且需要遵守最小間距和間隙安全規(guī)定。使用較小的封裝也會(huì)影響熱性能。

濾波器設(shè)計(jì)可用于幫助滿足EMI要求并簡(jiǎn)化系統(tǒng)權(quán)衡。頻率抖動(dòng)等控制技術(shù)也可以降低電源的EMI噪聲。

使用 RC 緩沖器

采用簡(jiǎn)單的RC緩沖器是一種更有效和高效的方法。它控制 VDS 尖峰并縮短振鈴持續(xù)時(shí)間,效率更高,關(guān)斷延遲可忽略不計(jì)。對(duì)于更快的dv/dt和額外的電容,緩沖電路具有更高的位移電流,從而降低了關(guān)斷轉(zhuǎn)換處的ID和VDS重疊。

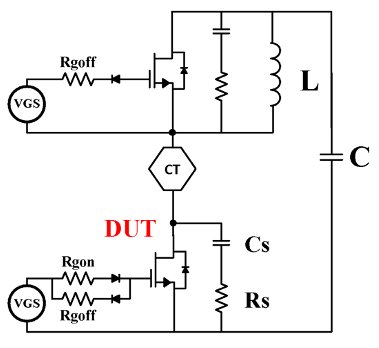

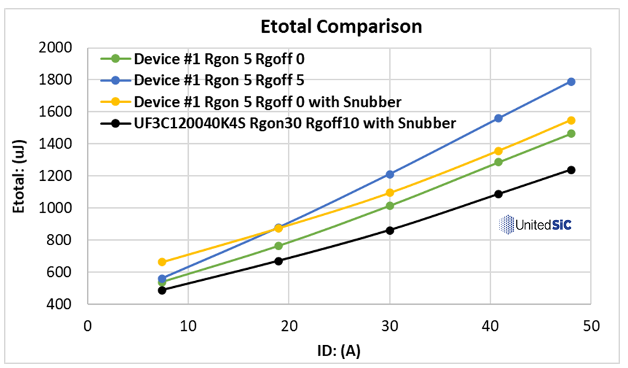

雙脈沖測(cè)試(DPT)證明了RC緩沖器的有效性。它是帶有感性負(fù)載的半橋配置。電橋的高側(cè)和低側(cè)使用相同的器件,在低側(cè)測(cè)量VGS、VDS和ID(圖2)。電流互感器(CT)測(cè)量器件和緩沖電流。因此,測(cè)得的總開關(guān)損耗包括器件和緩沖器損耗。

圖2.半橋配置(頂部和底部設(shè)備相同)

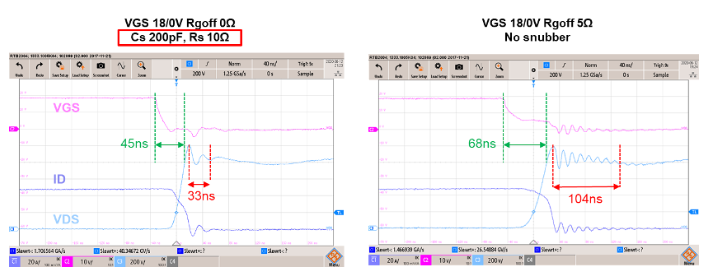

RC 緩沖器只是一個(gè) 200pF 電容器和 10Ω 電阻,串聯(lián)在 SiC MOSFET 的漏極和源極上。

圖 3:RC 緩沖器(左)比高 RG(右)更有效地控制關(guān)斷 EMI

在圖3中,比較了圖1中同一器件的關(guān)斷。左側(cè)波形使用R G(off)低的RC緩沖器,而右側(cè)波形具有高RG(off)且沒有緩沖器。兩種方法都限制了關(guān)斷峰值尖峰漏源電壓VDS。然而,緩沖電路通過將振鈴持續(xù)時(shí)間減少到僅33ns而更有效,并且延遲時(shí)間也更短。

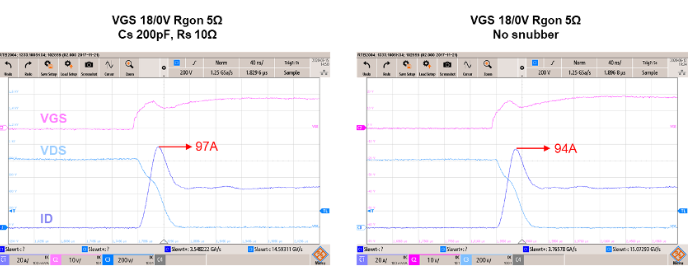

圖4.比較表明,使用 RC 緩沖器在開啟時(shí)的影響非常小

圖4比較了R G(on)為5Ω時(shí)有RC緩沖器(左)和不帶RC緩沖器的波形。RC緩沖器的導(dǎo)通波形具有略高的峰值反向恢復(fù)電流(IRR),但沒有其他明顯的差異。

RC 緩沖器比高 RG(off) 更有效地控制 VDS尖峰和振鈴持續(xù)時(shí)間,但它會(huì)影響效率嗎?

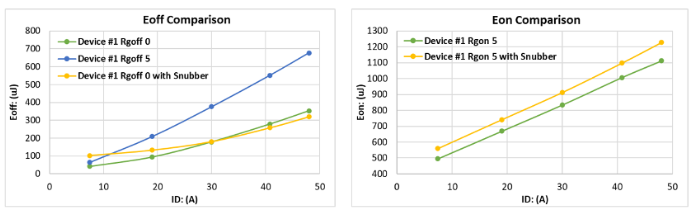

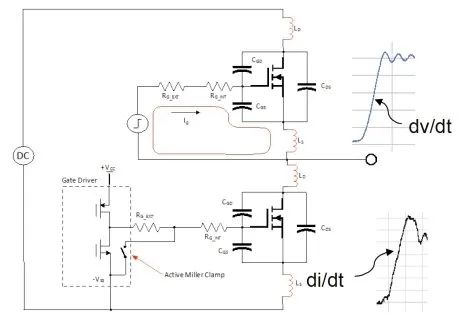

圖5.緩沖器與高RG(關(guān)閉)之間的開關(guān)損耗(E 關(guān)閉、E 開啟)比較

在48A時(shí),高R G(關(guān)斷)開關(guān)損耗是低RG(關(guān)斷)緩沖器的兩倍以上,幾乎與不使用緩沖器的緩沖器相當(dāng)。因此,可以得出結(jié)論,緩沖器效率更高,可以更快地切換和控制VDS尖峰和振鈴。從導(dǎo)通開關(guān)損耗來看,緩沖器僅略微增加E。

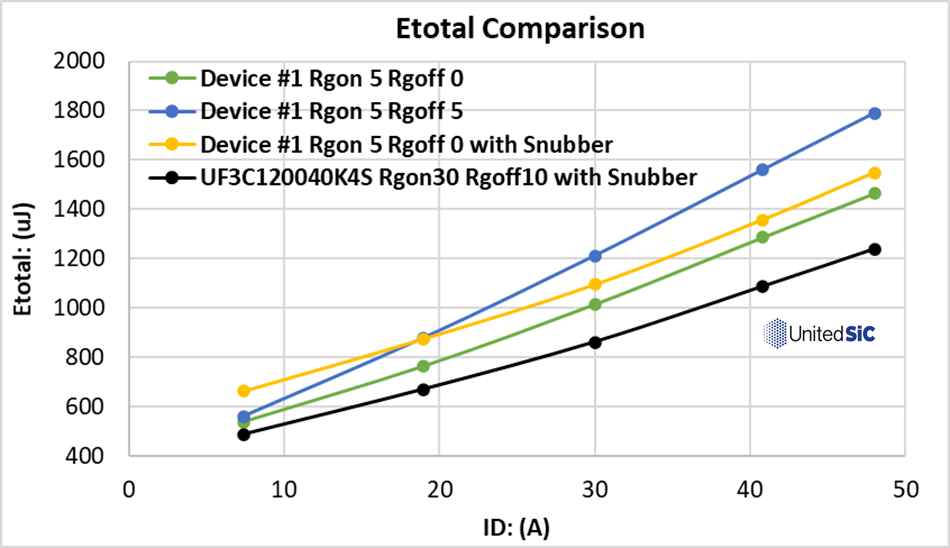

圖6.緩沖器的總開關(guān)損耗(E總損耗)與高RG(off)的比較

為了更好地理解整體效率,Eoff和Eon相加 - E總計(jì)(圖6)。全速開關(guān)時(shí),緩沖器在18A以上效率更高。對(duì)于開關(guān)頻率為40A/40kHz的40mΩ器件,采用RC緩沖器時(shí),高RG(關(guān)斷)之間的損耗差為11W。總而言之,緩沖器是一種更簡(jiǎn)單、更有效、更高效的方法,可以最大限度地減少EMI和開關(guān)損耗,而不是使用高RG(off)。

審核編輯:郭婷

-

MOSFET

+關(guān)注

關(guān)注

149文章

8222瀏覽量

218258 -

emi

+關(guān)注

關(guān)注

53文章

3683瀏覽量

130201 -

SiC

+關(guān)注

關(guān)注

31文章

3146瀏覽量

64396

發(fā)布評(píng)論請(qǐng)先 登錄

如何最大限度地提高SiC MOSFET性能呢?

功率MOSFET的開關(guān)損耗:關(guān)斷損耗

為何使用 SiC MOSFET

全SiC功率模塊的開關(guān)損耗

開關(guān)損耗更低,頻率更高,應(yīng)用設(shè)備體積更小的全SiC功率模塊

SiC-SBD大幅降低開關(guān)損耗

SiC MOSFET SCT3030KL解決方案

MOSFET開關(guān)損耗分析

最大限度地減少SiC FET中的EMI和開關(guān)損耗

全SiC功率模塊的開關(guān)損耗

最大限度降低SiC FET的EMI的開關(guān)損耗

全SiC功率模塊的開關(guān)損耗

如何在使用SiC MOSFET時(shí)最大限度地降低EMI和開關(guān)損耗

如何在使用SiC MOSFET時(shí)最大限度地降低EMI和開關(guān)損耗

評(píng)論