芯片設計工程師根據(jù)功能,完成RTL設計,添加各種約束,完成綜合、Place & Route等一系列工作之后,還需要一些配置數(shù)據(jù),完成寄存器初始化等內(nèi)容,才能開始工作。

今天我們一起來聊一聊FPGA的配置數(shù)據(jù)模式。

FPGA配置方式

根據(jù)FPGA配置過程控制者的不同,我們將配置方式主要分為三類:

FPGA控制配置過程第一種最常見的模式是,從片外FLASH中加載配置所需的比特流,F(xiàn)PGA內(nèi)部產(chǎn)生時鐘,整個過程有FPGA自主控制。FPGA 上電以后,將配置數(shù)據(jù)從FLASH中,讀入到SRAM中,實現(xiàn)內(nèi)部結(jié)構(gòu)映射。

優(yōu)點:不需要借助其他模塊或者終端,自己控制整個過程。

缺點:一般只能從FLASH(掉電不會丟失數(shù)據(jù))或者其他片外非易失性存儲器中,加載配置,配置方式有限。

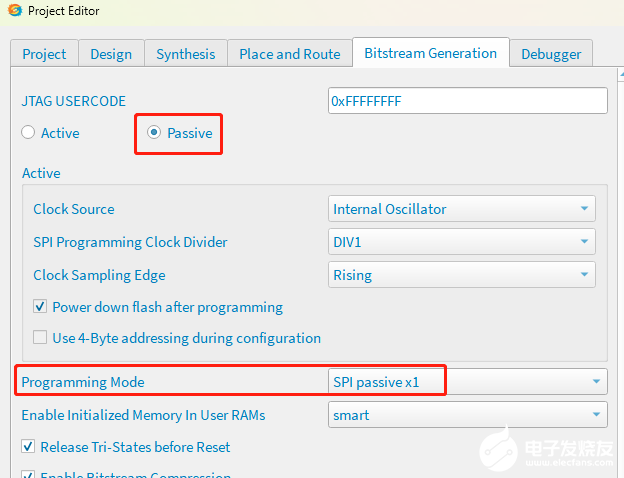

處理器控制器控制配置過程第二種模式是,通過借助處理器、控制器或者其他終端,完成配置過程。FPGA 作為從設備,微處理器或者控制電路提供配置所需的時序,實現(xiàn)配置數(shù)據(jù)的下載。

優(yōu)點:配置方式靈活。可以將配置數(shù)據(jù)放置在FLASH、硬盤燈存儲介質(zhì)中,通過其他終端完成整個配置過程。

缺點:需要借助其他終端設備。

通過JTAG配置第三種模式,通過JTAG完成配置。一般情況下,是通過JTAG進行調(diào)試,將比特流文件下載到FGPA中。需要注意的是,這種模式下,如果出現(xiàn)斷電,則配置失效。

此外有的FPGA還可以通過網(wǎng)絡進行配置,在實際工作中,接觸較少,所以不再贅述。

單片F(xiàn)PGA多片F(xiàn)PGA配置

單片F(xiàn)PGA和多片F(xiàn)PGA的配置過程類似,但還是有些不同,下面我們分開來描述一下,在FPGA控制配置過程這種模式下面,兩者的異同。

單片F(xiàn)PGA配置FPGA 的CCLK 管腳,提供工作時鐘給PROM ,PROM 在CCLK 的上升沿,將數(shù)據(jù)從D0 管腳送到FPGA 的DIN 管腳,這種方式是最簡單也是最常用的一種配置方式。在這種方式下,有兩點非常重要:

電源適配性。從上面描述可以看出,整個過程需要FPGA和PROM之間進行通信,所以兩者的接口電平必須一致,即FPGA管腳電壓和PROM的輸入電壓相等。JTAG鏈的完整性。保證JTAG 連接器、FPGA、PROM 的TMS、TCK 連在一起,保證從JTAG 連接器TDI 到其TDO 之間閉合回路。多片F(xiàn)PGA配置配置過程單片和多片過程相似,但是多片F(xiàn)PGA 配置時,需要區(qū)分主設備從設備,且需要選擇不同的配置模式。

小結(jié)

在實際工作中,工程師根據(jù)具體的工作需要,選擇相應的配置方式。

歡迎加入至芯科技FPGA微信學習交流群,這里有一群優(yōu)秀的FPGA工程師、學生、老師、這里FPGA技術(shù)交流學習氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

原文標題:FPGA數(shù)據(jù)配置模式解析

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613879

原文標題:FPGA數(shù)據(jù)配置模式解析

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

CY7C68013A客戶配置成slavefifo模式,FPGA發(fā)送數(shù)據(jù)到PC則會丟包或者收到的數(shù)據(jù)對不上,什么原因?

ADS4125配置成CMOS模式輸出數(shù)據(jù),始終沒有數(shù)據(jù)輸出是怎么回事?

ADS8528如何與FPGA鏈接通訊,采集數(shù)據(jù)?

AFE5805的配置應該注意些什么問題呢?

易靈思FPGA PS配置模式--v7

自動化創(chuàng)建UI并解析數(shù)據(jù)

ADS7952當配置為手動模式時,SPI通信時最后兩幀的數(shù)據(jù)怎么配置?

CDCI6214采用FPGA配置后,沒有時鐘輸出怎么解決?

PCM5142如何在FPGA中通過SPI配置寄存器?

固化FPGA配置芯片的方式

易靈思Trion FPGA PS配置模式--update(6)

FPGA數(shù)據(jù)配置模式解析

FPGA數(shù)據(jù)配置模式解析

評論