1引言

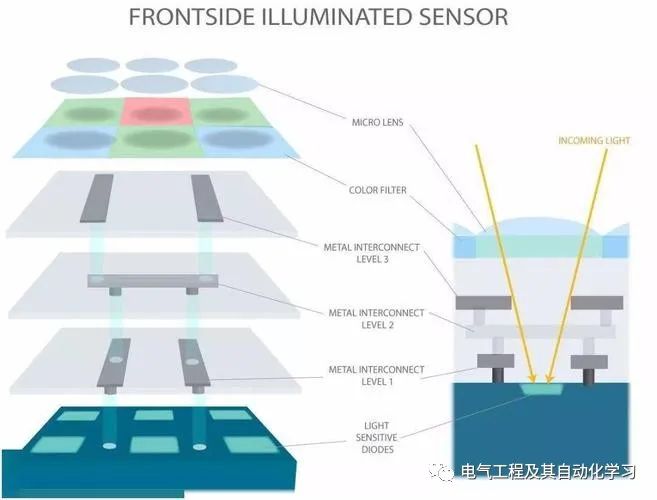

數(shù)碼相機(jī)等圖像消費(fèi)類電子產(chǎn)品產(chǎn)業(yè)正在飛速發(fā)展,這使得圖像傳感器和數(shù)碼相機(jī)專用集成芯片的研制獲得巨大的市場支持。目前廣泛使用的數(shù)碼相機(jī)圖像傳感器主要是以下兩種:CCD和CMOS。CCD圖像傳感器具有技術(shù)成熟、圖像噪聲小等優(yōu)點(diǎn),但由于制作工藝復(fù)雜,與標(biāo)準(zhǔn)工藝不兼容,且需要高電壓供電,芯片功耗大,目前僅在型數(shù)碼相機(jī)市場上占有一席之地。而CMOS圖像傳感器采用了CMOS工藝,可以將圖像采集單元和信號處理單元集成到同一塊芯片上,因而具有集成度高、功耗低、價格便宜的優(yōu)點(diǎn),具有很好的發(fā)展前景。隨著噪聲消除技術(shù)的改進(jìn),目前CMOS圖像傳感器正由中、低檔數(shù)碼相機(jī)向型數(shù)碼相機(jī)發(fā)展。

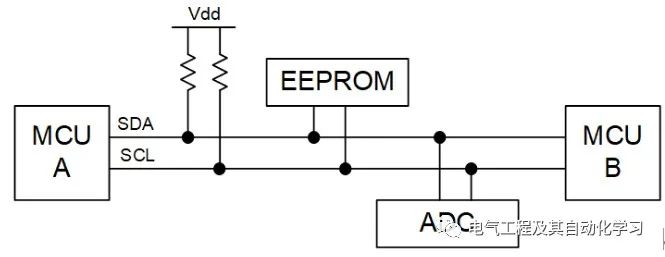

現(xiàn)在的CMOS圖像傳感器芯片大都把I2C總線的一個子集作為控制接口(如Motorola公司的MCM20027,Omnivision公司的OV9620等),因而用戶可以很方便地對芯片進(jìn)行編程操作。與其他串行總線相比,I2C總線以兩根連線實(shí)現(xiàn)了全雙工同步數(shù)據(jù)傳送,可以極方便地構(gòu)成多機(jī)系統(tǒng),并進(jìn)行擴(kuò)展,適用于消費(fèi)電子、通信電子、工業(yè)電子等領(lǐng)域的低速器件。I2C總線由雙向數(shù)據(jù)線SDA和時鐘線SCL組成川,用戶使用集電極開路門以“線與”方式進(jìn)行總線連接。圖1為I2C總線的通信協(xié)議示意圖,包括開始信號、結(jié)束信號、應(yīng)答信號和數(shù)據(jù)有效等狀態(tài)。當(dāng)SCL持續(xù)為高電平時,SDA由‘1'跳變到‘0',表示開始信號;當(dāng)SCL持續(xù)為高電平時,SDA由‘0'跳變到‘l',表示結(jié)束信號:在數(shù)據(jù)傳輸過程中,SDA在時鐘高電平時有效,低電平時更換數(shù)據(jù)。開始和結(jié)束信號均由主I2C產(chǎn)生,通過SDA傳輸?shù)臄?shù)據(jù)以字節(jié)(8—bit為單位,高位在前,低位在后,在每個字節(jié)后面由接收端發(fā)送一個低電平的應(yīng)答信號。

本文設(shè)計了一種基于I2C控制總線的CMOS圖像傳感器接口電路,能夠有效控制CMOS圖像傳感器的指令,產(chǎn)生數(shù)碼相機(jī)專用集成電路其他模塊的同步時序,在MCU的控制下完成取景和拍照操作,并支持多種規(guī)格的CMOS圖像傳感器和液晶顯示器。

2頂層設(shè)計

根據(jù)所設(shè)計的數(shù)碼相機(jī)專用集成電路芯片的系統(tǒng)要求[2],CMOS圖像傳感器接口用來控制達(dá)400萬像素多種規(guī)格的CMOS圖像傳感器,并且在MCU的控制下,能控制傳感器芯片的自動/手動曝光和自動/手動白平衡及其他芯片支持的功能。該接口電路能夠在取景和拍照兩種模式下工作,在取景模式下,實(shí)現(xiàn)可編程的降采樣處理,能夠輸出以4的倍數(shù)為基準(zhǔn)的任意分辨率的圖像,并接受多種規(guī)格的液晶顯示器,取景速度達(dá)到30幀/s。

根據(jù)上述功能要求將CMOS圖像傳感器接口劃分為三個模塊:主I2C總線接口模塊、寄存器文件接口和可編程降采樣模塊,其總體框圖和輸入輸出端口線如圖2所示。端口線主要有:①和MCU接口的連接,包括MCU_AB(地址總線),MCU_DB(數(shù)據(jù)總線),MCU_nWR(寫使能),MCU_nRD(讀位能),MCU—nCS(MCU操作選中信號)和MCU nINT(中斷信號)②和CMOS圖像傳感器的連接,包括來自CMOS圖像傳感器的幀同步(VC L K)、行同步(H C L K)、像素同步(PCLK)、數(shù)據(jù)ADC(10位CMOS輸出的數(shù)值),以及I2C總線的SDA,SCL,SCCB_E等:③和數(shù)碼相機(jī)專用集成電路芯片的其他子模塊相連,如VSYNC(幀同步)、HSYNC(行同步)、PSYNC(像素同步)、ADCOUT(輸出圖像數(shù)據(jù))。

3模塊設(shè)計

3.1寄存器文件模塊

寄存器文件模塊包括一個中斷狀態(tài)機(jī)和MCU接口。中斷狀態(tài)機(jī)用以控制主I2C總線模塊,降采樣處理模塊和MCU接口的協(xié)調(diào)工作,它主要包括5個狀態(tài):INT_DECIDE,INT_I2C_READ,INT_MCU_READ,INT_I2C_WRITE和INT_CLEAR。狀態(tài)機(jī)缺省狀態(tài)為INT_DECIDE判決狀態(tài),表示狀態(tài)機(jī)處于等待狀態(tài):INT_I2C_READ表示I2C,總線正在從CMOS傳感器讀數(shù)據(jù):INT_12C_WRITE表示I2C總線正在從CMOS傳感器寫數(shù)據(jù):INT_MCU_READ表示MCU正從I2C上讀數(shù)據(jù):INT_CLEAR表示清中斷。

MCU接口通過給內(nèi)部寄存器讀寫參數(shù),使CMOS圖像傳感器接口電路能夠?qū)崿F(xiàn)取景、拍照和軟復(fù)位的功能:并通過I2C總線給CMOS傳感器的內(nèi)部參數(shù)寄存器讀寫參數(shù),實(shí)現(xiàn)對CMOS傳感器進(jìn)行各種參數(shù)設(shè)置,以充分發(fā)揮CMOS傳感器的性能。其中內(nèi)部寄存器包括控制寄存器和降采樣寄存器,降采樣寄存器主要給降采樣處理模塊提供可編程所需要的參數(shù)。控制寄存器為低4位有效,第0位為軟復(fù)位位,當(dāng)系統(tǒng)復(fù)位或系統(tǒng)設(shè)置該位為l時,整個接口置于復(fù)位狀態(tài);當(dāng)系統(tǒng)設(shè)置該位為0時,則取消復(fù)位狀態(tài)變?yōu)楣ぷ鳡顟B(tài)。第1和第2位一起用來控制拍照和取景操作,當(dāng)兩位均為1時表示拍照狀態(tài):當(dāng)?shù)?位為1,第2位為0時表示取景狀態(tài);第3位用來表示中斷位。

3.2主I2C總線接口

由于CMOS圖像傳感器目前普遍采用的是I2C總線功能集中的一個子集,因此該接口比一個完整的主I2C總線要更簡單。它的讀寫周期如下:當(dāng)要進(jìn)行I2C總線寫操作時,先發(fā)送所使用的CMOS傳感器特定ID寫地址,緊接著發(fā)送需要寫的寄存器的地址(sub_address),再發(fā)送數(shù)據(jù)(data);當(dāng)進(jìn)行I2C總線讀操作時,先發(fā)送所使用的CMOS傳感器特定ID寫地址,緊接著發(fā)送需要寫的寄存器的地址(sub_address),再發(fā)送CMOS傳感器特定ID讀地址,接收數(shù)據(jù)(data)。對于不同的CMOS傳感器產(chǎn)品,它們的ID地址是不同的,例如Omnivision公司為60h(寫)[3]、61h(讀)Motorola公司為66h(寫)[4]、67h(讀)。

考慮該主I2C總線的讀寫周期的特殊性,將該I2C總線設(shè)計成如圖3所示的總體結(jié)構(gòu)。主要包括控制狀態(tài)機(jī)、數(shù)據(jù)緩存器、SDA產(chǎn)生接收器、SCL產(chǎn)生器以及并-串轉(zhuǎn)換和串-并轉(zhuǎn)換。數(shù)據(jù)緩存器用來將要通過I2C總線傳輸?shù)臄?shù)據(jù)組合成所需要的格式,由于CMOS圖像傳感器的I2C總線特殊的讀寫操作格式,因此可以將需要傳輸?shù)腎D地址、sub address和data組合在一個30位的緩存器中,它的低六位用來表示高24位的3個字節(jié)的屬性,以便正確的傳輸,通過這種數(shù)據(jù)組合,便于I2C總線傳輸和識別。串-并轉(zhuǎn)換和并-串轉(zhuǎn)換本質(zhì)上是兩個移位寄存器,用來將接收到的串行數(shù)據(jù)轉(zhuǎn)變成并行數(shù)據(jù)或并行數(shù)據(jù)轉(zhuǎn)變成要發(fā)送的串行數(shù)據(jù)。SDA產(chǎn)生接收器用宋生成主總線的控制命令如開始、結(jié)束和應(yīng)答位等(和SCL配合工作),隨后接收和讀取數(shù)據(jù)。SCL產(chǎn)生器用來產(chǎn)生I2C總線的時鐘信號和控制命令信號(和SDA配合工作)。控制狀態(tài)機(jī)主要負(fù)責(zé)控制整個I2C總線的流程,其狀態(tài)圖如圖4所示。主要包括以下八個狀態(tài):IDLE(等待讀取或?qū)懭霐?shù)據(jù))、LOAD(加載需要傳輸?shù)臄?shù)據(jù))、START(發(fā)送開始信號)、WRRD(I2C總線處于讀取或?qū)懭霐?shù)據(jù)狀態(tài))、DECIDE(判決當(dāng)前狀態(tài)是讀取數(shù)據(jù)還是寫入數(shù)據(jù))、WR_ACK(寫應(yīng)答)、RD_ACK(讀應(yīng)答)、STOP(發(fā)送結(jié)束信號)。例如給CMOS圖像傳感器的一個寄存器寫一個字節(jié)的數(shù)據(jù),需要經(jīng)歷以下狀態(tài):IDLE→LOAD→START→WRRD→WR_ACK→WRRD→WR_ACK→WRRD→WR_ACK→STOP→IDLE;一個字節(jié)的寫操作的ActiveHDL的仿真時序如圖5所示。

3.3可編程降采樣模塊

可編程降采樣模塊是通過MCU給內(nèi)部的降采樣寄存器寫入需要的降采樣參數(shù)來實(shí)現(xiàn)可編程的,接口內(nèi)一共有6個降采樣參數(shù)寄存器:總行數(shù)寄存器(hrefprecnt)、總列數(shù)寄存器(pixprecnt)、行丟寄存器(hrefdropcnt)、列丟寄存器(pixdropcnt)、行降采樣寄存器(vdscnt)、列降采樣寄存器(hdscnt),各個寄存器參數(shù)所表示的意義如圖6所示。操作過程如下:先跳過列丟寄存器值和行丟寄存器值數(shù)目的列和行,接下來保留總列數(shù)寄存器值和總行數(shù)寄存器值數(shù)目的列和行,在這些保留的行和列當(dāng)中用列降采樣寄存器和行降采樣寄存器的值進(jìn)行降采樣:行降采樣寄存器和列降采樣寄存器分為兩部分:保留和丟棄,保留和丟棄的像素和行的數(shù)目均為偶數(shù)且為連續(xù)的像素,從而保證降采樣后輸出的像素滿足RGRG…RG或GBGB…GB的Bayer格式。通過這樣幾個降采樣寄存器可以很方便實(shí)現(xiàn)的各種分辨率的降采樣,能夠輸出任意4的倍數(shù)的分辨率的圖像,因而可以很方便的支持多種規(guī)格的LCD顯示器。

4電路的FPGA驗證

在經(jīng)過上述頂層設(shè)計和各個子模塊的設(shè)計后,用Verilog語言[5]來實(shí)現(xiàn),并用ActiveHDL來進(jìn)行RTL級仿真,并對電路進(jìn)行了FPGA驗證,使用的芯片是Xilinx公司的SPARTANIIXC2S200PQ208,系統(tǒng)時鐘為54MHz,F(xiàn)PGA綜合的結(jié)果顯示需要FPGA芯片的11%的SLICEs,22%的IOBs和25%的GCLKIOBs。整個測試流程由MCU控制,在拍照模式下,CMOS圖像傳感器的數(shù)據(jù)流經(jīng)CMOS接口采樣存儲在SDRAM中,再由EPP接口上傳至PC上:在取景模式下,則有LCD顯示器實(shí)時顯示。該接口電路在各種工作模式下功能驗證正確。

FPGA驗證通過后,作為數(shù)碼相機(jī)專用集成電路芯片的一部分采用上華0.6μm工藝庫進(jìn)行了ASIC的后端自動綜合,包括用Design Compiler(Synopsys公司)進(jìn)行邏輯綜合、Prime Time(Synopsys公司)做版圖前驗證、Silicon Ensemble(Cadence公司)做自動布局布線、Virtuoso(Cadence公司)做DRC和LVS,得到的版圖面積約為3.7mm×3.7mm,綜合頻率為25MHz,在5V供電下,功耗約為150mW。

5結(jié)論

CMOS圖像傳感器接口電路的設(shè)計模塊可以分為寄存器文件、主12C總線接口和可編程降采樣模塊3部分,經(jīng)過電路的頂層設(shè)計和各個子模塊的功能設(shè)計,進(jìn)行了Verilog語言代碼實(shí)現(xiàn),用ActiveHDL進(jìn)行了RTL級仿真,并進(jìn)行了FPGA驗證,功能設(shè)汁正確,并打算作為數(shù)碼相機(jī)專用集成電路芯片的一部分到工藝廠流片。

審核編輯黃昊宇

-

傳感器

+關(guān)注

關(guān)注

2562文章

52450瀏覽量

763042 -

接口

+關(guān)注

關(guān)注

33文章

8918瀏覽量

153134

發(fā)布評論請先 登錄

I2C總線通信原理 如何設(shè)計I2C總線電路

基于I2C總線的智能家居應(yīng)用

I2C總線與Arduino的接口示例

I2C總線的工作模式介紹

I2C總線數(shù)據(jù)傳輸速度要求

I2C總線應(yīng)用實(shí)例分析

I2C總線與SPI總線的比較

使用GPIO模擬I2C的電路設(shè)計

TMP100-EP帶I2C接口的數(shù)字溫度傳感器數(shù)據(jù)表

TMP275 具有 I2C 和 SMBus 接口的 ±0.5°C 溫度傳感器數(shù)據(jù)表

TMPx75具有I2C和SMBus接口的溫度傳感器數(shù)據(jù)表

基于I2C總線的CMOS圖像傳感器接口電路設(shè)計

基于I2C總線的CMOS圖像傳感器接口電路設(shè)計

評論