霜降

什么是EDA?

EDA全稱是電子設(shè)計(jì)自動化,是一種工業(yè)軟件,所有的芯片公司都在用各種各樣的EDA軟件,來輔助完成芯片的設(shè)計(jì)。

DEA軟件有很明顯的杠桿效應(yīng)。EDA本身的市場規(guī)模其實(shí)并沒有很大,只占119億美元的市場份額但卻直接撬動了4400億美元的全球半導(dǎo)體產(chǎn)業(yè),也就是如果EDA出現(xiàn)問題,那么整個(gè)芯片產(chǎn)業(yè)都會受到重大的沖擊。光刻機(jī)是整個(gè)芯片產(chǎn)業(yè)的關(guān)鍵環(huán)節(jié),但DEA軟件雖然不為人所知,但重要性卻不輸光刻機(jī)的關(guān)鍵領(lǐng)域。

芯片設(shè)計(jì)主要流程理解

芯片的設(shè)計(jì)的主要流程可以分為前端和后端,前端負(fù)責(zé)芯片的邏輯電路設(shè)計(jì),包括系統(tǒng)架構(gòu)的定義,RTL編碼,邏輯綜合,這期間會進(jìn)行多次的仿真和驗(yàn)證,最終得到門級的網(wǎng)表。后端主要負(fù)責(zé)芯片的物理設(shè)計(jì),包括布局規(guī)劃,時(shí)鐘樹綜合,布線,參數(shù)提取等等步驟,最終會得到一個(gè)芯片電路的物理版圖,然后提供給晶圓廠去制造。簡單來說,前端就是這個(gè)芯片是什么,他有哪些部分,后端是這個(gè)芯片的各個(gè)部分長什么樣子。比如蓋房子,前端是畫出這個(gè)房子的設(shè)計(jì)圖,比如有幾個(gè)房間,每個(gè)房間是餐廳還是臥室,后端設(shè)計(jì)就是按照設(shè)計(jì)圖,畫出這個(gè)房子的施工圖紙,包括建筑施工的時(shí)候需要哪些步驟,用鋼結(jié)構(gòu)還是用磚結(jié)構(gòu),怎么做防水,怎么拉網(wǎng)線走水電等。建筑隊(duì)就是晶圓代工廠,就可以拿著施工圖紙去把芯片造出來了。

EDA工具最大的好處,就是能極大的縮短芯片設(shè)計(jì)的時(shí)間,從而提升芯片設(shè)計(jì)的效率。手動畫電路圖可能又慢又容易出錯(cuò),但是用計(jì)算機(jī)幾分鐘就完成了,而且還可以去隨便的修改。時(shí)間就是金錢,越早讓芯片制造出來,就能越早的去占據(jù)市場先機(jī)。在前端和后端的每個(gè)步驟和流程里,都需要用到各種各樣的EDA工具。

EDA工具舉例

新思科技是全球最大的EDA公司,比如拿它的EDA工具來舉例,看看芯片設(shè)計(jì)流程中需要用到多少個(gè)EDA工具。

比如要做一個(gè)簡單的加法電路,比如a+b=c,我們需要先用Verilog,或者VHDL這些硬件專用語言,把這個(gè)加法電路實(shí)現(xiàn)出來,為了驗(yàn)證加法的功能是不是正確,就要用EDA的仿真軟件,比如新思的VCS和VC Formal,讓a=1,b=1,看c是不是等于2。如果輸入1+1,結(jié)果等于3,那么就需要調(diào)試軟件,比如Verdi來確定問題出現(xiàn)在什么地方,還需要用到靜態(tài)和動態(tài)的分析軟件,比如SpyGlass來診斷分析電路是否有一些潛在的問題。如果代碼沒有問題就可以去編譯了,這在芯片設(shè)計(jì)里叫做綜合Synthesis。綜合的結(jié)果就是生成一堆互相連接的門電路,也叫做網(wǎng)表,這就需要使用專門的綜合工具 Design Complier綜合生成網(wǎng)表,再用IC Compiler做布局布線,用Prime Time做時(shí)序分析,用PrimePower做功耗優(yōu)化,用IC Validator做物理驗(yàn)證,用StarRC做寄生參數(shù)提取等等,最終生成一個(gè)符合設(shè)計(jì)要求,也符合晶圓代工廠要求的GDSII文件,這個(gè)文件就被拿去做流片生產(chǎn)。

上面介紹的這些EDA軟件,只是整個(gè)EDA工具庫的九牛一毛。規(guī)模比較大的芯片公司,都會根據(jù)自己具體的產(chǎn)品和技術(shù),在每個(gè)環(huán)節(jié)采用不同的工具,這種定制化的方法比較高效,但是對技術(shù)的要求比較高,只有大公司玩的起。其它中小規(guī)模的公司,可能就直接使用EDA廠商提供的完整方案了。比如Synopsys的Fusion Compiler,直接就能從RTL硬件語言到GDSII版圖一步到位。

EDA工具發(fā)展

整個(gè)芯片設(shè)計(jì)的流程里,用到了大量的EDA工具,DEA工具的好壞,對于芯片的性能功耗和面積(Performance, Power, Area, PPA)有決定性的影響。同樣一段代碼,不同的工具會做出截然不同的芯片,EDA的發(fā)展也不是一成而就的,而是經(jīng)歷了四個(gè)主要的階段,分別是計(jì)算機(jī)輔助設(shè)計(jì),計(jì)算機(jī)輔助工程,傳統(tǒng)EDA, AI加持的EDA。

在上世紀(jì)70年代的中期,人們就開始使用計(jì)算機(jī)來輔助芯片的晶體管版圖設(shè)計(jì),PCB電路板的布局布線,設(shè)計(jì)規(guī)則檢查等等這些相對簡單的工作。到80年代卡菲爾米德和林康維發(fā)表了《超大規(guī)模集成電路系統(tǒng)導(dǎo)論》,提出來使用編程語言來進(jìn)行芯片設(shè)計(jì)的的思想,這個(gè)也稱為了EDA發(fā)展的重要標(biāo)志。

在1986年和1987年,Verilog, VHDL這兩種硬件描述語言誕生,幾乎在同一時(shí)間,Aart de Geus博士發(fā)明了自動邏輯綜合技術(shù),來取代手動的設(shè)計(jì)工程,并且在1986年聯(lián)合創(chuàng)立了Synopsys新思科技,這也標(biāo)志著EDA工具開始走向了商業(yè)化。

從90年代到21世紀(jì)初期,在摩爾定律的指引下,晶體管的密度越來越高,設(shè)計(jì)流程也越來越復(fù)雜,EDA工具稱為了芯片設(shè)計(jì)的必選項(xiàng),也促進(jìn)了EDA工具的進(jìn)步,前面說的綜合仿真,布局布線技術(shù)等都在這個(gè)時(shí)期得到了飛速的發(fā)展,這些EDA工具也縮短了研發(fā)周期,提升了設(shè)計(jì)效率,從而反過來去促進(jìn)了芯片產(chǎn)業(yè)的技術(shù)革新,形成了正向反饋的螺旋式上升。

目前是AI加持的新時(shí)代,谷歌在Nature上發(fā)表的新文章,用深度學(xué)習(xí)技術(shù)去幫助芯片設(shè)計(jì),人類工程師需要幾個(gè)月去完成的工作,谷歌的AI僅需要6個(gè)小時(shí)就能達(dá)到相同或者近似的結(jié)果,新思科技也推出了一個(gè)名叫DSO.ai的技術(shù),可以用到新思所有的DEA工具上,并且在某個(gè)芯片的設(shè)計(jì)上可以獲得21%的功耗降低,18%的性能提升,并且把原本6個(gè)月的設(shè)計(jì)時(shí)間縮短成了1個(gè)月,那么我們猜想一下,加了AI buff的EDA工具,很可能就是芯片行業(yè)再次起飛的最大動力。

EDA發(fā)展規(guī)律

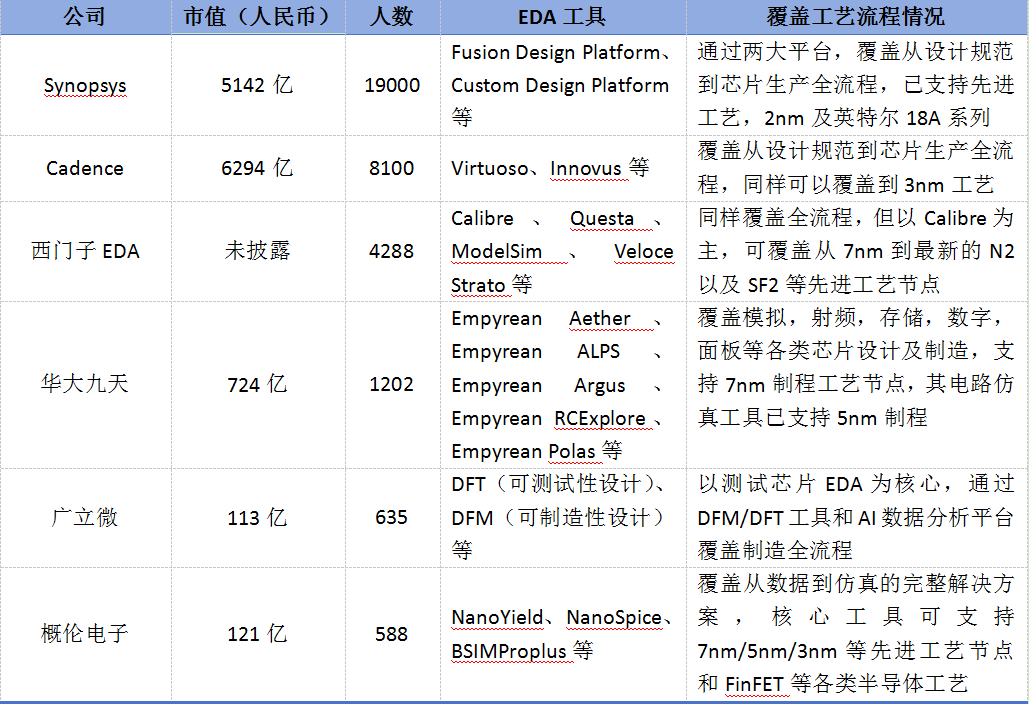

EDA如此重要,而全球的三大EDA領(lǐng)導(dǎo)者,占據(jù)了超過70%的全球市場份額,和接近80%的中國市場份額,他們是如何發(fā)展到今天的這種程度,中國的EDA產(chǎn)業(yè)又改如何迎頭趕上呢?從全球的EDA發(fā)展進(jìn)程來看,總結(jié)了四個(gè)可以借鑒的發(fā)展規(guī)律。

1)EDA需要大量的研發(fā)投入

EDA產(chǎn)業(yè)屬于典型的需要長期投入的領(lǐng)域,里面有大量的數(shù)學(xué)物理相關(guān)的基礎(chǔ)研究,國際學(xué)術(shù)界的四個(gè)頂級會議DAC, ASP-DAC, DATE,ICCAD里面討論的絕大部分都是從芯片設(shè)計(jì)里抽象出來的數(shù)學(xué)和算法問題,這些基礎(chǔ)研究都很難在短時(shí)間內(nèi)轉(zhuǎn)化成生產(chǎn)力。行業(yè)門檻很高,前期的投入產(chǎn)出比非常低,這就需要政府的大力支持。

EDA工具為了不斷實(shí)現(xiàn)技術(shù)革新也在大量的投入,比如新思科技有1.6W名員工,研發(fā)人員占據(jù)了80%,研發(fā)費(fèi)用占全年?duì)I收的35%。

2)EDA需要大量人才

和芯片行業(yè)類似,EDA人才從高校課題研究到行業(yè)的就業(yè),往往需要10年的時(shí)間,因此需要一套持久而健全的人次培養(yǎng)體系,除了前面所說的四大EDA頂會外,還有大量的EDA競賽,其實(shí)也都是在吸引和培養(yǎng)人才。

3)EDA需要建設(shè)完整生態(tài)

整個(gè)芯片設(shè)計(jì)過程需要晶圓廠,芯片公司,還有EDA廠商共同的去推進(jìn),很多物理參數(shù)的推進(jìn),需要晶圓廠和上下游的公司去深入的合作,獲得一手的數(shù)據(jù),所以說EDA串聯(lián)起了整個(gè)產(chǎn)業(yè)鏈。正因?yàn)槿绱耍裥滤歼@樣的EDA巨頭,還是世界上最大的IP提供商之一,特別是接口,模擬,嵌入式存儲和物理IP這些和工藝緊密綁定的領(lǐng)域。

4)EDA發(fā)展離不開并購擴(kuò)張

特別是很多細(xì)分的領(lǐng)域,自研的難度和成本都太高了,因此在自身產(chǎn)品市場足夠強(qiáng)大之后,可以去吸收和整合新公司和新技術(shù),從而實(shí)現(xiàn)快速的發(fā)展。對于國產(chǎn)EDA來說,有一個(gè)很好的發(fā)展機(jī)會,國家十四五規(guī)劃就明確提出,重點(diǎn)突破包括EDA在內(nèi)的工業(yè)軟件,2020年至今國內(nèi)成立了近50家EDA公司,也有4家在申請或者是已經(jīng)完成了IPO。

從上面發(fā)展的規(guī)律來看,肯定還會經(jīng)歷一波整合,雖然很那直接做到全產(chǎn)業(yè)鏈的完整方案,至少可以從細(xì)分領(lǐng)域進(jìn)入,從中低端制程切入,然后逐步的去迭代,形成更大的發(fā)展。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

436005 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1062瀏覽量

55461 -

eda

+關(guān)注

關(guān)注

71文章

2881瀏覽量

176429

原文標(biāo)題:【科普】EDA工具對芯片產(chǎn)業(yè)的重要性知識

文章出處:【微信號:feifeijiehaha,微信公眾號:電路和微電子考研】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

EDA禁令即將來襲!中國芯片產(chǎn)業(yè)迎背水一戰(zhàn)

西門子EDA斷供中國將如何沖擊國內(nèi)芯片產(chǎn)業(yè)?

新思科技引領(lǐng)EDA產(chǎn)業(yè)革新,展望2025年芯片與系統(tǒng)創(chuàng)新之路

STCO發(fā)展促使EDA工具考慮更多系統(tǒng)級因素

成都匯陽投資關(guān)于半導(dǎo)體產(chǎn)業(yè)基石,國產(chǎn)替代打破壟斷格局

艾偉達(dá)發(fā)布數(shù)字芯片EDA工具adsDesigner

英諾達(dá)推出兩款全新靜態(tài)驗(yàn)證EDA工具

PCBA加工中的靈魂:揭秘芯片燒錄的重要性

如何提升EDA設(shè)計(jì)效率

AI助力國產(chǎn)EDA,挑戰(zhàn)與機(jī)遇并存

可驗(yàn)證AI開啟EDA新時(shí)代,引領(lǐng)半導(dǎo)體產(chǎn)業(yè)變革

EDA工具對芯片產(chǎn)業(yè)的重要性知識

EDA工具對芯片產(chǎn)業(yè)的重要性知識

評論