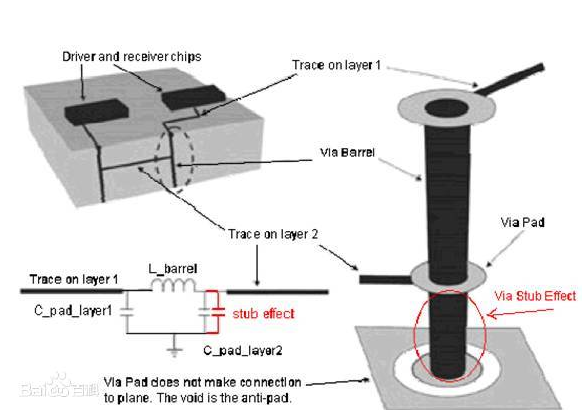

過孔的兩個寄生參數是寄生電容和寄生電感。

過孔本身存在著對地的寄生電容,如果已知過孔在鋪地層上的隔離孔直徑為D2,過孔焊盤的直徑為D1,PCB板的厚度為T,板基材介電常數為ε,則過孔的寄生電容可以近似用以下公式來計算:C=1.41εTD1/(D2?D1)。

過孔的寄生電容會給電路造成的主要影響是延長了信號的上升時間,降低了電路的速度。比如說,對于一塊厚度為50mil的PCB板,如果使用內徑為10mil,焊盤直徑為20mil的過孔,焊盤與地鋪銅區(qū)的距離為32mil,則可以通過上面的公式近似算出過孔的寄生電容大致是:C=1.41×4.4×0.050×0.020/(0.032?0.020)pF=0.517pF,這部分電容引起的上升時間變化量為:T10-90=2.2C(Z0/2)=2.2×0.517×(55/2)ps=31.28ps 。從這些數值可以看出,盡管單個過孔的寄生電容引起的上升沿變緩的效用不是很明顯,但是如果走線中多次使用過孔進行層間的切換,所產生的影響還是比較大的。

過孔存在寄生電容的同時也存在著寄生電感,在高速數字電路的設計中,過孔的寄生電感帶來的危害往往大于寄生電容的影響。它的寄生串聯電感會削弱旁路電容的貢獻,減弱整個電源系統(tǒng)的濾波效用。

我們可以用下面的公式來簡單地計算一個過孔近似的寄生電感:L=5.08h[ln(4h/d)+1]。其中,L是過孔的電感,h是過孔的長度,d是中心鉆孔的直徑。從公式中可以看出,過孔的直徑對電感的影響較小,而對電感影響最大的是過孔的長度。仍然采用上面的例子,可以計算出過孔的電感為:L=5.08×0.050[ln(4×0.050/0.010)+1]nH=1.015nH 。如果信號的上升時間是1ns,那么其等效阻抗大小為:XL=πL/T10-90=3.19?。這樣的阻抗在有高頻電流通過時已經不能忽略了。特別要注意,旁路電容在連接電源層和地層的時候需要通過兩個過孔,這樣過孔的寄生電感就會成倍增加。

為了消除過孔寄生電容與寄生電感所帶來的影響,可以采取如下措施:

? 選擇合理尺寸的過孔大小,如對6~10層的PCB設計來說,選用10/20mil(鉆孔/焊盤)的過孔較好,對于一些高密度的小尺寸板子,也可以嘗試使用8/18mil的過孔。

? 使用較薄的PCB板有利于減小過孔的兩種寄生參數。

? PCB板上的信號走線盡量不換層,也就是說盡量不要使用不必要的過孔。

? 電源和地的管腳要就近打過孔,過孔和管腳之間的引線越短越好,因為它們會導致電感的增加。同時,電源和地的引線要盡可能粗,以減少阻抗。

? 在信號換層的過孔附近放置一些接地的過孔,以便為信號提供最近的回路。甚至可以在PCB板上大量放置一些多余的接地過孔。

審核編輯 黃昊宇

-

寄生電容

+關注

關注

1文章

299瀏覽量

19791 -

過孔

+關注

關注

2文章

213瀏覽量

22282

發(fā)布評論請先 登錄

KiCad-Parasitics:KiCad 寄生參數分析插件

一文詳解寄生參數對柵極震蕩的影響

過孔的兩個寄生參數是什么?它有什么影響?應該怎么消除?

過孔的兩個寄生參數是什么?它有什么影響?應該怎么消除?

評論