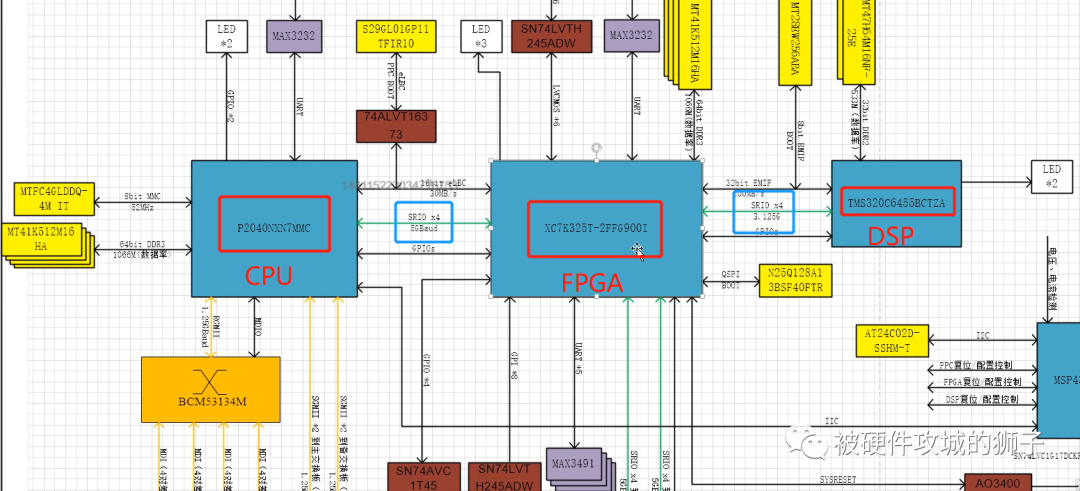

系統(tǒng)架構(gòu)確定,下一步就是FPGA與各組成器件之間互聯(lián)的問題了。通常來說,CPU和FPGA的互聯(lián)接口,主要取決兩個要素:

(1)CPU所支持的接口。

(2)交互的業(yè)務(wù)。

通常來說,F(xiàn)PGA一般支持與CPU連接的數(shù)字接口,其常用的有EMIF,PCI,PCI-E,UPP,網(wǎng)口(MII/GMII/RGMII),DDR等接口。作為總線類接口,F(xiàn)PGA通常作為從設(shè)備與CPU連接,CPU作為主設(shè)備通過訪問直接映射的地址對FPGA進(jìn)行訪問。根據(jù)是否有時鐘同步,通常總線訪問分為同步或異步的總線,根據(jù)CPU外部總線協(xié)議有所不同,但數(shù)據(jù)、地址、控制信號基本是總線訪問類型中總線信號所不能省略的。CPU手冊中會對信號定義和時序控制有著詳細(xì)的說明,F(xiàn)PGA需要根據(jù)這些詳細(xì)說明來實現(xiàn)相應(yīng)的邏輯。同時CPU還可以對訪問時序進(jìn)行設(shè)置,比如最快時鐘,甚至所需的最小建立時間和保持時間,這些一般CPU都可以進(jìn)行設(shè)置,而這些具體參數(shù),不僅影響FPGA的實現(xiàn),也決定總線訪問的速度和效率。對于同步總線,只需要根據(jù)輸入時鐘進(jìn)行采樣處理即可,但對于異步總線,則需要的對進(jìn)入的控制信號進(jìn)行同步化處理,通常處理方式是寄存兩拍,去掉毛刺。因此用于采樣的時鐘就與CPU所設(shè)置的總線參數(shù)相關(guān),如采樣時鐘較低,等控制信號穩(wěn)定后在譯碼后輸出,一個總線操作周期的時間就會相對較長,其處理的效率也相對較低;假如采樣時鐘過快,則對關(guān)鍵路徑又是一個挑戰(zhàn),因此合理設(shè)定采樣頻率,便于接口的移植并接口的效率是設(shè)計的關(guān)鍵點和平衡點。

對于總線型的訪問來說,數(shù)據(jù)信號通常為三態(tài)信號,用于輸入和輸出。這種設(shè)計的目的是為了減少外部連線的數(shù)量。因為數(shù)據(jù)信號相對較多一般為8/16/32位數(shù)據(jù)總線。總線的訪問的優(yōu)勢是直接映射到系統(tǒng)的地址區(qū)間,訪問較為直觀。但相對傳輸速率不高,通常在幾十到100Mbps以下。這種原因的造成主要為以下因素(1)受制總線訪問的間隔,總線操作周期等因素,總線訪問間隔即兩次訪問之間總線空閑的時間,而總線操作周期為從發(fā)起到相應(yīng)的時間。(2)不支持雙向傳輸,并且FPGA需主動發(fā)起對CPU操作時,一般只有發(fā)起CPU的中斷處理一種方式。這種總線型操作特點,使其可以用作系統(tǒng)的管理操作,例如FPGA內(nèi)部寄存器配置,運行過程中所需參數(shù)配置,以及數(shù)據(jù)流量較小的信息交互等操作。這些操作數(shù)據(jù)量和所需帶寬適中,可以應(yīng)對普通的嵌入式系統(tǒng)的處理需求。

對于大數(shù)據(jù)流量的數(shù)據(jù)交互,一般采用專用的總線交互,其特點是,支持雙向傳輸,總線傳輸速率較快,例如GMII/RGMII、Upp、專用LVDS接口,及 SERDES接口。專用SERDES接口一般支持的有PCI-E,XAUI,SGMII,SATA,Interlaken接口等接口。GMII/RGMII,專用LVDS接口一般處理在1GbpS一下的業(yè)務(wù)形式,而PCI-E,根據(jù)其型號不同,支持幾Gbps的傳輸速率。而XAUI可支持到10Gbps的傳輸速率,lnterlaken接口可支持到40Gbps的業(yè)務(wù)傳輸。

對于不同所需的業(yè)務(wù)形式及處理器的類型,則可選擇相應(yīng)的接口形式,來傳輸具體的業(yè)務(wù)。現(xiàn)今主流FPGA中都提供的各種接口的IP。選擇FPGA與各型CPU互聯(lián)接口,一般選擇主流的應(yīng)用交互方案,特殊的接口缺少支撐IP,導(dǎo)致開發(fā)、調(diào)試、維護(hù)和兼容性的成本都較大,同時注意系統(tǒng)的持續(xù)演進(jìn)的需要,如只在本項目使用一次,而下一項目或開發(fā)階段已摒棄此類接口,則需提前規(guī)劃技術(shù)路線。畢竟一個穩(wěn)定、高效的接口互聯(lián)是一個項目成功的基礎(chǔ)。

不是所有的嵌入式系統(tǒng)都需要“高大上”的接口形式,各類低速的穩(wěn)定接口也同樣在FPGA的接口互聯(lián)中有著重要的角色,其中UART、SPI、I2C等連接形式也非常的常見。畢竟,一個優(yōu)秀的設(shè)計不是“高大上”的堆積,而是對需求最小成本的滿足。適合的才是最美的。

FPGA與各組成器件之間互聯(lián) - FPGA的系統(tǒng)架構(gòu)組成和器件互聯(lián)問題---FPGA通常作為從設(shè)備與CPU連接

Serial RapidIO (SRIO)與PCIE

1.1 與PCIe的差異

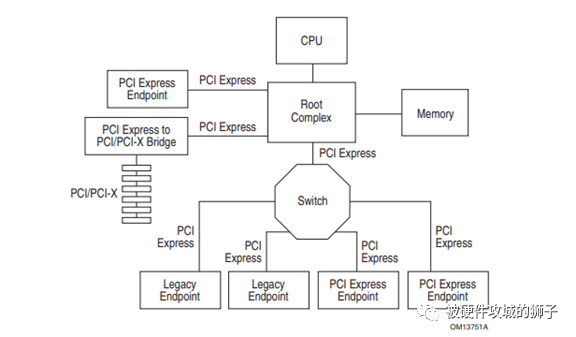

典型的PCIe結(jié)構(gòu)定義了一個以單個中央處理器為核心的計算機系統(tǒng),比如我們常見的工控機、PXIe機箱控制器、服務(wù)器內(nèi)的IO設(shè)備。從系統(tǒng)架構(gòu)來看,這個結(jié)構(gòu)的優(yōu)勢在于可有統(tǒng)一的軟件驅(qū)動,軟件模型,設(shè)備間具備優(yōu)異的兼容性。兼容性才是王道,廠商就可以用一個標(biāo)準(zhǔn)包打天下。

圖 1?1 PCIe 互聯(lián)架構(gòu)

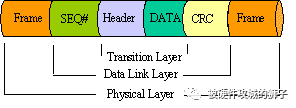

PCIe 的幀格式如下圖所示。幀由 1 字節(jié)的幀起始、2 字節(jié)的序列號、16 或 20 字節(jié)的報頭、0 到 4096 字節(jié)的數(shù)據(jù)字段、0 到 4 字節(jié)的 ECRC 字段、4 字節(jié)的 LCRC、和 1 字節(jié)的幀結(jié)束。數(shù)據(jù)字段中傳輸?shù)奈粩?shù)越少,開銷就越大。零字節(jié)數(shù)據(jù)字段會導(dǎo)致 100% 的開銷,因為沒有傳輸數(shù)據(jù)。

圖 1?2 幀格

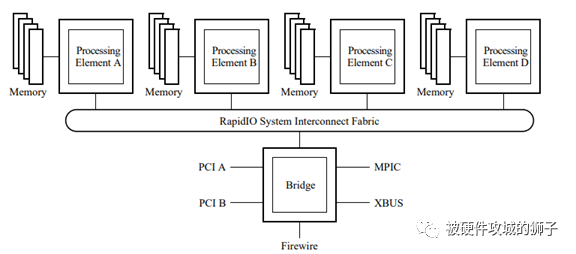

RapidIO定義了一種高性能、分組交換互連技術(shù),用于在微處理器、DSP、通信和網(wǎng)絡(luò)處理器、系統(tǒng)內(nèi)存和外圍設(shè)備之間傳遞數(shù)據(jù)和控制信息。RapidIO 適用于點對點的設(shè)備間通訊,不需要經(jīng)過一個中央處理器進(jìn)行調(diào)度,就可以完成設(shè)備間的通訊,并且包長度簡單,效率相對于PCIe要更高,有效數(shù)據(jù)傳輸速度更快。但是RapidIO沒有定義標(biāo)準(zhǔn)的軟件模型,這就導(dǎo)致廠家之間的設(shè)備大概率無法兼容,從而只能在某些領(lǐng)域進(jìn)行部署,不易推廣。

圖 1?3 RapidIO 互聯(lián)架構(gòu)

RapidIO 由于比PCIe更簡單、更高效、延遲更低等特點,已經(jīng)在嵌入式領(lǐng)域、圖像處理、通訊系統(tǒng)、軍工航天有了大量的應(yīng)用。

我們來看一個應(yīng)用場景,在醫(yī)學(xué)影像等圖像處理領(lǐng)域,經(jīng)常需要擴展單塊DSP、FPGA的計算能力,這時候需要將多個DSP或者FPGA通過高速串口進(jìn)行互聯(lián),此時RapidIO就是當(dāng)前互換性最好的一個最佳選擇,因為PCIe太過復(fù)雜,Xilinx的Auraro效率也不滿足要求,并且互換性不好。

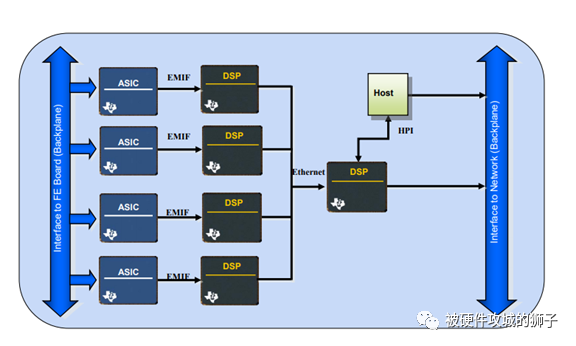

我們來看一下在RapidIO之前,實現(xiàn)多個DSP系統(tǒng)互聯(lián)的方法:

圖 1?4 多個DSP設(shè)備通過網(wǎng)絡(luò)互聯(lián)

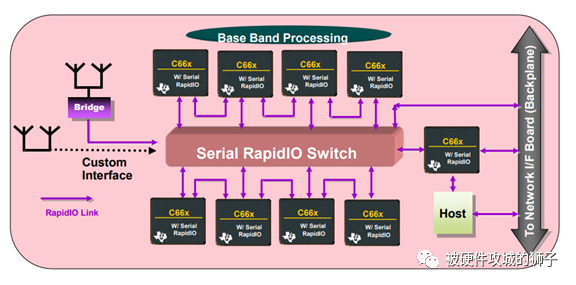

圖 1?5 多個DSP設(shè)備可以通過RapidIO 實現(xiàn)任意互聯(lián)通訊

2 可用的驗證硬件

目前具備SRIO接口的硬件不多,我們推薦2類可用的開發(fā)板:

1、創(chuàng)龍科技開發(fā)的TI DSP開發(fā)板 也可用于評估EMIF等接口

2、Xilinx 的KC705等具備高速GTX/GTP接口的開發(fā)板,Xilinx提供了兼容SRIO 2.2的IP可供評估;

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613910 -

cpu

+關(guān)注

關(guān)注

68文章

11031瀏覽量

215931 -

Xilinx

+關(guān)注

關(guān)注

73文章

2181瀏覽量

124314

原文標(biāo)題:2???? 可用的驗證硬件

文章出處:【微信號:被硬件攻城的獅子,微信公眾號:被硬件攻城的獅子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

FPGA的系統(tǒng)架構(gòu)組成和器件互聯(lián)問題

FPGA研發(fā)之道(2)FPGA和他那些小伙伴們(二)器件互聯(lián)

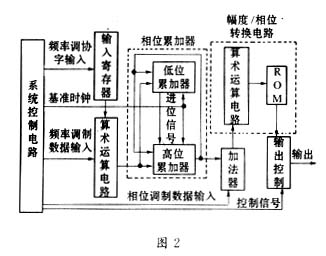

一種基于FPGA的PLL數(shù)頻率合成器設(shè)計

如何利用FPGA設(shè)計PLL頻率合成器?

三極管、二極管、運放各組成的恒流源電路

請問怎么采用FPGA和集成器件來實現(xiàn)IJF編碼?

基于FPGA的直接數(shù)字頻率合成器的設(shè)計

基于FPGA的直接數(shù)字頻率合成器的設(shè)計和實現(xiàn)

基于FPGA的直接數(shù)字頻率合成器的設(shè)計和實現(xiàn)

數(shù)字頻率合成器的FPGA實現(xiàn)

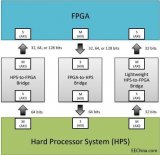

FPGA與HPS之間互聯(lián)的結(jié)構(gòu)

FPGA的組成架構(gòu)、類型及應(yīng)用講解

陶瓷電容的ESR的各組成電阻介紹資料下載

FPGA與各組成器件之間互聯(lián)的問題

FPGA與各組成器件之間互聯(lián)的問題

評論