選擇性外延工藝

通過圖形化硅氧化或氮化硅掩蔽薄膜生長,可以在掩蔽膜和硅暴露的位置生長外延層。這個過程稱為選擇性外延生長(SEG)。

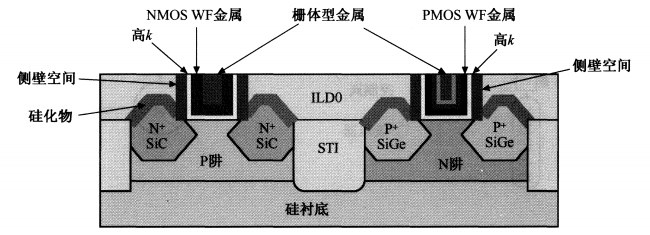

下圖顯示了利用SEG SiC形成NMOS拉伸應(yīng)變溝道,以及利用SEG SiGe形成PMOS壓縮應(yīng)變溝道。

多晶硅沉積

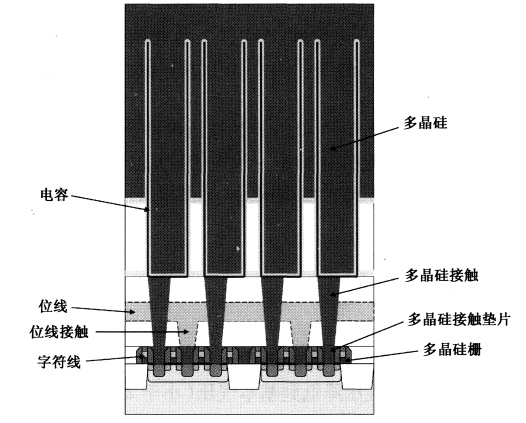

自從20世紀(jì)70年代中期離子注入被引入IC生產(chǎn)中作為硅摻雜工藝后,多晶硅就作為柵極材料使用,同時也廣泛用于DRAM芯片的電容器電極。

下圖顯示了多晶硅在先進DRAM 芯片上的應(yīng)用。

硅化物疊在第一層多晶硅(Poly 1)上形成柵電極和局部連線,第二層多晶硅(Poly 2)形成源極/漏極和單元連線之間的接觸栓塞。

硅化物疊在第三層多晶硅(Poly 3)上形成單元連線,第四層多晶硅(Poly 4)和第五層多晶硅(Poly 5)則形成儲存電容器的兩個電極,中間所夾的是高介電系數(shù)的電介質(zhì)。

為了維持所需的電容值,可以通過使用高介電系數(shù)的電介質(zhì)減少電容的尺寸。

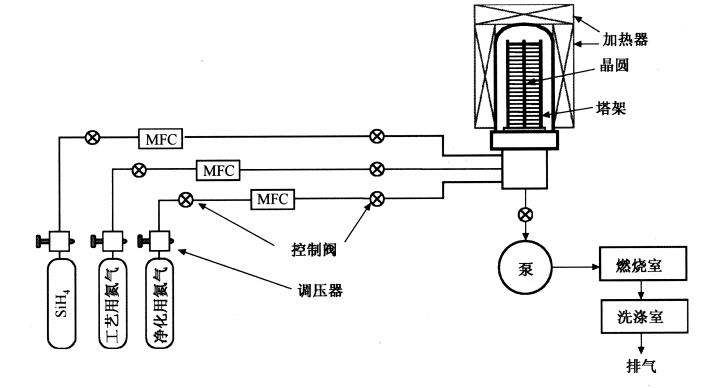

多晶硅沉積是一種低壓化學(xué)氣相沉積(UPCVD), 一般在真空系統(tǒng)的爐管中進行(見下圖) 。

多晶硅沉積一般釆用硅烷(SiH4)化學(xué)反應(yīng)。高溫條件下硅烷將分解并在加熱表面形成硅 沉積,該化學(xué)反應(yīng)可以表示如下:

SiH4 --> Si+2H2

多晶硅也可以使用二氯W(SiH2Cl2, DCS)的化學(xué)反應(yīng)形成沉積。高溫狀態(tài)下DCS將和氫反應(yīng)并在加熱表面形成硅沉積,DCS過程需要的沉積溫度比硅烷過程高。

DCS的化學(xué)反應(yīng)為:

SiH2Cl2+H2 --> Si+2HCl

通過在反應(yīng)室內(nèi)(即爐管中)將三氫化碑(ah3 )、三氫化磷(PH3)或二硼烷的摻雜氣體直接輸入硅烷或DCS的硅材料氣體中,就可以進行臨場低壓化學(xué)氣相沉積(LPCVD)的多晶硅摻雜過程。

一般情況下,多晶硅沉積是在0.2-1 Torr的低壓條件及600 ~650攝氏度之間的沉積溫度下進行,使用純硅烷或以氮氣稀釋后純度為20% ~30%的硅烷。

這兩種沉積過程的沉積速率都在100?200A/min之間,主要由沉積時的溫度決定。晶圓內(nèi)的薄膜厚度不均勻性低于4%。

多晶硅沉積過程如下:

?系統(tǒng)閑置時注入吹除凈化氮氣

?系統(tǒng)閑置時注入工藝氮氣

?注入工藝氮氣并載入晶圓

?注入工藝氮氣并降下反應(yīng)爐管(鐘形玻璃罩)

?關(guān)掉氮氣,抽真空使反應(yīng)室氣壓降低到基本氣壓(小于2 mTorr)

?注入氮氣并穩(wěn)定晶圓溫度、檢查漏氣

?關(guān)掉氮氣,抽真空使氣壓回升到基本氣壓(小于2 mTorr)

?注入氮氣并設(shè)置工藝過程所需的氣壓(約250 mTorr)

?開啟SiH4氣流并關(guān)掉氮氣,開始沉積

?關(guān)掉硅烷氣流并打開柵極活塞,抽真空使氣壓回升到基本氣壓

?關(guān)閉柵極活塞,注入氮氣并將氣壓提高到一個大氣壓力

?注入氮氣降低晶圓溫度,然后升起鐘形玻璃罩

?注入工藝氮氣并卸載晶圓 ?

?系統(tǒng)閑置時注入吹除凈化氮氣

LPCVD多晶硅沉積過程主要由工藝溫度、工藝壓力、稀釋過程的硅烷分壓及摻雜物的濃度決定。雖然晶圓的間距和負載尺寸對沉積速率的影響較小,但對晶圓的均勻性相當(dāng)重要。

多晶硅薄膜的電阻率很大程度上取決于沉積時的溫度、摻雜物濃度及退火溫度,而退火溫度又會影響晶粒的大小。

增加沉積溫度將造成電阻率降低,提高摻雜物濃度會降低電阻率,較高的退火溫度將形成較大尺寸晶粒,并使電阻率隨之下降。

多晶硅的晶粒尺寸越大,其刻蝕工藝就越困難,這是因為大的晶粒尺寸將造成粗糙的多晶側(cè)壁,所以必須在低溫下進行多晶硅沉積以獲得較小的晶粒尺寸,經(jīng)過多晶硅刻蝕和光刻膠剝除,再經(jīng)過高溫退火形成較大的晶粒尺寸和較低的電阻率。

某些情況是在450攝氏度左右沉積非晶態(tài)硅后再進行圖形化、刻蝕及退火,最后形成具有更大、更均勻晶粒尺寸的多晶硅。

審核編輯:劉清

-

電容器

+關(guān)注

關(guān)注

64文章

6525瀏覽量

101833 -

DRAM芯片

+關(guān)注

關(guān)注

1文章

88瀏覽量

18267 -

PMOS

+關(guān)注

關(guān)注

4文章

266瀏覽量

30305

原文標(biāo)題:半導(dǎo)體行業(yè)(一百三十三)——加熱工藝(十四)

文章出處:【微信號:FindRF,微信公眾號:FindRF】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

半導(dǎo)體選擇性外延生長技術(shù)的發(fā)展歷史

選擇性焊接的工藝流程及特點

PCB選擇性焊接技術(shù)介紹

PCB選擇性焊接技術(shù)詳細

PCB選擇性焊接工藝難點解析

深度解析PCB選擇性焊接工藝難點

PCB選擇性焊接工藝難點解析

PCB板選擇性焊接工藝

PCB選擇性焊接的工藝特點及流程

選擇性焊接工藝技術(shù)的研究

半導(dǎo)體工藝之氣相外延介紹

半導(dǎo)體前端工藝:刻蝕——有選擇性地刻蝕材料,以創(chuàng)建所需圖形

半導(dǎo)體之選擇性外延工藝介紹

半導(dǎo)體之選擇性外延工藝介紹

評論