引言:傳輸線沿其長度定義并控制特性阻抗。然而,它們接口的三維結構在信號路徑上沒有容易定義的或恒定的阻抗。計算10Gb/s信號通過這些結構時所看到的阻抗,需要3D場解算器等軟件工具,而2D場解算器足以計算傳輸線特性阻抗。PCB設計人員可以使用本章中的分析和示例來輔助此類通道的設計。本章未涉及的案例可能需要進一步仿真和分析。

1.冗余電容和電感

大多數差分躍遷都是通過電容。P和N路徑相互耦合,增加了電容。許多躍遷在寬頻帶上具有與集總電容相同的頻率響應。通過設計,增加電感可以抵消這種過剩。 通過設計,除了受到密度和物理限制的影響外,在許多情況下,增加電感可以消除這種過剩電容。雖然盲孔、較大間距的焊球和非常小的通孔焊盤等技術降低了電容,但它們在設計中并不總是可行的。 時域反射(TDR)技術,無論是通過仿真還是測量,都允許設計者識別過渡過程中的冗余電容或電感。

2.時域反射法(TDR)

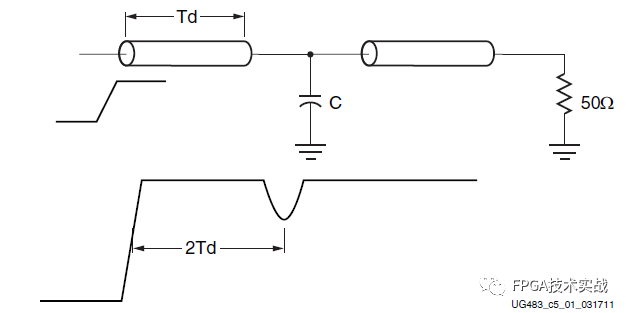

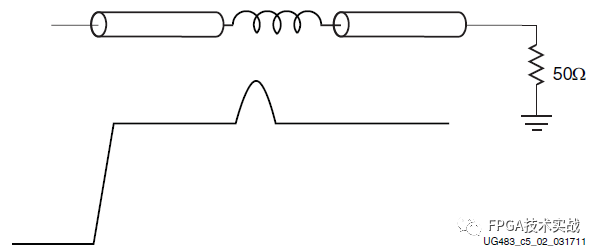

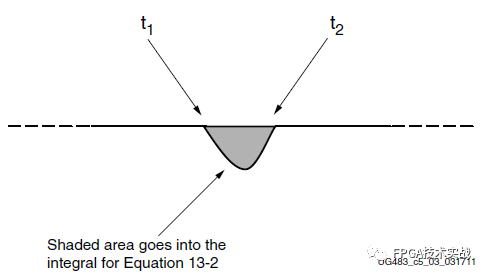

為了進行TDR測量,將階躍輸入應用于互連。通過觀察反射信號,可以確定電壓階躍穿過互連時所經歷的冗余電容或電感的位置和大小。 并聯電容(見圖1)會導致阻抗的瞬時下降,而串聯電感(見圖2)則會導致相反方向的阻抗不連續。Td是通過左側第一個傳輸線段的傳播延遲。由于阻抗不連續而產生的反射波需要2*Td才能返回TDR端口。如果信號通過傳輸線的傳播速度已知,則可以計算出沿通道的冗余電容或電感的位置。

圖1、并聯電容的TDR特征

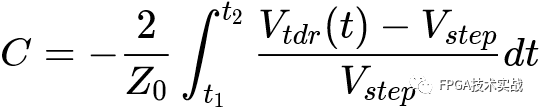

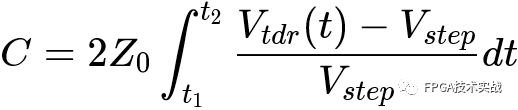

圖2、串聯電感的TDR特征 這種冗余電容(C)或電感(L)的大小也可以通過積分躍遷的TDR的歸一化面積從TDR波形中提取反應。反應電容和電感的相應方程式為:

????????????????????????? ?(式1)

????????????????????????? ?(式1)

?????????????????????????? (式2)

?????????????????????????? (式2)

圖3顯示了歸一化TDR區域的積分。

圖3、歸一化TDR面積的積分

利用這些方程得到的結果對上升時間變化不敏感,并且對于仿真TDR測量是有效的,前提是前后傳輸線非常接近50Ω。然而,對于實際測量,精度非常依賴于Z0。

3.BGA封裝

BGA封裝中的每個信號路徑都經過精心設計,以優化信號完整性。支持單端I/O的走線通常設計為50Ω的阻抗。支持高速SERDES I/O的走線設計為標稱100Ω差分阻抗。在設計信號路徑時要特別小心,以優化不連續性,如焊球和基板過孔,以盡量減少它們對信號完整性的影響。采用三維全波電磁解算器和矢量網絡分析儀對封裝性能進行建模和測量。

4.SMT焊盤

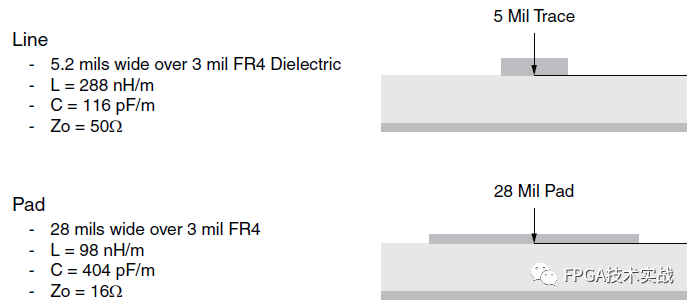

對于需要在發送器和接收器之間進行交流耦合的應用,在通道中引入SMT焊盤以允許安裝耦合電容器。標準SMT焊盤由于對附近基準面的板電容而具有冗余電容。在圖4示例中,一個5 mil的走線(Z0為50Ω)過渡到一個0402 SMT焊盤,其寬度為28 mils,全部超過3 mils的FR4。

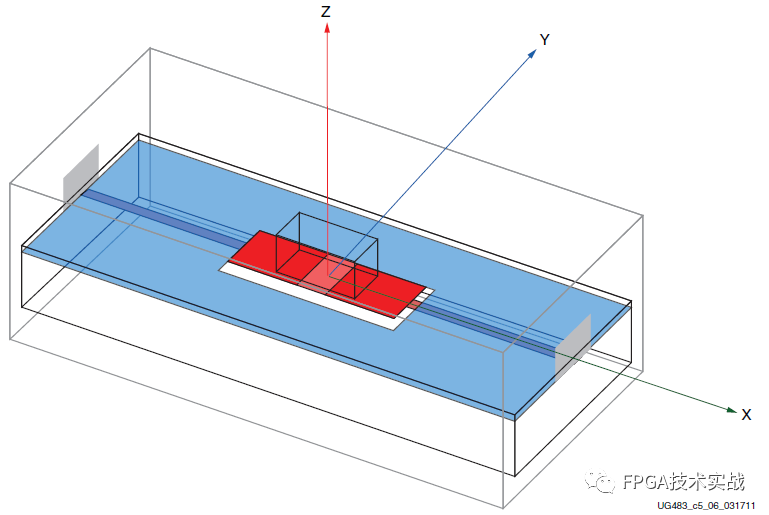

圖4、5 Mil走線和28 Mil焊盤的2D場解算器分析 在這些尺寸上使用2D場解算器,5mil走線的Z0為50Ω。0402焊盤的Z0為16Ω,因為焊盤的電容太大,電感太小,導致阻抗小于50Ω。此轉換的性能可以通過以下兩種方式之一進行優化。 第一種方法使走線與焊盤的寬度相同,并將接地層移到層疊中更深的位置,以將過渡段的Z0保持在50Ω。這種方法不需要任何特殊的分析,但由于貼片電容器體的邊緣電容會產生一定的誤差。走線密度是有限的,因為走線現在是28mil寬。 第二種方法,如圖5所示,清除焊盤下方的接地層,從而消除焊盤和接地層之間的板電容引起的大量多余電容。這種技術允許比第一種方法更大的走線密度,但需要三維場解算器分析或測量以及幾個電路板迭代來獲得所需的性能。

圖5、傳輸優化 二維場解算器的例子表明,如果清除焊盤走線下的地平面,可以獲得接近50Ω的電阻。然后使用三維場解算器在更大程度上驗證該結果準確。圖6所示的地平面與二維模擬時完全相同。在HFSS中使用頻域分析,使用這種技術可以使回波損耗提高20dB(10x)。

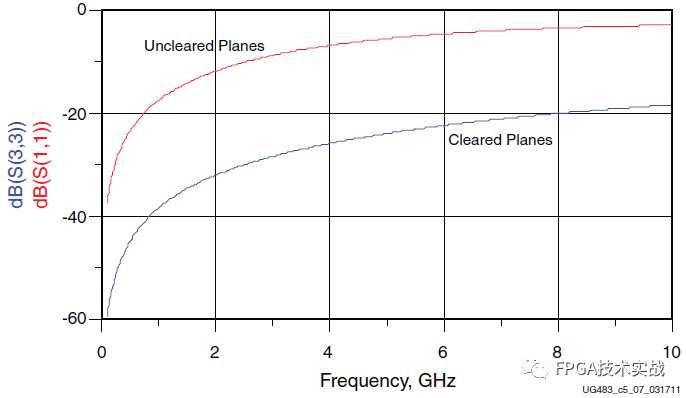

圖6、Pad清除的Ansoft HFSS模型 圖7顯示了0402焊盤結構與線性比例之間的回波損耗比較。

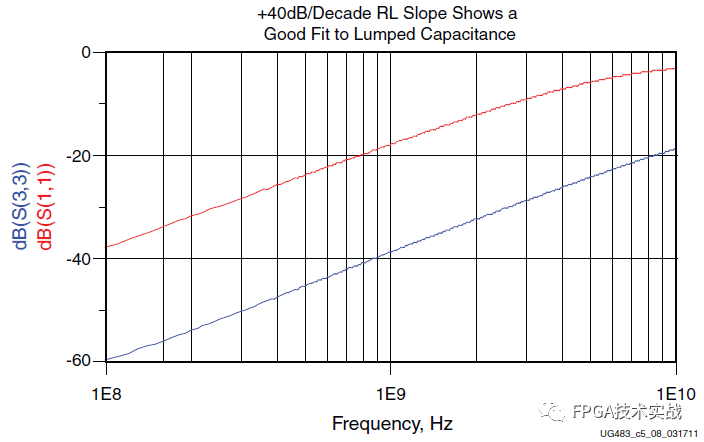

圖7、0402焊盤結構的回波損耗比較 圖8中約-40 dB/decade的斜率與集總電容器的頻率響應非常吻合。

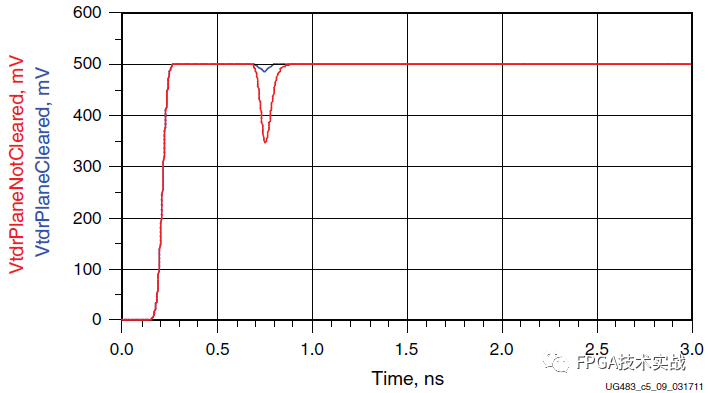

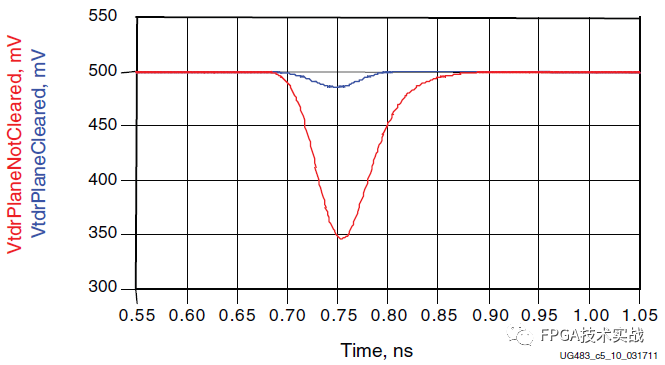

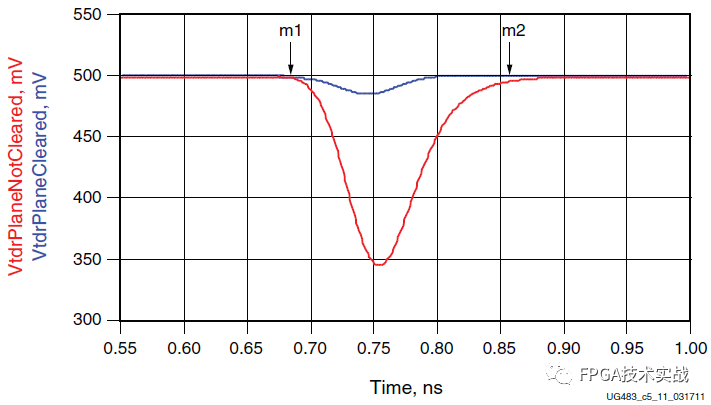

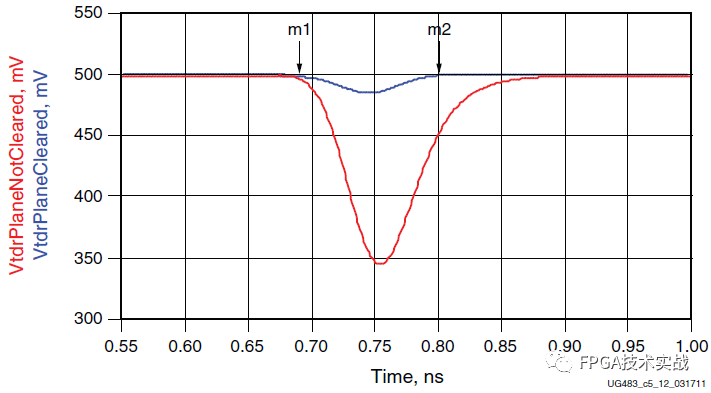

圖8、0402焊盤結構在對數(頻率)尺度上的回波損耗比較 接下來,使用HFSS中模擬的同一躍遷的仿真測量,可以通過對早期頻域分析的S參數結果進行TDR來測量該躍遷的時域性能。 在圖9和圖10中,具有大電容傾角的紅色曲線對應于SMT焊盤,而沒有從下面清除接地層。藍色曲線顯示,清除接地層可以去除大部分多余的電容。這種改進可以用等式1和等式2進行量化。

圖9、0402焊盤結構的TDR結果對比

圖10、0402焊盤結構的TDR結果對比

圖11、接地層完好時840 fF的過剩電容

圖12、57 fF接地層完整時的過剩電容

5. 差分過孔

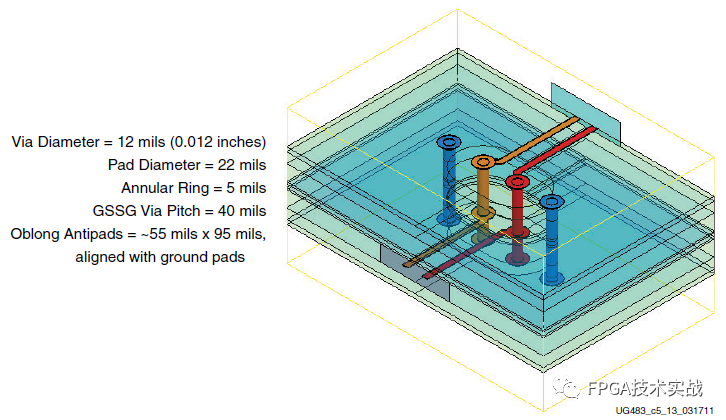

最常見的傳輸是差分過孔,其中信號對必須從上帶狀線層或頂部微帶過渡到下帶狀線層或底部微帶。 圖13所示為接地信號接地(GSSG)型差分通孔。接地過孔連接到層疊中的每個接地層,而信號層僅包含入口層和出口層的焊盤。

圖13、差分通孔設計示例

GSSG通孔的一個關鍵優點是,它允許信號的返回電流在相應信號通孔附近的接地過孔中流動,從而減少過大的電感。信號路徑在差分信號的P和N半部分之間也是對稱的,這對于控制由于P/N不平衡引起的共模偽影是至關重要的。

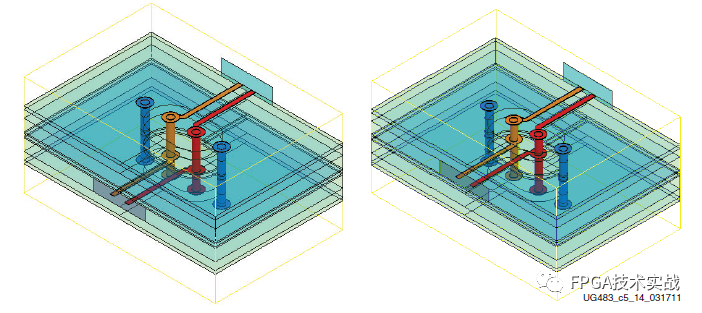

較大的長方形反焊盤減少過孔體和周圍平面邊緣之間的多余邊緣電容。未使用的焊盤也會被移除。 一個好的起點是使用圖13所示的尺寸作為80mil的差分過孔設計示例。為了適應密度約束或缺乏密度約束,可以相應地縮放尺寸,以保持每個尺寸相對于其他尺寸的比率。這種縮放保持了差分過孔的阻抗性能,同時允許總尺寸的變化以更好地適應特定應用。這些最終尺寸受到可制造性和密度約束的限制。 雖然通孔長度可以少量改變,以適應比80mil更厚或更薄的板示例,但是改變過孔長度相對于其他尺寸的比率會影響過孔的阻抗。對于差分過孔的這種和其他配置,最好使用三維場解算器工具模擬模型,以確保達到性能目標。

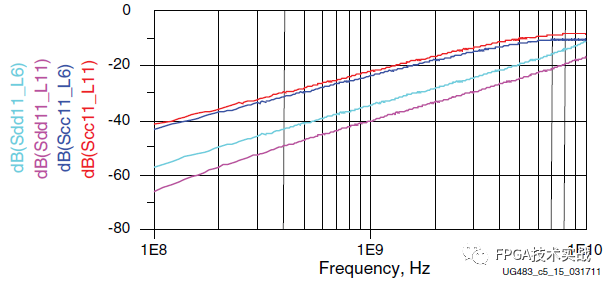

圖14、引腳L11和L6的16層PCB中的差分GSSG過孔 作為一般規則,P和N路徑在傳輸過程中需要保持相等的長度。在可能的情況下,通過將信號穿過過孔的整個長度,應將通孔存根(sub)長度保持在最小值。圖5-15所示的分析比較了共模(SCC11)和差分(SDD11)響應的S參數回波損耗。

圖15、比較L11和L6 GSSG過孔的差模和共模損耗的模擬回波損耗

從圖15中的圖表來看,共模響應在回波損耗方面差20 dB。與差分響應相比,共模響應差得多,這就是為什么在進入傳輸之前盡可能減少P/N偏差是一個好主意的原因。60/40的經驗法則是1 GHz時40 dB的回波損耗,這意味著60 fF的過剩電容。因為過剩電容是單極響應,所以可以使用簡單的外推規則。例如,如果返回損耗移到34 dB,則多余電容將增加一倍。由于GSSG通孔的優異性能,即使是長通孔存根也最多只能使差分通孔的電容增加一倍。

6. P/N交叉過孔

一些收發器提供獨立切換發送和接收信號對極性的能力。此功能消除了在板級交叉P/N信號的需要,從而顯著增強了信號完整性。如果可能,應避免P/N交叉過孔,并應使用收發器的極性開關。

7. SMA連接器

設計良好的SMA連接器可以減少調試時間,并允許在第一次通過時正確設計高性能通道。為了達到這一性能目標,需要對10Gb/s下性能良好的形狀記憶合金連接器進行模擬、設計和制造。供應商還可以提供設計服務,確保連接器在特定板上正常工作。裝配指南對于確保連接器與電路板的匹配過程得到良好控制以提供指定的性能至關重要。

Xilinx使用Rosenberger和其他精密連接器制造商生產的精密SMA連接器,因為它們具有優異的性能和上一段中列出的要點。

8. 背板連接器

背板連接器存在許多信號完整性問題,包括:

P/N信號偏差

串擾

連接器引腳導致的短截線

一些連接器制造商不僅提供連接器的參數、模型和布局指南,還提供設計支持、研討會和教程。

9. 微帶/帶狀線彎曲

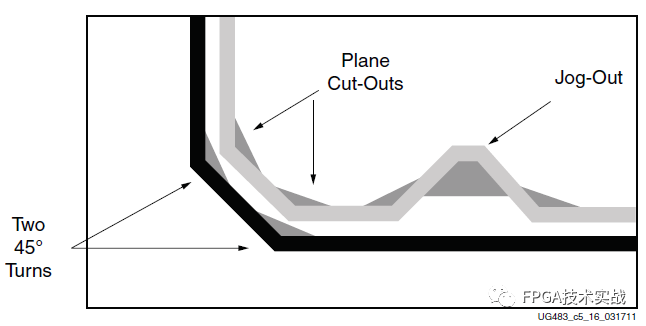

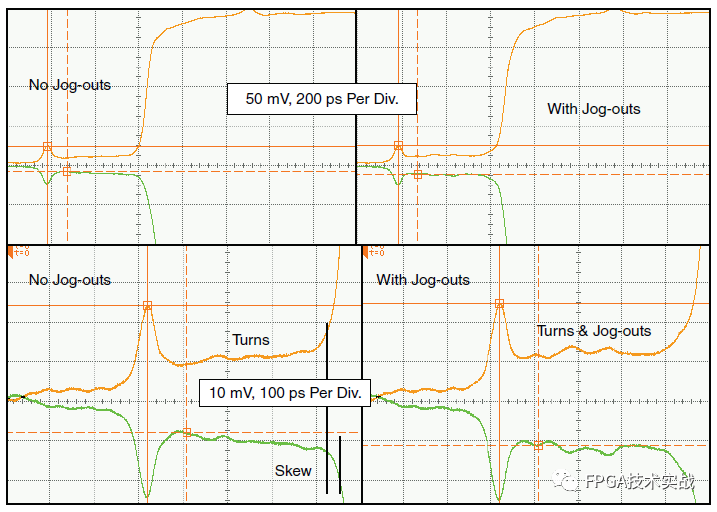

當差分走線通過90°角時,外部走線比內部走線長,這會導致P/N不平衡。即使在一個單一的走線內,信號電流也有擁抱拐角內側走線的趨勢,從而進一步減少通過彎道的實際延遲。 為了使P和N路徑之間的傾斜最小化,微帶線或帶狀線中的90°匝被布置為兩個45°彎曲以提供斜角。添加一個jog out還允許跟蹤長度匹配。圖16顯示了走線中的彎曲示例。

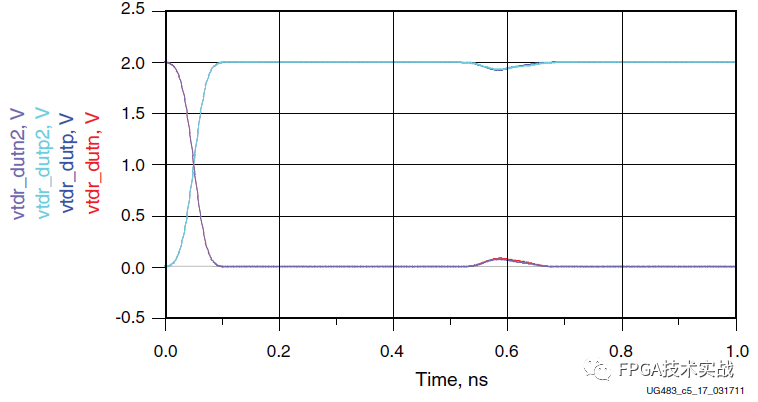

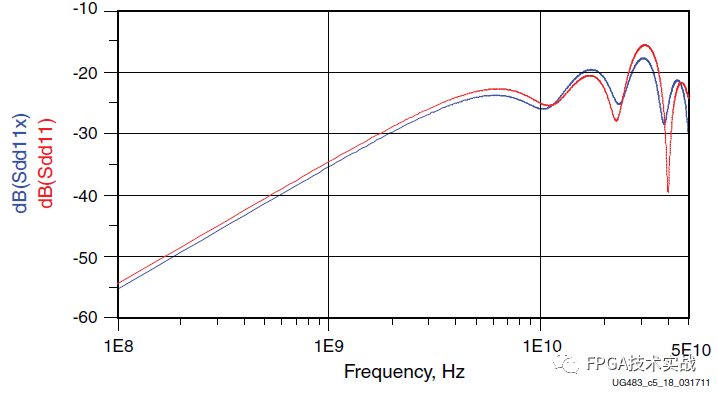

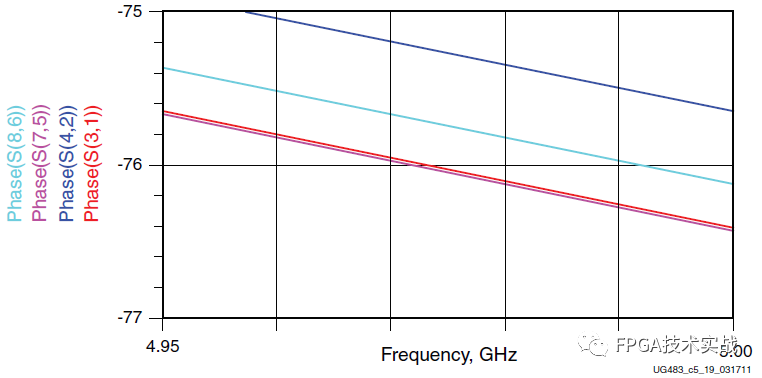

圖16、走線中90度轉彎的設計示例 匝數增加了電容,因為90°角處的走線寬41%。45°轉彎時,差值減小到8%。在30mil的深度上增加平面開孔可以減少多余的電容量。 當用緩動切口和平面切口仿真這種斜接彎曲時,減少了多余電容,改善了P/N長度和相位匹配。如果沒有Jog-out,P/N長度不匹配為16mil。給定FR4材料,16mil的差異轉化為5Ghz下有4.8°的相位失配,或10Gb/s下2.68ps(0.0268ui)。 圖17至圖19顯示,相位失配減少到0.75°,使用緩動器和Jog-out,相位失配減少到0.3°。結合緩動和Jog-out的仿真結果表明,該結構的剩余電容減小到65fF。 設計人員試圖加寬線路,以補償由于線路分離和耦合不太強烈而增加的特性阻抗。然而,即使沒有加寬線路,轉角和Jog-out的組合電容仍然是過電容的,因此緩動輸出的非耦合部分不能加寬。

圖5-17:帶有Jog-out的45度轉彎的仿真TDR

圖18、帶有Jog-ou的45度轉彎的仿真回波損耗

圖5-19:帶有Jog-out的45度轉彎的仿真相位響應

圖20、45度轉彎的測量TDR,帶和不帶折彎

-

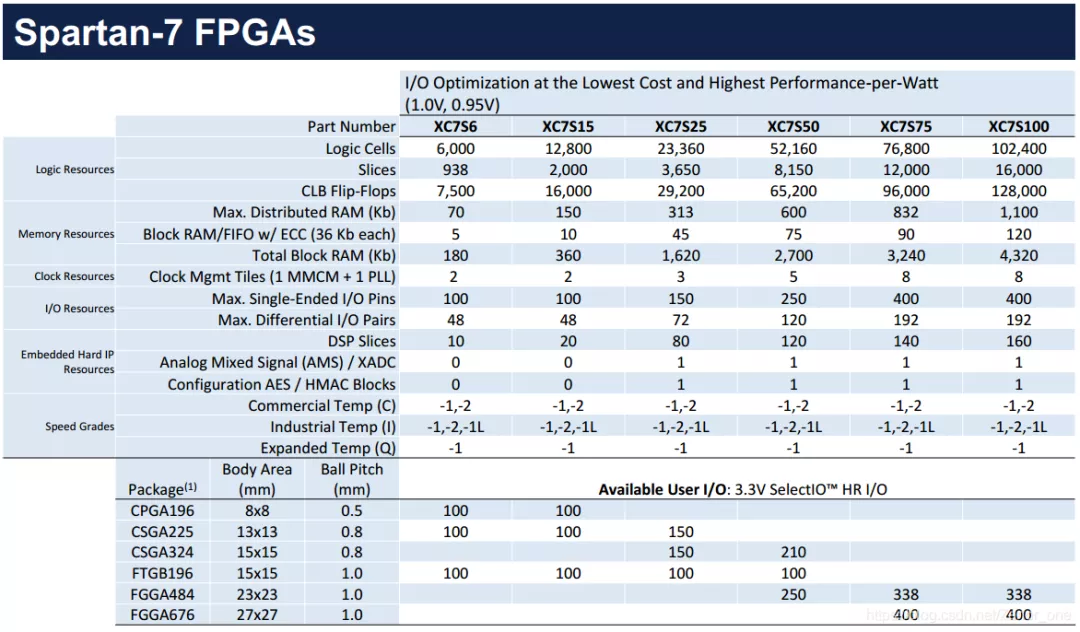

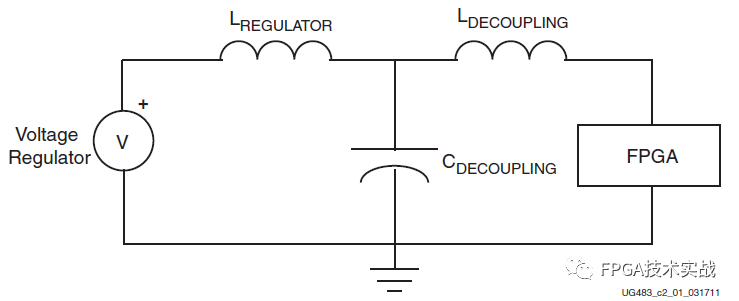

FPGA

+關注

關注

1643文章

21952瀏覽量

613826 -

pcb

+關注

關注

4350文章

23403瀏覽量

406488 -

Xilinx

+關注

關注

73文章

2181瀏覽量

124288

原文標題:Xilinx 7系列FPGA PCB設計指導(五)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

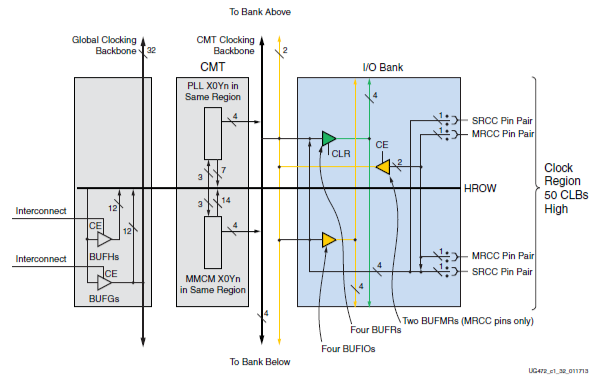

Xilinx 7系列FPGA的時鐘結構解析

Xilinx 7系列FPGA管腳是如何定義的?

Xilinx 7系列與Ultrascale系列FPGA的區別

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx 7系列FPGA PCB仿真和分析

Xilinx 7系列FPGA PCB仿真和分析

評論