本文介紹基于Mentor Graphics Catapult工具的HLS(High LevelSynthesis,高層次綜合)硬件設(shè)計。

首先將簡單介紹高層次綜合在數(shù)字芯片流程中所處的層次、其獨特優(yōu)勢等等;接著將介紹如何基于Catapult工具進行HLS設(shè)計,例如Catapult支持的數(shù)據(jù)類型、接口類型;最后將以RMD(RoughMode Decision,粗略模式估計)為例介紹如何實現(xiàn)寄存器、狀態(tài)機和RAM等硬件電路基本組件。

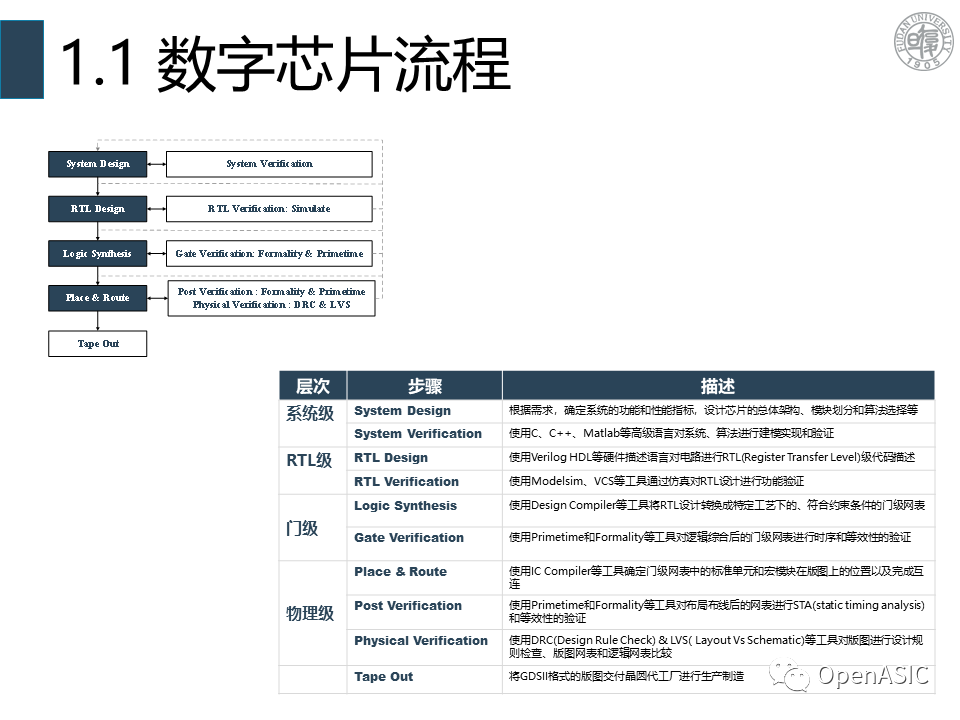

如圖表所示,數(shù)字芯片的硬件描述層級可以被粗略分為四個,從底向上依次是物理級(晶體管級)、門級、RTL(RegisterTransfer Level,寄存器傳輸級)級和系統(tǒng)級/算法級。隨著芯片復(fù)雜度(晶體管數(shù)量)的不斷提升,在較低層次上描述整個硬件設(shè)計變得難以實現(xiàn)。目前的數(shù)字芯片集中于在RTL級以Verilog/ System Verilog語言描述硬件電路,特殊情況下為了追求極致的性能可能會在門級/物理級進行電路設(shè)計。總體來說,主要依靠DC(DesignCompiler), ICC(ICCompiler)這樣的EDA(ElectronicsDesign Automation,電子設(shè)計自動化)工具來實現(xiàn)硬件描述層次的降低。隨著EDA工具的不斷發(fā)展,在系統(tǒng)級/算法級使用C/C++/SystemC等高級語言描述硬件電路逐漸被廠商采納以提升硬件開發(fā)效率。即在DC和ICC前,再使用HLS的綜合器來實現(xiàn)硬件描述層次的降低。

HLS的出現(xiàn),讓硬件描述層級再次提升,有利于降低硬件設(shè)計難度,減少硬件開發(fā)時間,讓開發(fā)人員可以更多關(guān)注系統(tǒng)級/算法級的設(shè)計。越高層次的優(yōu)化往往能帶來更多的系統(tǒng)收益。但需注意,使用C等高級語言描述硬件電路本質(zhì)仍是設(shè)計硬件,在寫相關(guān)代碼時仍需做到能估計出相關(guān)的硬件電路。在FPGA開發(fā)流程中,Vivado HLS是最常使用的HLS工具。而在ASIC開發(fā)流程中,Catapult是最常使用的。

HLS在設(shè)計和驗證方面都存在諸多優(yōu)勢:

在設(shè)計方面,直接在算法級進行電路設(shè)計,有利于進行算法/架構(gòu)探索。C/C++代碼開發(fā)后通過HLS+DC/FPGA快速得到硬件代價(面積/性能)的估計值。相同的設(shè)計源碼,通過更改循環(huán)展開/循環(huán)流水的參數(shù)能快速調(diào)整設(shè)計的吞吐率,進而在性能和面積之間輕松調(diào)整;通過調(diào)整HLS的時鐘周期約束,能快速調(diào)整設(shè)計所能達到的最高頻率。同一份代碼,能在多個平臺/場景間最大化復(fù)用。

在驗證方面,仿真C模型后能將其作為golden,和后續(xù)HLS生成的RTL代碼進行形式驗證,以及同步仿真,即RTL仿真時復(fù)用C仿真的測試用例。此外,在C模型層次仿真所需時間更少。

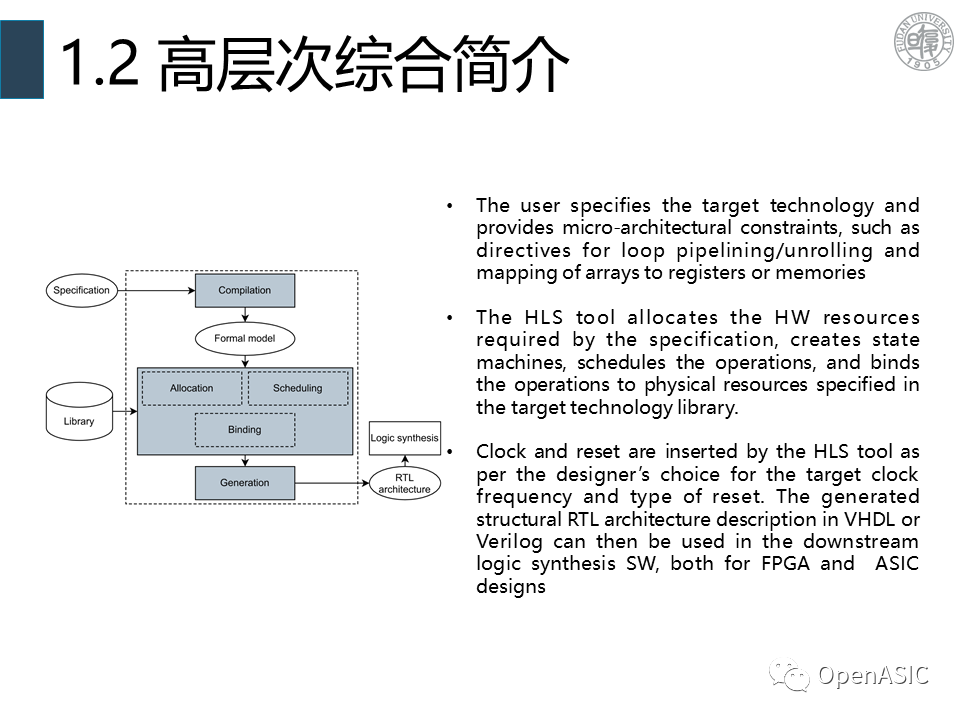

高層次綜合和DC綜合過程較為相似:用戶輸入設(shè)計源文件,設(shè)計約束和目標工藝庫等信息,HLS工具將自動分配硬件資源,根據(jù)延時信息和目標頻率將各個運算分配到各個時鐘周期里。HLS工具將自動插入時鐘和復(fù)位(同步復(fù)位/異步復(fù)位)。產(chǎn)生的RTL文件可以被用于后續(xù)的FPGA設(shè)計和ASIC設(shè)計。

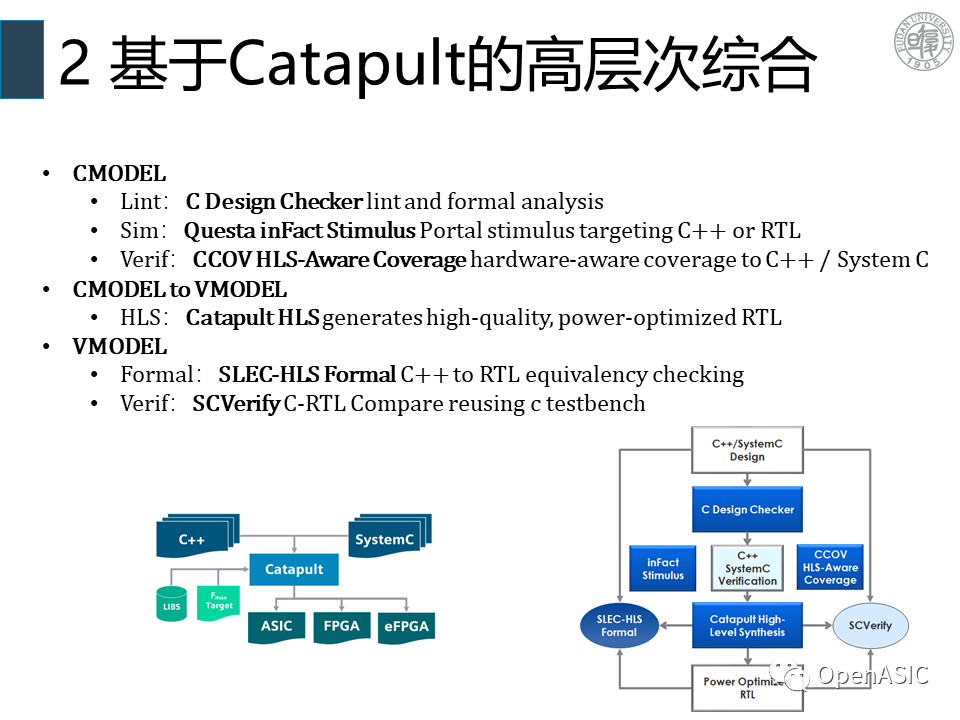

Catapult有一系列EDA工具來輔助HLS設(shè)計:

在C模型(CMODEL)層次,可以使用C Design Checker來進行語法檢查和形式驗證分析;使用inFactStimulus來仿真C++/RTL,也可指定其他外部仿真工具如VCS;使用CCOVHLS-Aware Coverage來進行覆蓋率收集。

在CMODEL到RTL模型(VMODEL)轉(zhuǎn)換中,使用Catapult High-Level Synthesis生成高質(zhì)量、功耗優(yōu)化的RTL。

在VMODL層次,使用SLEC-HLS Formal進行C++和RTL的形式驗證檢查;使用SCVerify進行C-RTL同步仿真,復(fù)用相同的C測試用例。

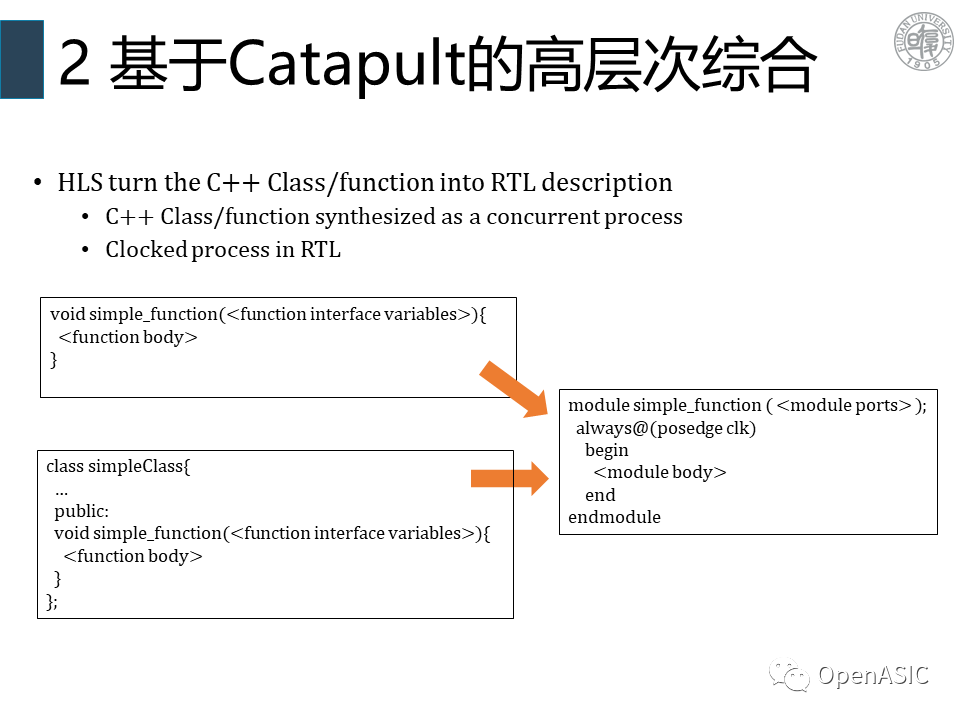

在RTL設(shè)計中,以模塊(Module)為最小單元進行硬件設(shè)計。在CatapultHLS設(shè)計中,支持以函數(shù)(function)和類(Class)作為最小單元進行設(shè)計,HLS綜合工具將為其自動插入時鐘和復(fù)位。

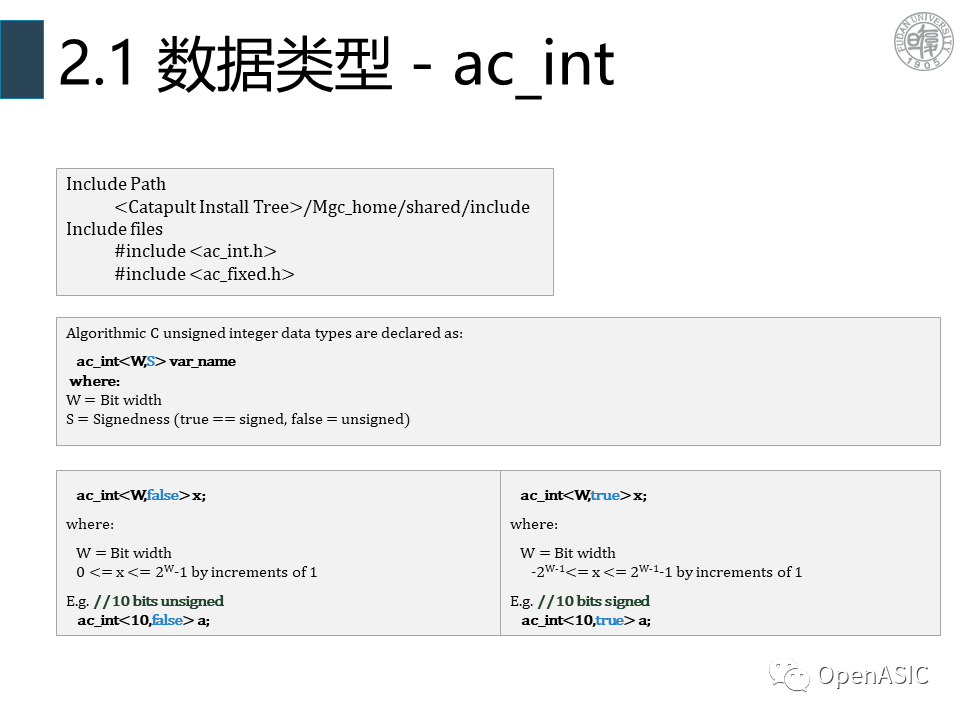

Catapult HLS支持比特精度的數(shù)據(jù)類型ac_int, 通過設(shè)計位寬W 和符號標志位 S來定義信號。此外,其還支持定點數(shù)類型ac_fixed,在ac_int的基礎(chǔ)上新增整數(shù)位寬I。

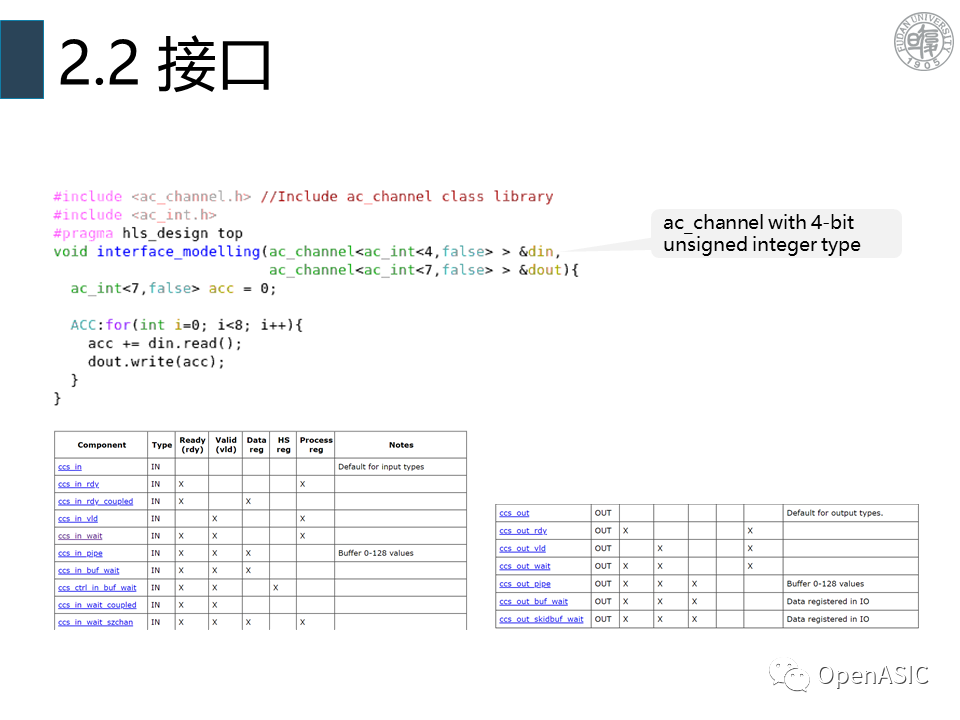

Catapult HLS使用 ac_channel 來定義輸入端口和輸出端口的數(shù)據(jù)類型。若某端口只被讀取,則將其推導(dǎo)為輸入端口;若某端口只被寫入,則將其推導(dǎo)為輸出端口;若某端口既有讀取又有寫入,則會被推導(dǎo)為雙向端口。如需進行累加,建議使用中間變量來進行累加,累加結(jié)束后再將結(jié)果寫入,從而避免輸出端口被推導(dǎo)為雙向端口。

ac_channel 支持多種接口協(xié)議,輸入輸出默認類型為ccs_in_wait和ccs_out_wait,會自動維護ready和 valid,也可將其修改為最簡潔的ccs_in/ccs_out類型。

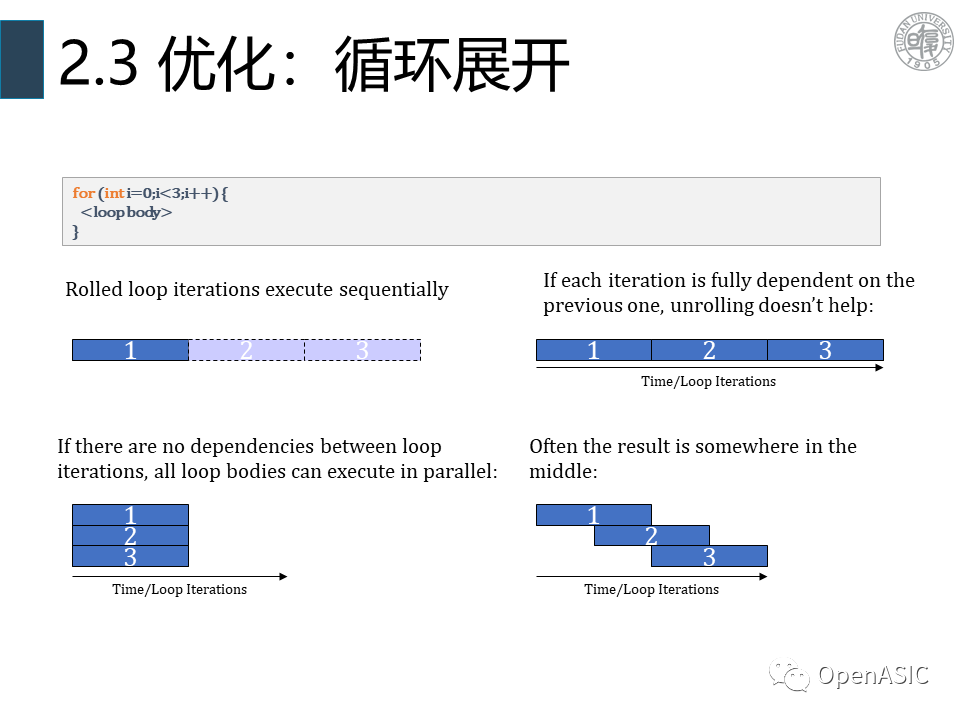

Catapult HLS支持循環(huán)展開,用面積換性能,如果迭代塊無數(shù)據(jù)依賴可以被完全展開。

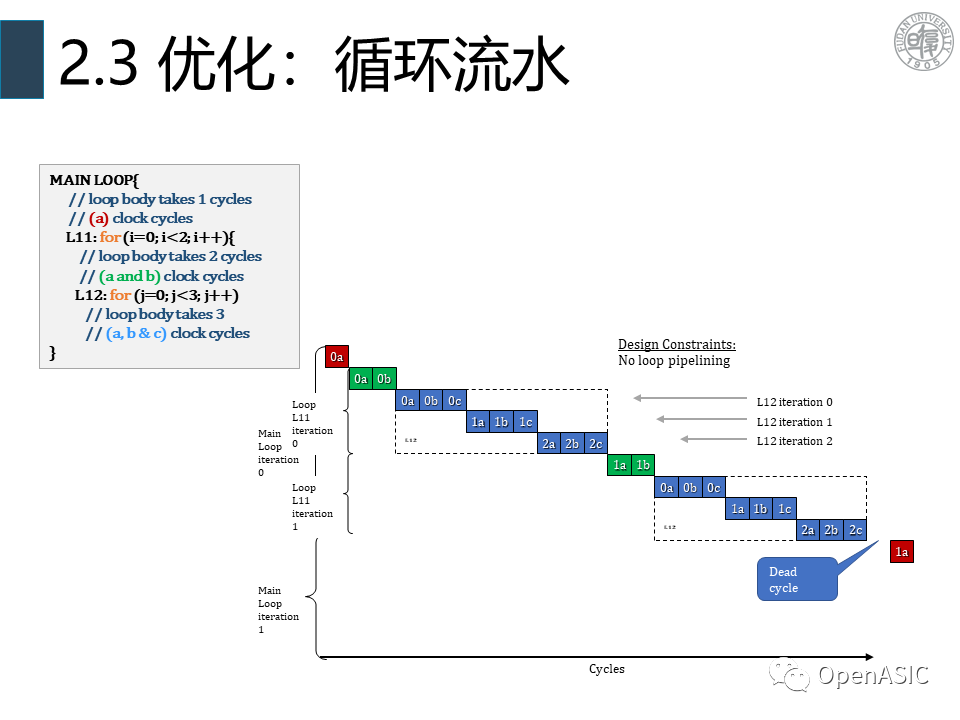

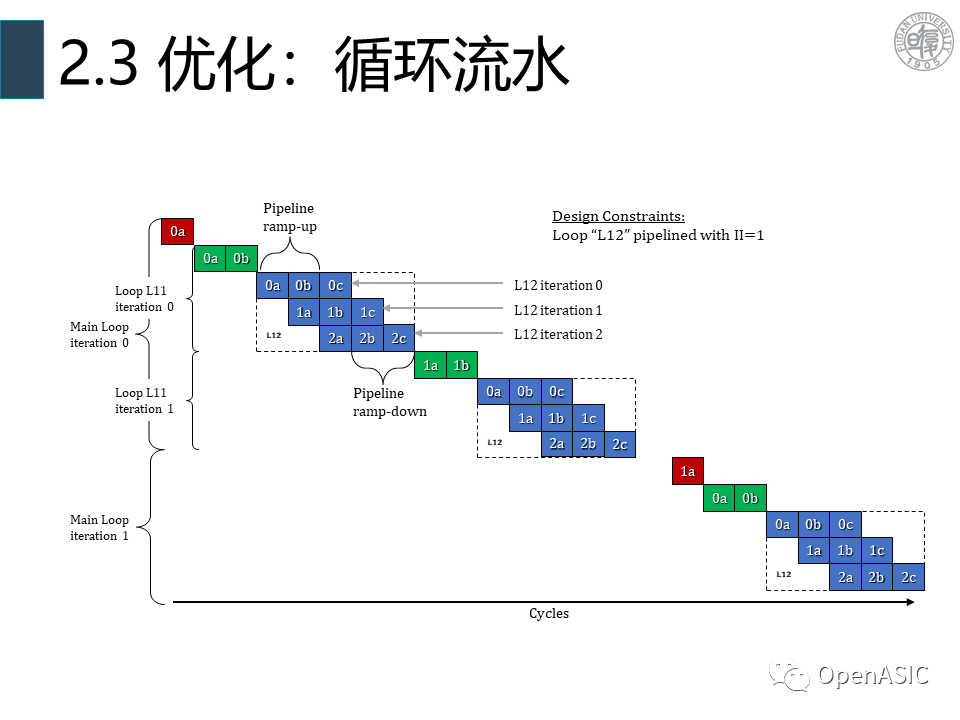

Catapult HLS支持循環(huán)流水,也是用面積換性能,提升整體的吞吐率,并降低從輸入到輸出的延時。當存在數(shù)據(jù)依賴導(dǎo)致循環(huán)展開無法使用時,可以采用循環(huán)流水的方式優(yōu)化。

對每個循環(huán)都可以指定其流水與否,II(InitInterval)確定了流水線的初始化間隔,即每隔幾個周期開啟一次新的數(shù)據(jù)迭代。

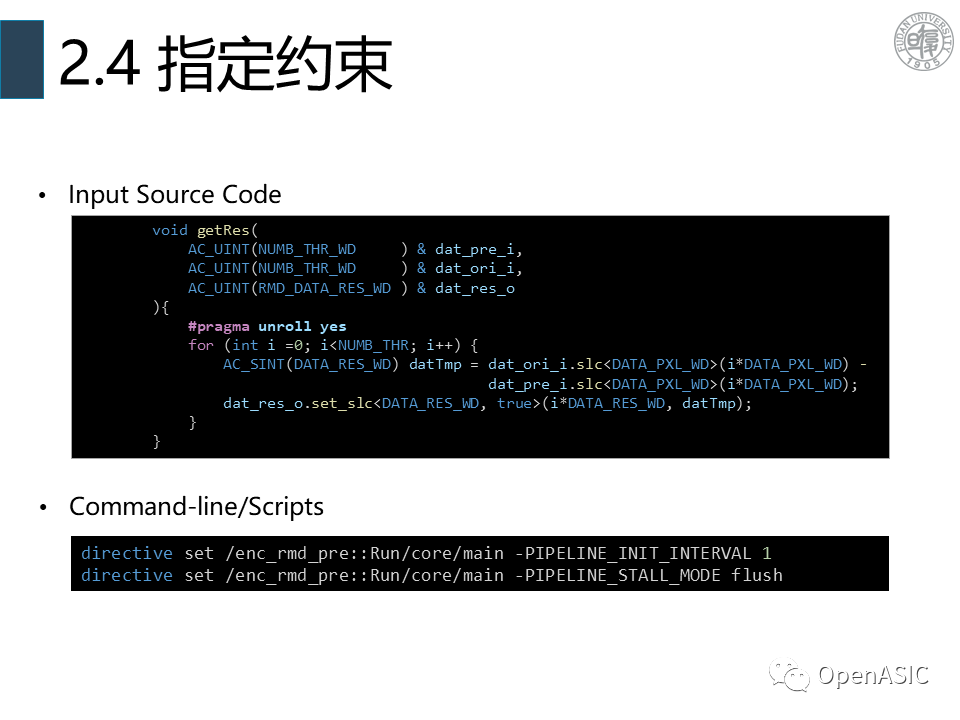

可以通過在源碼中加入諸如 #pragaunroll yes的指令來設(shè)置約束;也可以通過tcl指令在腳本中設(shè)置約束,諸如設(shè)置RMD的預(yù)測模塊(enc_rmd_pre)采用流水實現(xiàn)。

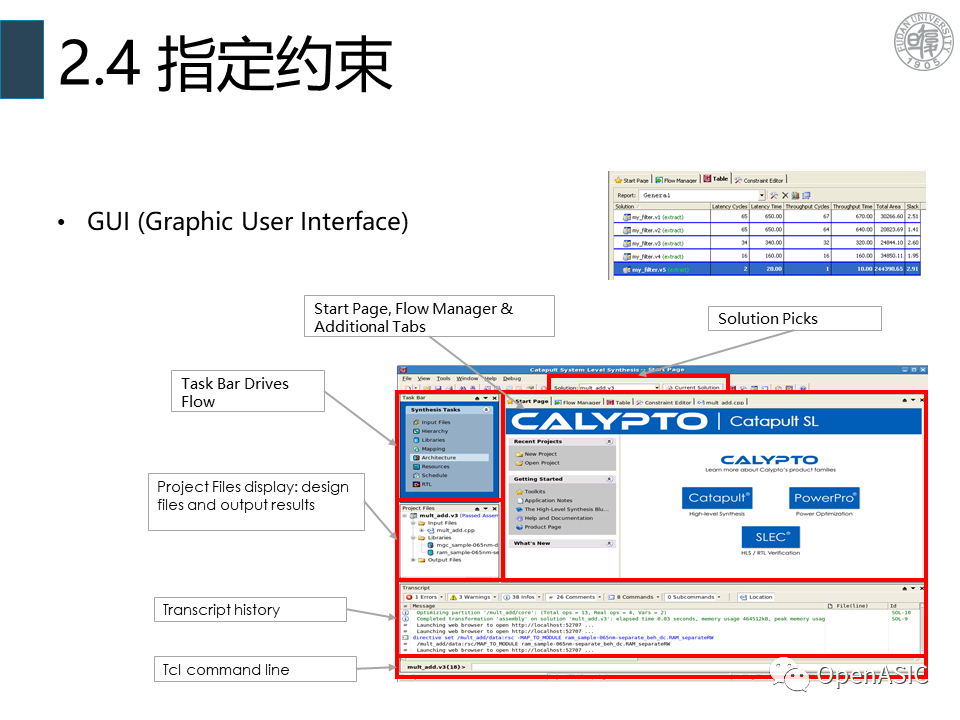

此外,還可以通過軟件的圖形界面來進行設(shè)置約束,即在各個綜合步驟(SynthesisTasks)中設(shè)置相關(guān)的約束。在圖形界面進行設(shè)置后,transcripthistory里會顯示對應(yīng)的tcl 指令,可將其搜集起來匯總到腳本中,后續(xù)復(fù)用。修改源碼/配置后可以產(chǎn)生新的Solution,工具會顯示各個Solution的延時、吞吐、綜合面積和時序裕量。

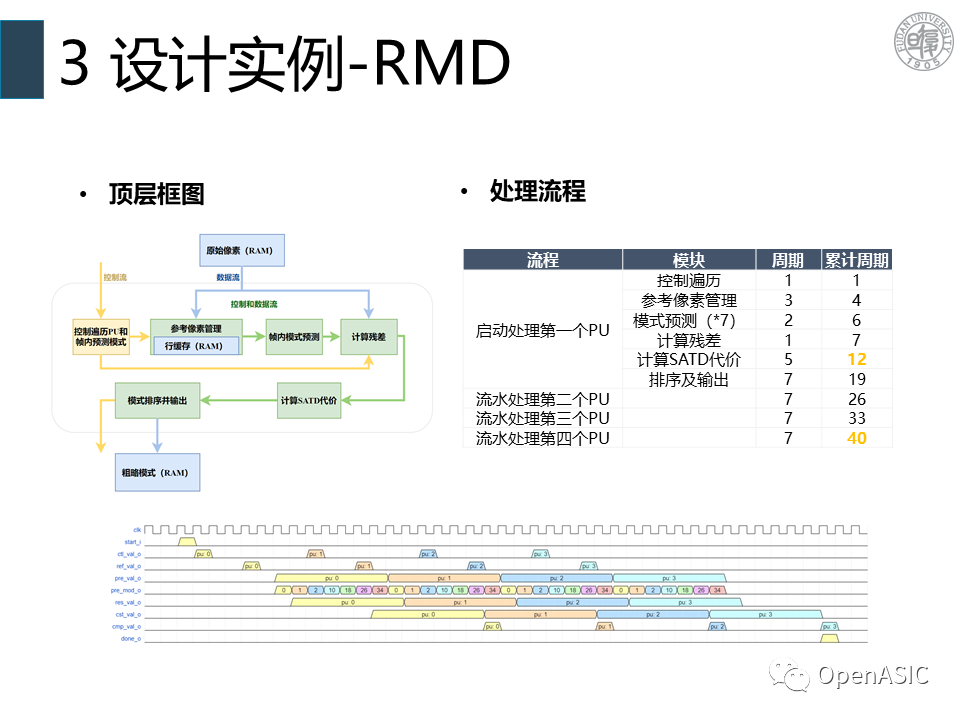

以RMD模塊為例介紹HLS設(shè)計,其包含了控制、參考像素管理、幀內(nèi)模式預(yù)測、殘差計算、SATD代價計算和模式排序與輸出等等子模塊。使用HLS實現(xiàn)各個子模塊,使用verilog進行頂層設(shè)計。RMD將流水處理4個PU,對每個PU會進行7種模式預(yù)測。流水線啟動延時為12個周期,后續(xù)4*7=28個周期逐漸出結(jié)果。

采用基于類的方式來實現(xiàn)模塊設(shè)計。定義__ENC_RMD_CTL_H__這個宏以避免多重編譯。define.h中定義了諸如塊尺寸和位寬的一些參數(shù),以及封裝了一些常用的數(shù)據(jù)類型,比如AC_UINT(x)即 ac_int

將狀態(tài)跳轉(zhuǎn)條件和輸出置于狀態(tài)變量(計數(shù)器 cnt_mod/pu,狀態(tài)機state)更新之前,即當前輸出與之前的輸入和狀態(tài)變量相關(guān),摩爾型。

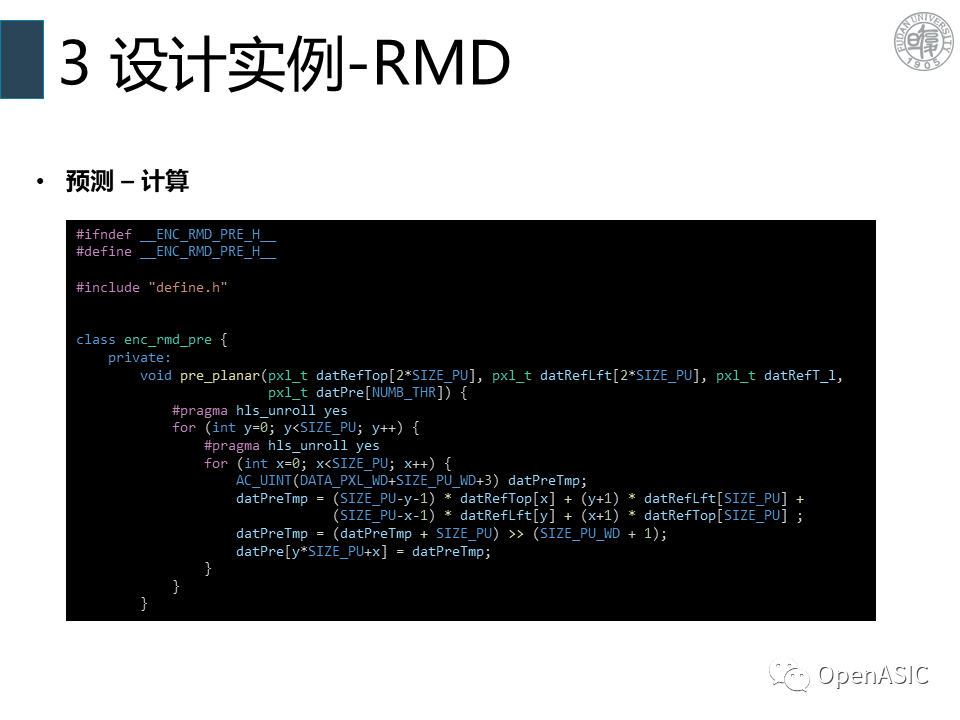

以Planar預(yù)測模式為例,其將根據(jù)上方、左方和左上方的參考像素來得到當前塊的預(yù)測值,pxl_t是封裝了ac_int<8,false>。對兩重循環(huán)使用#pragmahls_unroll yes進行循環(huán)展開。定義相應(yīng)位寬的中間變量來記錄中間結(jié)果,避免被截斷。對于這類純計算函數(shù),無需手動切流水級,工具將根據(jù)目標工藝和時鐘約束來自動調(diào)度,使得各個周期內(nèi)的運算延時較為均勻。

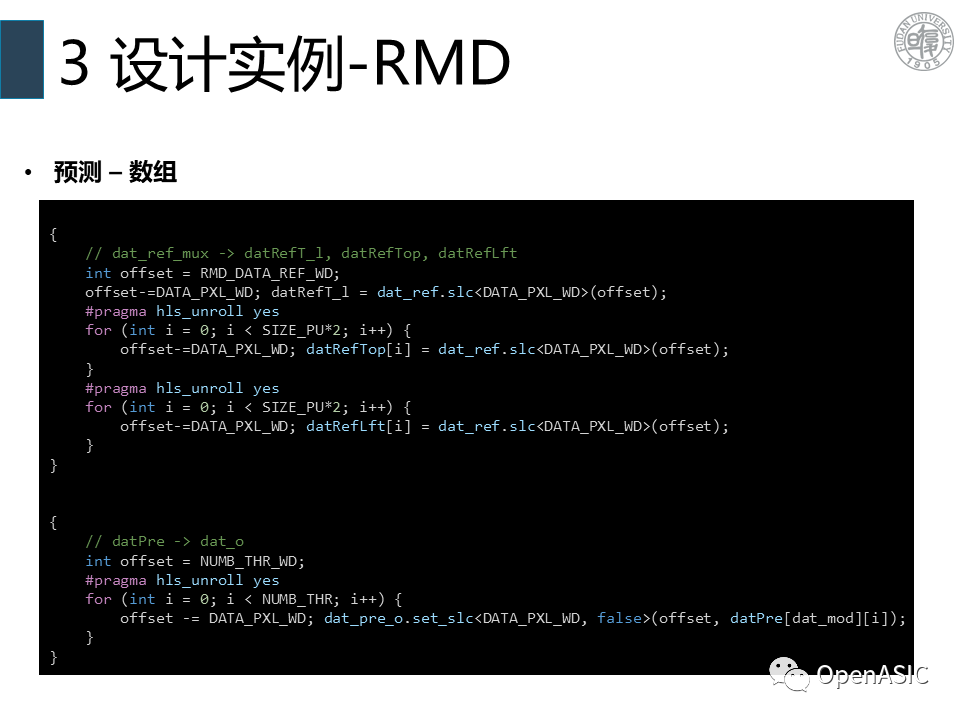

在非頂層函數(shù)的接口中可以使用數(shù)組來簡化后續(xù)索引。為此,在頂層函數(shù)的輸入和輸出處需增加平面格式與多維數(shù)組格式的數(shù)據(jù)格式轉(zhuǎn)換,可使用slc和set_slc進行切片操作。

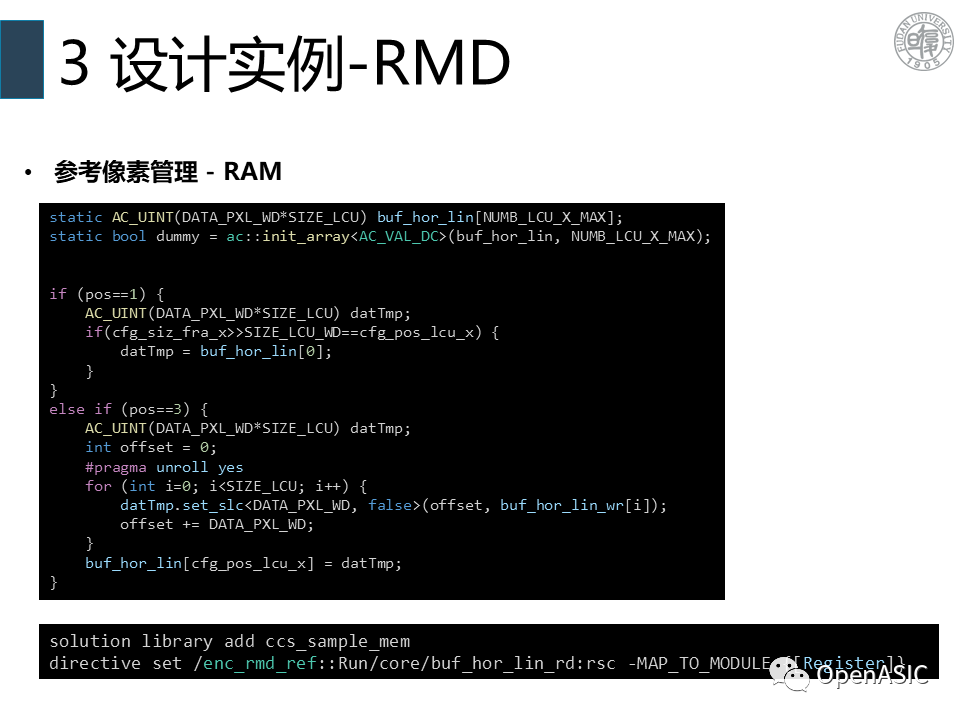

對于參考像素管理中需要使用到的行緩存,register實現(xiàn)時代價過大,傾向于使用ram實現(xiàn)。為此,1. 使用 static修飾該數(shù)組;2. 如果不需要將數(shù)組/ram初始化為0,則設(shè)置該數(shù)組的初始化類型為AC_VAL_DC,即 Don’tCare,以避免工具默認對ram進行初始化為0的操作,節(jié)省若干啟動周期。3. 在設(shè)置目標庫時增加相應(yīng)的ram庫,如ccs_sample_mem。此外,可以通過tcl指令來指定某些數(shù)組的默認類型,例如將buf_hor_lin_rd 強制設(shè)置為Register類型。

審核編輯 :李倩

-

硬件設(shè)計

+關(guān)注

關(guān)注

18文章

426瀏覽量

45065 -

數(shù)據(jù)類型

+關(guān)注

關(guān)注

0文章

237瀏覽量

13816 -

HLS

+關(guān)注

關(guān)注

1文章

131瀏覽量

24632

原文標題:基于Catapult的HLS硬件設(shè)計

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

西門子 EDA(Mentor)或停服,華大九天 Argus 助力國產(chǎn) EDA 崛起

Vivado HLS設(shè)計流程

VNF9D1M5QTR芯片用什么硬件讀寫工具?讀寫軟件怎么實現(xiàn)?

使用HLS流程設(shè)計和驗證圖像信號處理設(shè)備

為什么用TVP7002采集到的PC graphics會閃爍呀?

Altera推出一系列FPGA軟、硬件和開發(fā)工具

NFC IC配置工具NFC Cockpit的主要特性

優(yōu)化 FPGA HLS 設(shè)計

FPGA的開發(fā)工具

一種在HLS中插入HDL代碼的方式

基于Mentor Graphics Catapult工具的HLS硬件設(shè)計

基于Mentor Graphics Catapult工具的HLS硬件設(shè)計

評論