上次我們講了處理器的中斷和異常,只是從高到低俯視了這一功能。沒有落到實處,沒有具體到細節。上一章有一處有問題,在此改正一下,狹義的中斷和狹義的異常一起構成了廣義的異常而非廣義的中斷。這一次,我們就來講講RISC-V特權架構,順便把RISC-V架構中的中斷和異常探索得更加深入。

CPU可以運行在好幾種特權模式下。RISC-V中定義了三種特權模式,分別是機器模式(machinemode)、監管者模式(supervisor mode)和用戶模式(user mode)。不同的領域和不同的廠家有不同的稱呼。在操作系統中,機器模式體現為實模式,用戶模式則體現為保護模式。早期的dos系統就是運行在實模式下。

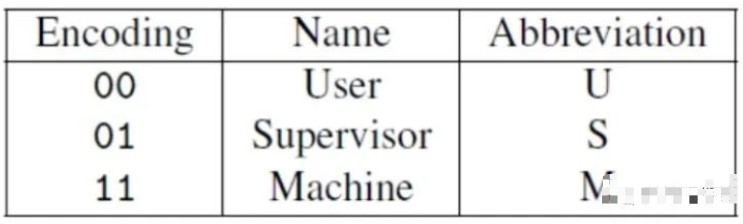

RISC-V中的三種特權模式的編碼、名稱和縮寫

為什么要劃分這么多種的模式呢?目的是為了保護電腦運行環境不被破壞。比如說一個病毒線程想要篡改其他線程中的內存數據,甚至是破壞操作系統,這種操作肯定是不被允許的。我們必須為每一個線程劃定一個空間,每個線程只能訪問屬于自己的空間。具體操作以后會講。那問題就解決了嗎?沒有。作為操作系統,得能夠有效的控制別的線程的運行情況,必要的時候將讀寫一些線程。因此操作系統必須要被賦予更高級的權限,或者說要與其他的應用線程區別對待,因此不同特權模式應運而生。

其中操作系統的線程代碼就是運行在機器模式下,應用程序運行在用戶模式下,有些時候比如windows系統里會忽然彈出一個管理員權限的許可窗口,如果你點了確定,可以理解為應用程序的權限經過你的許可提高到了監管者模式。注意:機器模式的權限是最高的,用戶模式的權限是最低的。如果用戶的權限過高,他們可能會弄壞電腦。

那么RISC-V的CPU是怎么做的呢?

首先,RISC-V架構中定義了一些控制和狀態寄存器(control and status register),簡稱CSR,與32個物理寄存器不同(物理寄存器可以認為是5位地址尋址的),這些CSR是用12位地址進行尋址的,并且地址空間是私有獨立的,不同于全局地址空間。并且,針對這些CSR寄存器的讀寫有相應的特殊指令,這些特殊指令都有被定義在之前講的RISC-V指令集圖卡中。其中某些特權指令只能在機器模式中被執行(需要等級權限),如果在用戶模式中遇到這些特權指令,處理器就會拋出異常,相應的線程可能會被殺死,或者由用戶自行決定。其次,CSR的種類有很多,舉幾個機器模式中要用到的CSR。比如mvendorid寄存器,它在12位的地址空間的地址是0xf11,它的用途是保存廠商標識代碼的,所有的電子產品生產廠商可以向美國JEDEC協會付費申請一個廠商標識代碼(也可以向我申請,我不收費,有意聯系)。再比如misa(指令集寄存器),地址是0x301,用途是指示此CPU支持哪些指令集。類似的CSR有很多,在此不一一贅述,下面重點說說八個和機器模式中斷與異常有關的CSR。

它們分別是:mepc(異常PC寄存器)、mtvec(異常向量基地址寄存器)、mcause(異常原因寄存器)、mie(中斷使能寄存器)、mip(中斷等待寄存器)、mtval(異常值寄存器)、mscratch(草稿寄存器)和mstatus(線程狀態寄存器)。其中每個寄存器命名開頭的m是機器模式的意思。相應的還有其他模式中斷與異常的CSR。

mstatus寄存器的具體字段,僅需注意紅色畫圈部分

機器模式下,異常發生時,mepc用于保存當前線程的PC值(或者異常的PC值),并將異常服務程序的入口地址從mtvec寫入PC寄存器中。倘若支持向量中斷并且是狹義中斷發生時,那么PC值設置為mtvec-1+異常序號編碼*4(之所以-1,是因為mtvec最低位是硬件是否支持向量中斷的標志位,1表示支持向量中斷,在硬件電路中我們大可以直接將最后一位抹掉實現-1),而狹義異常發生時,PC值仍設置成mtvec不變。根據異常或中斷來源,將其來源序號寫入mcause中。將mtval設置為出錯的地址或其他適用于特定異常的信息字。將mstatus中的MIE字段(注意,是MIE字段,不是mie寄存器,字段是指寄存器中的某一段數值,MIE字段屬于mstatus寄存器的一部分)寫到MPIE字段中后,再將MIE字段寫0,用以禁止接受狹義中斷,此時狹義中斷如果發生,硬件將不做響應。因此,RISC-V能且只能支持軟件中斷嵌套。狹義異常是不需要嵌套的,異常服務程序中不會再發生狹義異常,除非你異常服務程序寫得有問題。將發生中斷前的權限模式寫到mstatus中的MPP字段內。可以想象到,當中斷或異常結束后,這些保存了的東西是要復原回來的,線程方能繼續執行。

注意:以上過程均是由硬件自己完成,該過程中,沒有指令被執行。硬件準備完成后,PC跳轉到mtvec這個統一的地址入口,異常服務程序才開始處理異常。(以上過程有些繁雜,慢慢看,你會明白設計者的用意的)

異常服務程序具體怎么做呢?如果不支持向量中斷,那么異常服務程序一上來,就先查詢mcause寄存器,看看這個異常是狹義中斷還是狹義異常,具體是哪出了問題。根據不同的問題再次跳轉到不同的地址,對癥下藥解決問題。比如說打3d游戲的時候鼠標傳來了一個中斷,CPU跳轉到異常服務程序,經查詢mcause得知這是一個鼠標傳來的中斷,進而訪問鼠標的驅動程序,并將相應數值傳遞給這款3d游戲,從而3d游戲渲染新的一幀畫面,最后畫面完成旋轉。

以上便是RISC-V架構在機器模式下對異常的處理。具體細節需要參考RISC-V架構書。

審核編輯:劉清

-

中斷

+關注

關注

5文章

906瀏覽量

42854 -

狀態寄存器

+關注

關注

0文章

39瀏覽量

7317 -

RISC-V

+關注

關注

46文章

2596瀏覽量

48940

發布評論請先 登錄

RISC-V架構在機器模式下對異常的處理

RISC-V架構在機器模式下對異常的處理

評論