前段時間,Soitec宣布8英寸SiC量產,而且還投資23億建線(。點這里。),更為關鍵的是他們號稱能讓單塊SiC晶錠產量增加10倍,使SiC MOSFET芯片尺寸縮小5-15%。

很多人都很好奇Soitec的技術細節,最近,“行家說三代半”拿到了他們的技術文獻,今天就給大家分享一下。

插播:7月7日,欣銳科技、英飛凌、Wolfspeed、三菱電機、芯干線、百識電子和恒普科技等企業“大咖”,將參與“新能源趨勢下第三代半導體產業化發展論壇”,發布最新技術報告,報名點文末“閱讀原文”。

SiC功率器件已成為廣泛應用的突破性技術,風靡汽車牽引逆變器、DC/DC轉換器、車載充電器或充電站等領域。

但是目前,4H-SiC材料質量和供應限制了碳化硅在汽車等領域的爆發,因為這些領域對碳化硅襯底的質量要求非常高,而目前業界還很難提供近乎無缺陷的襯底晶圓。

Soite認為,他們通過Smart Cut技術,制造的SmartSiC襯底,具有非常高的質量,能夠優化器件良率。

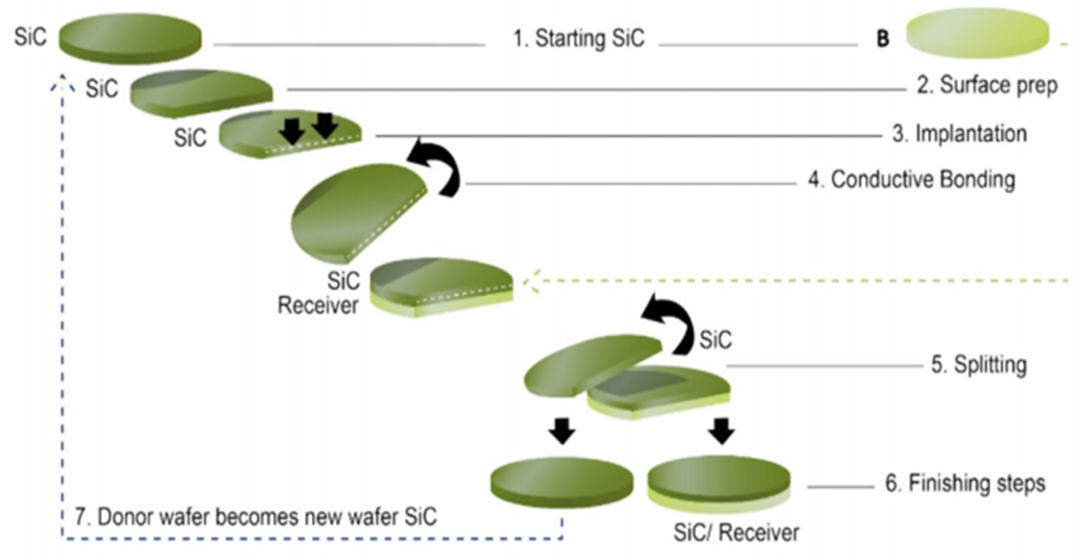

SmartSiC的制作步驟如下,這種方式的好處可以參考之前的報道:

圖1:SmartSiC 襯底制造工藝

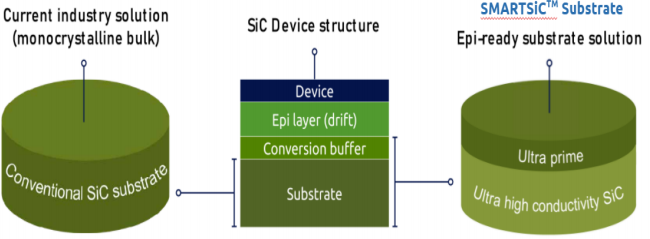

SmartSiC襯底概念圖如下:

圖2: SmartSiC襯底

目前,Soitec已經展示了SmartSiC開發樣品,并可用于器件評估。

4H-SiC 襯底(左)和 SmartSiC襯底(右)

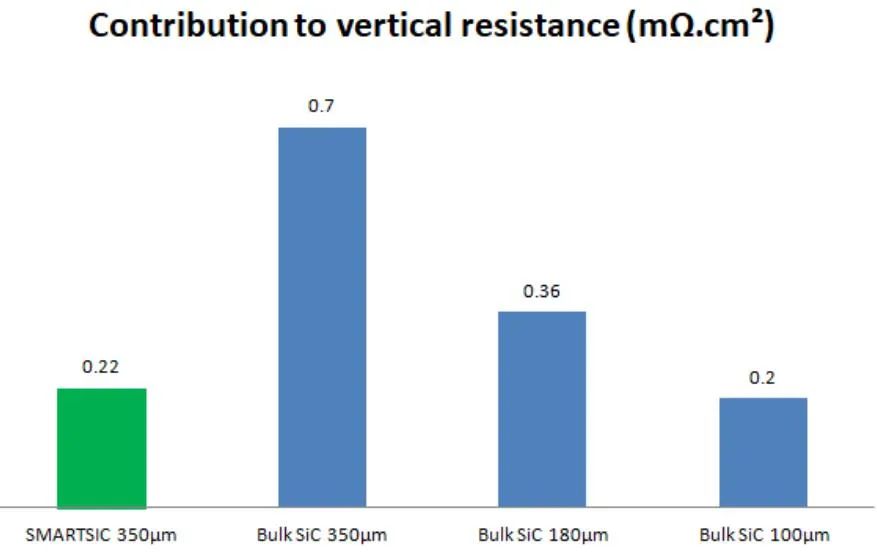

根據文獻,Soitec通過多晶SiC襯底的開發,制作了電阻率低至 5mΩ.cm或更小的碳化硅晶片。從整個堆棧來看,對應的垂直電阻為0.22mΩ.cm2(或更小)。

350μm的SmartSiC電阻率與100μm的 4H SiC相當,比常規180μm的碳化硅襯底的電阻率降低了35%。

此外,多晶SiC襯底的另一個好處是能夠提高材料的機械性能,從而使磨削下的變形可以忽略不計。與Bulk SiC 參考相比,優化的多晶SiC磨削至180μm變形得到改善。

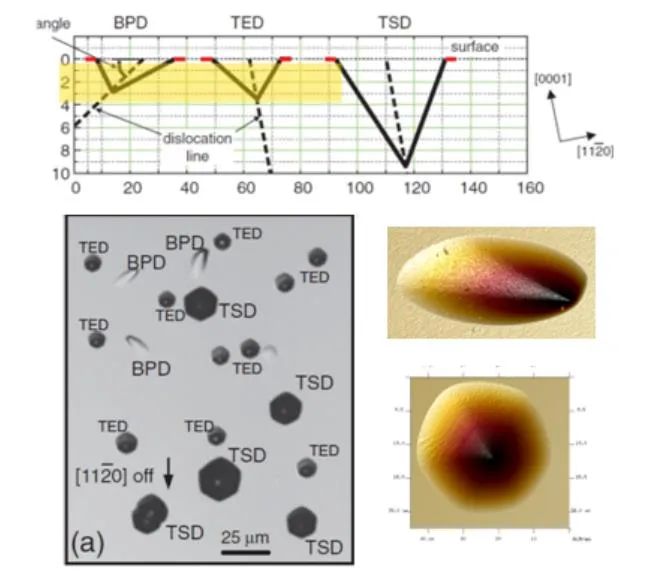

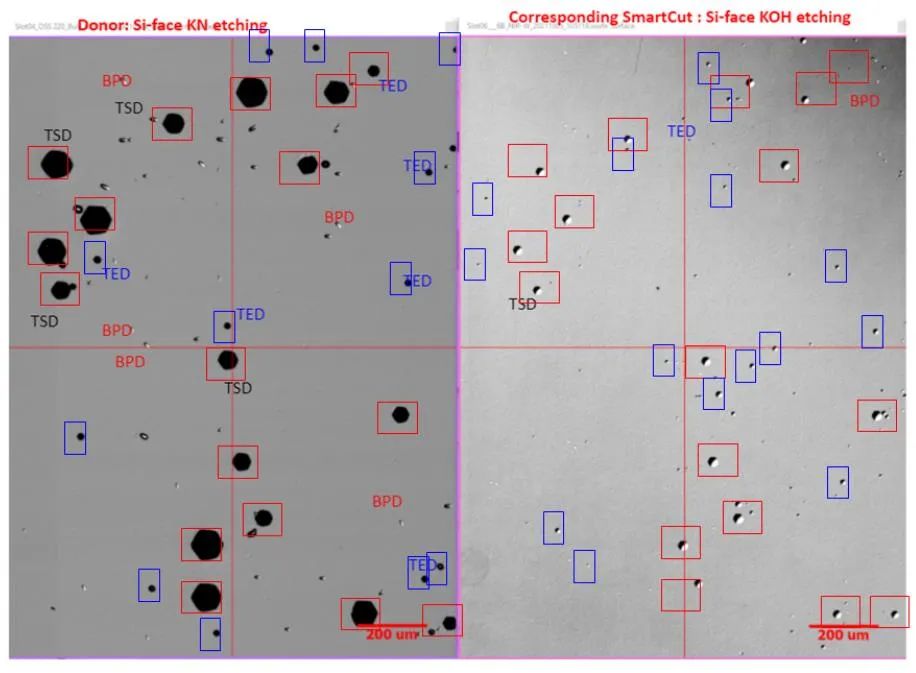

同時,Soitec還證明了SmartSiC襯底比供體晶圓更低的晶體缺陷率。

顯微鏡和 AFM 圖像顯示,SmartSiC的 TED、TSD 和 BPB都得到了明顯的優化。

通過對比可以發現,Smart Cut 不會引入新的晶體缺陷。

為此,該公司認為,他們的SmartSiC在功率器件應用方面具有巨大潛力,不僅可以提高性能,而且可以提高可制造性。

原文標題:電阻率降低35%!Soitec公布碳化硅技術細節

文章出處:【微信公眾號:第三代半導體風向】歡迎添加關注!文章轉載請注明出處。

-

功率器件

+關注

關注

42文章

1906瀏覽量

92136 -

SiC

+關注

關注

31文章

3152瀏覽量

64433 -

MOSFET芯片

+關注

關注

1文章

7瀏覽量

9191

原文標題:電阻率降低35%!Soitec公布碳化硅技術細節

文章出處:【微信號:SiC_GaN,微信公眾號:行家說三代半】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RAC400控制器通過ModbusRTU轉profibusDP網關接入到300plc

Profibus DP轉ModbusTCP網關通訊技巧!

索尼IP編碼板:技術細節與應用探索

N1X 英偉達Arm AI PC 芯片技術細節,性能表現

SONY編碼板測試:技術細節與性能評估

臺積電2納米制程技術細節公布

有關UV固化你不知道的技術細節

機房精密空調外機的技術細節!

頻譜儀怎么測量相位噪聲

PCB電路板設計與制作的步驟和要點

探究雙路或四路可選可編程晶體振蕩器SG-8503CA/SG-8504CA的技術細節及其應用

圖像邊緣檢測系統的設計流程

直通網線的作用及制作步驟

LED顯示屏的換幀頻率與刷新頻率:技術細節與市場發展

SmartSiC的制作步驟及技術細節

SmartSiC的制作步驟及技術細節

評論