核芯互聯(lián)發(fā)布首顆支持PCIE 5.0的時鐘發(fā)生器CLG52147系列芯片,PCIe Gen 5 Jitter<15fs。

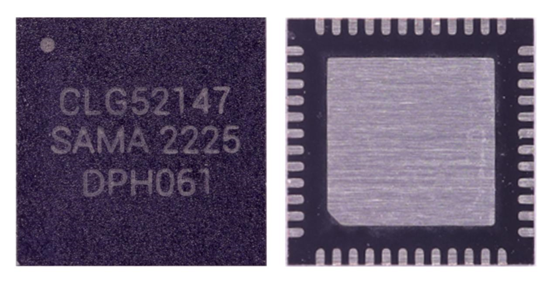

CLG52147 QFN-48封裝

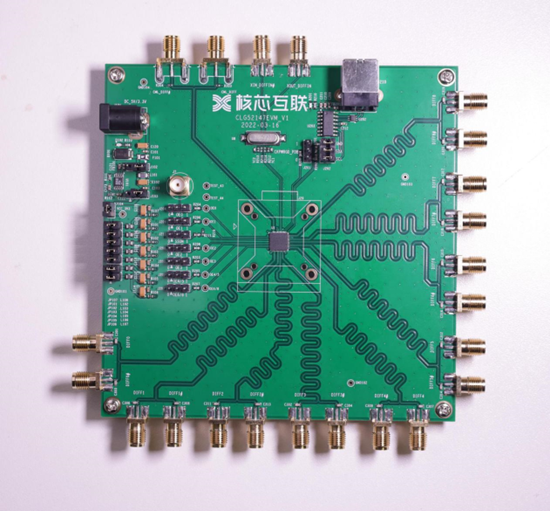

業(yè)界領(lǐng)先的時鐘IC供應(yīng)商核芯互聯(lián)發(fā)布了滿足新一代PCI Express(PCIe)5.0規(guī)范的時鐘發(fā)生器芯片CLG52147,配合之前發(fā)布的時鐘Buffer CLB53156系列,可以為用戶提供完整PCIE時鐘解決方案組合。

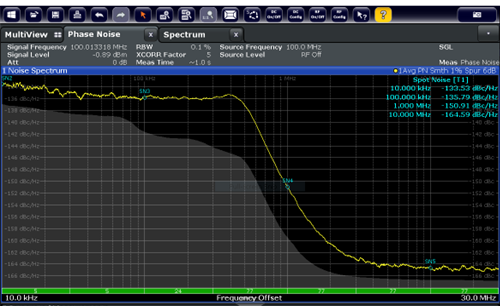

核芯互聯(lián)的CLG52147系列和CLB53156系列可以提供同類型產(chǎn)品領(lǐng)先的抖動性能,具有顯著的設(shè)計余量,具有出色的頻率靈活性和可配置的交流電參數(shù)對信號完整性進行優(yōu)化,可以工作在全工業(yè)溫度范圍內(nèi),滿足PCI Express (PCIe) Gen 1/2/3/4/5 的時鐘抖動要求,支持SSC(展頻),使用推拉式 HCSL 輸出端能夠確保最低的功耗,同時接受電路板空間和外部終端電阻,從而提高 BOM 整合。

基礎(chǔ)概念

Jitter,時鐘抖動,是對于同一時鐘而言的, 是時鐘源引起的,用來描述被測時鐘與理想時鐘在時域的偏差(單位為 ps RMS,皮秒均方根)。時鐘抖動越小越好。

Skew,時鐘偏斜,是對于多個時鐘線而言的,是時鐘樹不平衡引起的。時鐘偏斜越小越好。

頻率穩(wěn)定性,用來描述被測時鐘頻率與理想時鐘頻率的偏差(單位 ppm,百萬分之一)。頻率越穩(wěn)定(ppm越小)越好。

PCIe Serdes 在時鐘驅(qū)動下收發(fā)串行數(shù)據(jù)流。Serdes 所用時鐘由 PHY 內(nèi)的 PLL 生成,PLL 的參考時鐘由外部提供或從接收數(shù)據(jù)流中恢復(fù)出來。 PCIe 協(xié)議指定標(biāo)準(zhǔn)的參考時鐘為 HCSL 電平的 100 MHz 時鐘,Gen1~Gen4 下要求收發(fā)端參考時鐘精度在 ±300 ppm 以內(nèi),Gen5 要求頻率穩(wěn)定性 ±100 ppm。一顆性能優(yōu)秀的參考時鐘是整個PCIe系統(tǒng)成功的基礎(chǔ)。

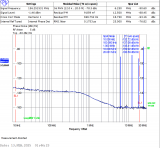

CLG52147核心指標(biāo)

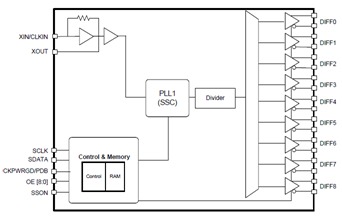

CLG52147是一顆高性能的PCIe參考時鐘發(fā)生器,使用25MHz晶振或時鐘輸入,采用3.3V供電,符合PCIe Gen1/2/3/4/5規(guī)范,支持SRNS和Common Clock架構(gòu),支持SSC以降低EMI。CLG52147具有業(yè)界領(lǐng)先的抖動指標(biāo),PCIe Gen 5 Jitter < 15fs。CLG52147有9個獨立的控制引腳用來開啟或關(guān)斷輸出以降低功耗。

CLG52147采用QFN48封裝,可以輸出9路時鐘。

CL52147已經(jīng)開放樣品申請,請聯(lián)系對口銷售或核芯互聯(lián)授權(quán)代理。

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

435895 -

時鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

223瀏覽量

68846 -

PCIe

+關(guān)注

關(guān)注

16文章

1322瀏覽量

84647

原文標(biāo)題:國內(nèi)首顆支持PCIE 5.0的時鐘發(fā)生器

文章出處:【微信號:gh_0dbe96735e9d,微信公眾號:核芯互聯(lián)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

面向5G和GNSS的微型MEMS移動時鐘發(fā)生器

核芯互聯(lián)推出高性能任意時鐘發(fā)生器CLG5908M

時鐘發(fā)生器的特點和應(yīng)用

面向Switchtec和數(shù)據(jù)中心應(yīng)用的預(yù)配置時鐘發(fā)生器器件編號

PLL1707-Q1多時鐘發(fā)生器數(shù)據(jù)表

CDCEx937低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCE(L)913低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCS501 SSC時鐘發(fā)生器/緩沖器數(shù)據(jù)表

CDCI6214超低功耗時鐘發(fā)生器(具有PCIe支持、四路可編程輸出和EEPROM)數(shù)據(jù)表

CDCE62005高性能時鐘發(fā)生器和分配器數(shù)據(jù)表

CDCE62002高性能時鐘發(fā)生器數(shù)據(jù)表

LMK05318B超低抖動時鐘發(fā)生器數(shù)據(jù)表

LMK03318超低噪聲抖動時鐘發(fā)生器系列數(shù)據(jù)表

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

首顆支持PCIE 5.0的時鐘發(fā)生器CLG52147系列芯片

首顆支持PCIE 5.0的時鐘發(fā)生器CLG52147系列芯片

評論