針對(duì)SpinalHDL中的兩大類型Reg、Wire,來(lái)梳理下在SpinalHDL中的對(duì)應(yīng)關(guān)系及聲明形式。

Wire

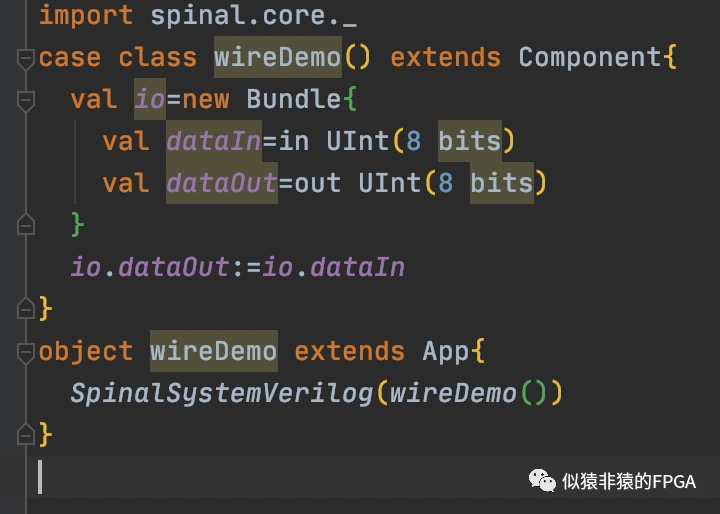

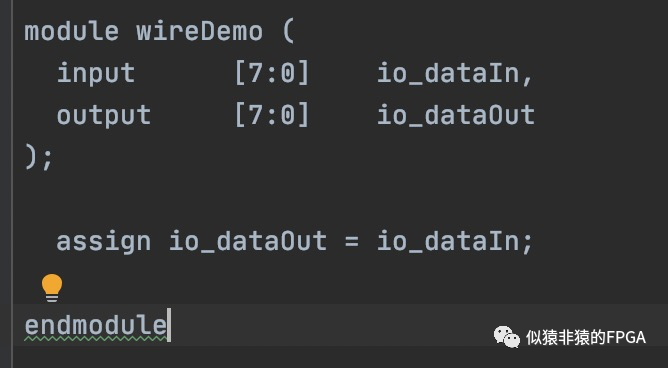

在編寫(xiě)Verilog時(shí),reg、wire是我們經(jīng)常用到的變量聲明類型。wire類型變量常用于描述組合邏輯。而Reg則用于描述時(shí)序邏輯。在SpinalHDL中,其定義了Bool、Bits、UInt、SInt、Vec等數(shù)據(jù)類型。當(dāng)我們聲明一個(gè)數(shù)據(jù)類型變量時(shí)其默認(rèn)均為線網(wǎng)類型:

在上面的代碼中,我們聲明了端口dataIn、dataOut、其默認(rèn)均對(duì)應(yīng)著RTL中的Wire類型:

Reg

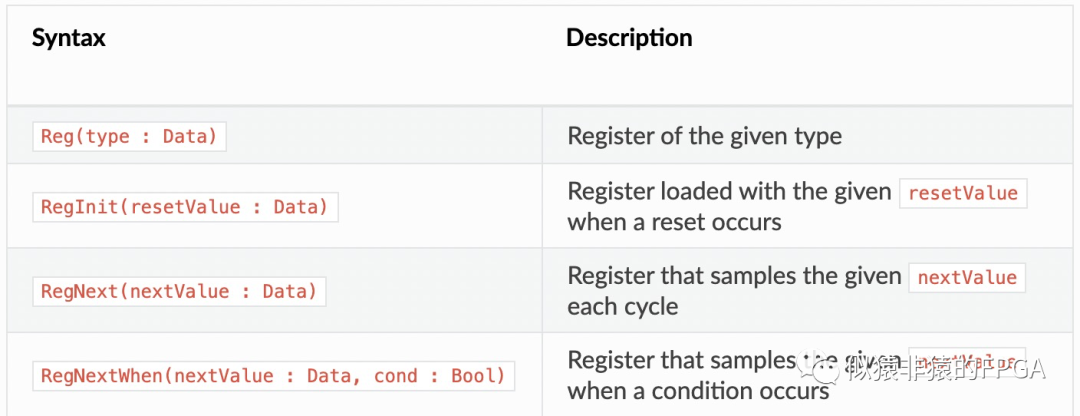

Reg類型變量常用于時(shí)序邏輯,在SpinalHDL中,將數(shù)據(jù)類型聲明為Reg類型的方式有:

SpinalHDL提供了四種類型聲明寄存器的方式,根據(jù)不同的場(chǎng)景需求,我們可以四選一選擇最合適的(都是基于Reg一步步封裝的)。 除此之外,由于SpinalHDL中默認(rèn)為Wire類型,而SpinalHDL為其都提供了setAsReg()方法來(lái)標(biāo)注為寄存器類型,同時(shí)提供Init(resetValue)方法來(lái)做初始化。因此想上面的那個(gè)例子我們想寄存器打一拍我們可以這么來(lái)寫(xiě):

case class regDemo() extends Component{ val io=new Bundle{ val dataIn=in UInt(8 bits) val dataOut=out UInt(8 bits) } val regTemp=Reg(UInt(8 bits)) init(0) regTemp:=io.dataIn io.dataOut:=regTemp}也可以這么來(lái)寫(xiě):

case class regDemo() extends Component{ val io=new Bundle{ val dataIn=in UInt(8 bits) val dataOut=out UInt(8 bits) } val regTemp=RegInit(U(0,8 bits)) regTemp:=io.dataIn io.dataOut:=regTemp}

還可以這么寫(xiě):

case class regDemo() extends Component{ val io=new Bundle{ val dataIn=in UInt(8 bits) val dataOut=out UInt(8 bits) } io.dataOut:=RegNext(io.dataIn).init(0)}

甚至可以這么寫(xiě):

case class regDemo() extends Component{ val io=new Bundle{ val dataIn=in UInt(8 bits) val dataOut=out UInt(8 bits) setAsReg() init(0) } io.dataOut:=io.dataIn}

時(shí)序調(diào)整很容易

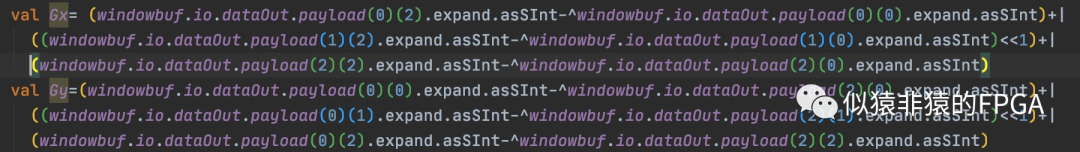

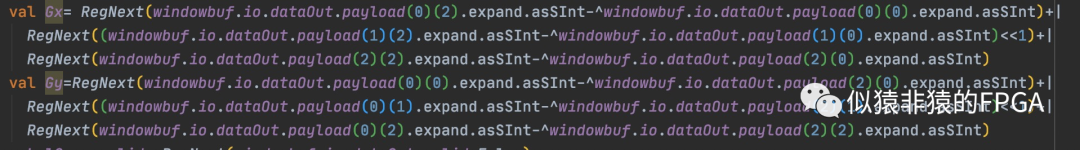

在我們編寫(xiě)RTL代碼時(shí),當(dāng)時(shí)序存在問(wèn)題時(shí)需要我們調(diào)整時(shí)序時(shí)是很痛苦的,因?yàn)闊o(wú)論是Verilog還是SystemVerilog代碼,在較長(zhǎng)組合邏輯之間添加一級(jí)寄存器往往需要改動(dòng)較多的點(diǎn),還需要仔細(xì)的評(píng)估。稍不注意就是時(shí)序沒(méi)調(diào)整好,功能先出問(wèn)題了(主要在于代碼太長(zhǎng),更改需慎之又慎)。 而在SpinalHDL里,時(shí)序調(diào)整可以做到簡(jiǎn)潔而優(yōu)雅。 在我們之前用SpinalHDL做Sobel圖像處理算法時(shí)有這么一段代碼:

在卷積核計(jì)算處理時(shí)這里存在較多的組合邏輯延遲,會(huì)成為系統(tǒng)時(shí)序瓶頸點(diǎn)。當(dāng)我們想向更高的頻率去跑時(shí)這里便需要插入寄存器。想想看這里如果是用Verilog來(lái)寫(xiě)時(shí)我們插入寄存器不僅要計(jì)算清楚中間寄存器的位寬,同時(shí)也需要改多行代碼,還要小心翼翼的改寫(xiě)。 而在SpinalHDL里,我們這里插入寄存器調(diào)整時(shí)序很容易!我們可以通過(guò)調(diào)用regNext很容易地插入一級(jí)寄存器:

如此我們便可以輕松地優(yōu)化時(shí)序,誰(shuí)還說(shuō)時(shí)序調(diào)整是個(gè)體力活兒呢??? 而針對(duì)帶握手信號(hào)的時(shí)序打拍優(yōu)化,SpinalHDL也有相關(guān)的Lib供調(diào)用可以快捷地優(yōu)化處理。

原文標(biāo)題:SpinalHDL—Reg&Wire

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

寄存器

+關(guān)注

關(guān)注

31文章

5412瀏覽量

123144 -

Reg

+關(guān)注

關(guān)注

0文章

20瀏覽量

11620 -

代碼

+關(guān)注

關(guān)注

30文章

4886瀏覽量

70194 -

時(shí)序邏輯

+關(guān)注

關(guān)注

0文章

39瀏覽量

9329

原文標(biāo)題:SpinalHDL—Reg&Wire

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

在SpinalHDL中如何快速地實(shí)現(xiàn)總線連接

spinalhdl轉(zhuǎn)Verilog可讀性 SpinalHDL開(kāi)發(fā)流程

在SpinalHDL中的對(duì)應(yīng)關(guān)系及聲明形式

在SpinalHDL中的對(duì)應(yīng)關(guān)系及聲明形式

評(píng)論