摘要

跨晶圓柵極臨界尺寸(CD)的一致性會(huì)影響芯片與芯片之間在速度和功耗方面的性能差異。隨著線寬減小到90 nm及以下,跨晶片CD均勻性的性能規(guī)格變得越來(lái)越嚴(yán)格。本文介紹了我們?nèi)A林科納提出了一種新的方法,通過(guò)光刻和刻蝕工藝順序來(lái)提高跨晶片柵極CD的均勻性。我們?nèi)A林科納所提出的方法是通過(guò)優(yōu)化整個(gè)晶片曝光后烘烤(PEB)溫度曲線來(lái)補(bǔ)償光刻工藝順序中的上游和下游系統(tǒng)CD變化成分。更準(zhǔn)確地說(shuō),我們首先構(gòu)建了一個(gè)溫度-偏移模型,該模型將PEB溫度分布與多區(qū)PEB板塊的設(shè)定點(diǎn)偏移相關(guān)聯(lián)。然后從CD掃描電子顯微鏡測(cè)量中識(shí)別將跨晶片CD與PEB板的設(shè)定點(diǎn)偏移相關(guān)聯(lián)的第二模型。然后基于CD-偏移模型和溫度-偏移模型提出了顯影后和蝕刻后CD均勻性增強(qiáng)方法。溫度-偏移模型被確定為更適合用于CD均勻性控制,因?yàn)榕cCD-偏移模型相比,它具有更好的保真度和便攜性。我們證明,在驗(yàn)證實(shí)驗(yàn)中,蝕刻后CD變化的標(biāo)準(zhǔn)偏差減少了約1nm,這驗(yàn)證了所提出的CD均勻性控制方法的有效性。

索引術(shù)語(yǔ)—約束二次規(guī)劃、臨界尺寸(CD)、臨界尺寸均勻性(CDU)、多目標(biāo)優(yōu)化、多區(qū)域PEB烘烤板、等離子體蝕刻偏差信號(hào)、曝光后烘烤(PEB)、過(guò)程控制、過(guò)程建模。

介紹

如今,批次間和晶圓間的臨界尺寸變化一般通過(guò)先進(jìn)工藝控制(APC)來(lái)解決。已經(jīng)對(duì)控制晶片老化CD進(jìn)行了廣泛的研究,其方案從前饋到前饋/反饋閉環(huán)控制[3]–[ 7]。在這些論文中,CD數(shù)據(jù)被用于校正來(lái)自光刻蝕刻順序的擾動(dòng),以便將晶片平均CD調(diào)節(jié)到目標(biāo),并最小化晶片間和批次間的CD變化。整個(gè)晶片的CD可變性變得越來(lái)越重要,這要求工藝控制超越批次與批次和晶片與晶片的水平,達(dá)到整個(gè)晶片的水平,以減少可變性。不幸的是,在現(xiàn)有文獻(xiàn)中還沒(méi)有對(duì)跨晶片CD變化的控制進(jìn)行深入研究。有效控制跨晶片CD變化將導(dǎo)致更緊密的芯片速度和功耗分布。這進(jìn)而導(dǎo)致更一致的芯片性能和更高的產(chǎn)量。

在整個(gè)光刻和蝕刻過(guò)程中,各種來(lái)源導(dǎo)致CD變化。這些可以如表1所示進(jìn)行分類(lèi)。減少跨晶片CD變化的最簡(jiǎn)單和最直接的方法是使每個(gè)處理步驟在空間上均勻。一些研究人員已經(jīng)研究了提高單個(gè)處理步驟的均勻性。Ho等人提出了一種級(jí)聯(lián)控制結(jié)構(gòu)[8],通過(guò)控制多區(qū)烘烤板的溫度分布,將涂覆的抗蝕劑膜厚度不均勻性降低到小于1 nm。向min-展示了坂本的一種新的開(kāi)發(fā)應(yīng)用技術(shù)

盡量減少顯影不均勻性,導(dǎo)致晶片CD偏差為6nm(3 sigma)[9]。

然而,對(duì)于300毫米晶片加工來(lái)說(shuō),使每個(gè)加工步驟在空間上均勻變得過(guò)于昂貴。此外,并不是通過(guò)光刻蝕刻順序的每個(gè)處理步驟都提供空間控制權(quán)限。我們注意到,在典型的蝕刻工藝中,空間可控性受到嚴(yán)重限制。唯一潛在可用的控制機(jī)制是雙區(qū)ESC冷卻系統(tǒng)中背面氦氣壓力的調(diào)節(jié)。然而,這種雙氦區(qū)系統(tǒng)在蝕刻機(jī)中并不普遍。此外,由于其僅有的雙區(qū)配置,背面氦氣壓力調(diào)節(jié)在蝕刻過(guò)程中提供非常有限的控制權(quán)限。光刻步驟提供了更多的空間控制機(jī)會(huì)。這包括逐個(gè)芯片的曝光劑量調(diào)整

[10]通過(guò)調(diào)整加熱器區(qū)域控制器的偏移和PID設(shè)置[12],在曝光后烘焙(PEB)步驟中調(diào)整空間溫度曲線。這兩個(gè)控制輸入通常很容易接近。我們論文的中心思想是使用這些控制機(jī)制,通過(guò)補(bǔ)償其他系統(tǒng)的跨晶片CD變化源,如上游顯影不均勻性和下游等離子體蝕刻偏置信號(hào),來(lái)改善蝕刻后跨晶片CD均勻性。在這篇論文中,我們把我們的控制行為限制在PEB步驟。曝光設(shè)置的探索是一個(gè)有待在未來(lái)研究中分析的課題。

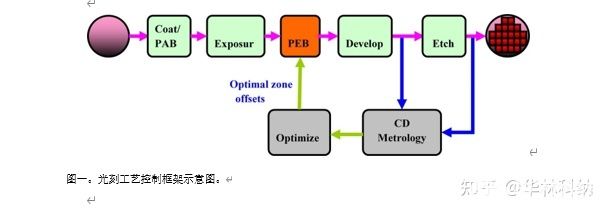

為了說(shuō)明我們的方法,考慮圖1所示的典型光刻工藝控制框架。因?yàn)榫植縋EB溫度可以直接控制局部CD,所以如果通過(guò)適當(dāng)調(diào)整PEB溫度空間分布可以平衡整個(gè)晶片CD變化源,則可以最小化整個(gè)晶片的顯影后/蝕刻后CD變化1。

通過(guò)將PEB溫度與多區(qū)域烘烤板區(qū)域控制器偏移相關(guān)聯(lián)的溫度-偏移模型或者將CD與多區(qū)域烘烤板區(qū)域控制器偏移相關(guān)聯(lián)的CD-偏移模型,可以獲得對(duì)應(yīng)于最小化CD擴(kuò)散的期望PEB溫度分布的最佳加熱器區(qū)域控制器偏移。這些模型是通過(guò)一組設(shè)計(jì)好的實(shí)驗(yàn)從實(shí)驗(yàn)中提取出來(lái)的。還通過(guò)平行設(shè)計(jì)的實(shí)驗(yàn)提取了KrF和ArF抗蝕劑的局部光致抗蝕劑PEB熱敏性。

如圖2所示,在裸硅襯底上涂覆2950 KrF DUV抗蝕劑。光刻工具是一個(gè)248納米波長(zhǎng)掃描儀,以及一個(gè)現(xiàn)代跟蹤功能的多區(qū)PEB烘烤板模塊。使用最先進(jìn)的CD掃描電子顯微鏡(SEM)來(lái)測(cè)量橫跨每個(gè)晶片的45個(gè)管芯處的線間距光柵上的抗蝕劑CD。

本文的其余部分組織如下。第二節(jié)介紹了多區(qū)烘烤板和從實(shí)驗(yàn)設(shè)計(jì)(DOE)中提取的經(jīng)驗(yàn)溫度偏移模型和臨界尺寸偏移模型。第三節(jié)介紹了顯影后[即顯影檢查或(DI)] CD均勻性控制方法以及蝕刻后[即最終檢查或(FI)] CD均勻性控制方法。獲取基線光刻-蝕刻工藝特征的表征實(shí)驗(yàn)和蝕刻后CD均勻性控制的驗(yàn)證實(shí)驗(yàn)在第四節(jié)中描述。最后,第五部分給出了結(jié)論和討論。

審核編輯:符乾江

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28563瀏覽量

232303 -

蝕刻

+關(guān)注

關(guān)注

10文章

424瀏覽量

15934

發(fā)布評(píng)論請(qǐng)先 登錄

MICRO OLED 金屬陽(yáng)極像素制作工藝對(duì)晶圓 TTV 厚度的影響機(jī)制及測(cè)量?jī)?yōu)化

wafer晶圓厚度(THK)翹曲度(Warp)彎曲度(Bow)等數(shù)據(jù)測(cè)量的設(shè)備

提供半導(dǎo)體工藝可靠性測(cè)試-WLR晶圓可靠性測(cè)試

晶圓高溫清洗蝕刻工藝介紹

【「芯片通識(shí)課:一本書(shū)讀懂芯片技術(shù)」閱讀體驗(yàn)】了解芯片怎樣制造

光刻工藝的主要流程和關(guān)鍵指標(biāo)

晶圓表面光刻膠的涂覆與刮邊工藝的研究

【「大話芯片制造」閱讀體驗(yàn)】+ 芯片制造過(guò)程和生產(chǎn)工藝

芯片濕法蝕刻工藝

【「大話芯片制造」閱讀體驗(yàn)】+芯片制造過(guò)程工藝面面觀

簡(jiǎn)述光刻工藝的三個(gè)主要步驟

光刻工藝的基本知識(shí)

通過(guò)光刻和蝕刻工藝順序提高整個(gè)晶圓的關(guān)鍵尺寸均勻性(1)

通過(guò)光刻和蝕刻工藝順序提高整個(gè)晶圓的關(guān)鍵尺寸均勻性(1)

評(píng)論