從理論上講,異構(gòu)多核設(shè)備可以配備一個(gè)計(jì)算塊,該計(jì)算塊針對(duì)給定用例的任何類(lèi)型的操作進(jìn)行了優(yōu)化。用于視頻處理的 GPU、用于對(duì)象識(shí)別的神經(jīng)網(wǎng)絡(luò)處理器、運(yùn)行操作系統(tǒng)的 CPU 等等。與同級(jí)別的同質(zhì)處理器相比,不同用途的內(nèi)核為 SoC 提供了更大的靈活性,因此在更廣泛的工作負(fù)載范圍內(nèi)具有更高的性能和更低的功耗。

但當(dāng)您開(kāi)始考慮基于邊緣的 AI、計(jì)算機(jī)視覺(jué)等應(yīng)用程序的要求時(shí),事實(shí)是 I/O 和內(nèi)存變得與原始處理性能一樣受到限制,甚至更多。

“內(nèi)存速度只會(huì)這么快,對(duì)吧?” 英偉達(dá)嵌入式與邊緣計(jì)算副總裁兼總經(jīng)理 Deepu Talla “它并沒(méi)有呈指數(shù)級(jí)增長(zhǎng)。由于大小,位寬大致相同:它可以是 16 位、32 位、64 位、128 位,等等。大多數(shù)嵌入式處理器通常具有 32 位甚至 16 位接口,這也是出于成本和尺寸的原因。

“內(nèi)存的速度只是一代比一代增長(zhǎng) 2 倍,而且這通常每三年發(fā)生一次,”他繼續(xù)說(shuō)道。“然而,SoC 中的計(jì)算需求可能增加了 10 倍或 20 倍。”

您如何協(xié)調(diào)計(jì)算性能的這種不成比例的增長(zhǎng)與內(nèi)存技術(shù)的相對(duì)較小的進(jìn)步?特別是當(dāng)處理器演變成獨(dú)特的邏輯集合時(shí),它們都需要自己訪問(wèn)內(nèi)存等資源。

根據(jù)塔拉的說(shuō)法,你把它給了他們。以下是嵌入式存儲(chǔ)器架構(gòu)為滿(mǎn)足下一代異構(gòu)多核處理器的需求而發(fā)展的三種方式。

1、內(nèi)核專(zhuān)用 SRAM

“如果你看很多這些嵌入式處理器,它們過(guò)去一直都有 SRAM,”Talla 說(shuō)。“現(xiàn)在,對(duì)于每個(gè)特定單元,我們都有本地 SRAM,它從 DRAM 獲取數(shù)據(jù),在本地存儲(chǔ)并處理它,然后發(fā)回最終輸出。”

特定于內(nèi)核的 SRAM 提供了幾個(gè)優(yōu)勢(shì),首先是由于不必將臨時(shí)數(shù)據(jù)寫(xiě)回片外 DRAM 所帶來(lái)的內(nèi)存性能提升。

這種架構(gòu)還具有降低功耗的額外好處,因?yàn)槌碗妷?SRAM 模塊位于 SoC 內(nèi)相應(yīng)的邏輯 IP 附近或附近。

“如果你使用 DRAM,這可能是一個(gè)數(shù)量級(jí)的功率,所以你實(shí)際上是通過(guò)使用這些技術(shù)來(lái)節(jié)省功率,”Talla 解釋道。

2、增加系統(tǒng)內(nèi)存

今天的嵌入式處理器具有高達(dá) 4 MB 到 8 MB 的系統(tǒng)內(nèi)存。此系統(tǒng)內(nèi)存并非專(zhuān)用于任何特定內(nèi)核,并且可以在 CPU、GPU 和加速器等元素之間共享。

與專(zhuān)用 SRAM 類(lèi)似,更多共享系統(tǒng)內(nèi)存的主要好處是更少的 DRAM 訪問(wèn)。例如,傳統(tǒng)的視頻編碼序列如下所示:

DRAM -》 視頻編碼器 -》 DRAM -》 附加計(jì)算 -》 DRAM

增加的系統(tǒng)緩存可以實(shí)現(xiàn)這一點(diǎn):

DRAM -》 視頻編碼器 -》 系統(tǒng)內(nèi)存 -》 附加計(jì)算 -》 DRAM

如前所述,不同之處在于單獨(dú)的內(nèi)核不必不斷地從片外 DRAM 中獲取數(shù)據(jù),因?yàn)榇笙到y(tǒng)內(nèi)存消除了對(duì)中間步驟的需要。

3、增加緩存大小

最后,隨著更新的工藝技術(shù)使更高容量的內(nèi)存更便宜,緩存大小將不可避免地增加。在異構(gòu) SoC 上發(fā)現(xiàn)的用于 CPU、GPU、DSP 和其他核心架構(gòu)的更大緩存也將減少 DRAM 流量。

并且將增加的緩存大小與前兩個(gè)進(jìn)步配對(duì)開(kāi)始產(chǎn)生一些重大收益。

“更多的 SRAM、通用的系統(tǒng)內(nèi)存以及更多的大容量緩存可以讓您在接下來(lái)的三到五年內(nèi)將性能提高 10 倍到 100 倍,即使內(nèi)存帶寬可能只增加了一倍或四倍,”Talla 指出出去。

審核編輯:郭婷

-

嵌入式

+關(guān)注

關(guān)注

5143文章

19567瀏覽量

315609 -

DRAM

+關(guān)注

關(guān)注

40文章

2343瀏覽量

185273 -

編碼器

+關(guān)注

關(guān)注

45文章

3782瀏覽量

137380

發(fā)布評(píng)論請(qǐng)先 登錄

精選好文!噪聲系數(shù)測(cè)量的三種方法

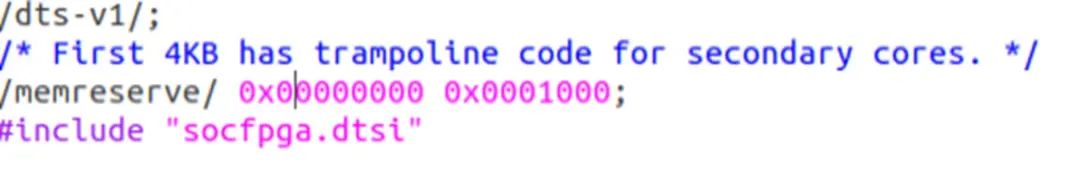

Linux系統(tǒng)中通過(guò)預(yù)留物理內(nèi)存實(shí)現(xiàn)ARM與FPGA高效通信的方法

如何提高嵌入式代碼質(zhì)量?

什么是嵌入式人工智能

基于全志T113-i多核異構(gòu)處理器的全國(guó)產(chǎn)嵌入式核心板簡(jiǎn)介

飛凌嵌入式FET6254-C核心板為智能運(yùn)動(dòng)控制系統(tǒng)強(qiáng)力賦能

【「嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用」閱讀體驗(yàn)】+ 了解Hypervisor

Windows管理內(nèi)存的三種主要方式

【「嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用」閱讀體驗(yàn)】+全文學(xué)習(xí)心得

嵌入式系統(tǒng)的未來(lái)趨勢(shì)有哪些?

七大嵌入式GUI盤(pán)點(diǎn)

學(xué)習(xí)hypervisor嵌入式產(chǎn)品安全設(shè)計(jì)

MCUXpresso IDE下在線(xiàn)聯(lián)合調(diào)試雙核MCU工程的三種方法

為異構(gòu)多核實(shí)現(xiàn)十倍嵌入式內(nèi)存性能的三種方法

為異構(gòu)多核實(shí)現(xiàn)十倍嵌入式內(nèi)存性能的三種方法

評(píng)論