2021 年連接的物聯(lián)網(wǎng)設(shè)備數(shù)量超過 460 億,預(yù)計(jì)到 2030 年將達(dá)到驚人的 1250 億。這將顯著改變半導(dǎo)體市場(chǎng),因?yàn)槊總€(gè)物聯(lián)網(wǎng)設(shè)備都需要一個(gè)處理器內(nèi)核來有效處理大量數(shù)據(jù)和相關(guān)交易。為了充分利用這種市場(chǎng)潛力,RISC-V 架構(gòu)已成為 SoC 設(shè)計(jì)人員替代 x86 或 ARM 的新選擇,這要?dú)w功于其開放的指令格式和低成本。

然而,隨著物聯(lián)網(wǎng)市場(chǎng)的不斷擴(kuò)大,對(duì)抗性攻擊的破壞性也在不斷擴(kuò)大。連接應(yīng)用程序的安全性現(xiàn)在是其設(shè)計(jì)的基本要素。連接的設(shè)備必須能夠相互驗(yàn)證,確保安全的數(shù)據(jù)傳輸,并包括安全存儲(chǔ)。雖然RISC-V 的安全指南仍在制定中,但為 RISC-V 用戶提供有效的即插即用解決方案以加強(qiáng) SoC 及其他產(chǎn)品的安全性至關(guān)重要。

需要什么樣的設(shè)計(jì)來保護(hù)物聯(lián)網(wǎng)應(yīng)用?

在大多數(shù)情況下,需要考慮六個(gè)關(guān)鍵的 SoC 安全因素……

可信執(zhí)行環(huán)境 (TEE):隔離需要更高安全級(jí)別的代碼、數(shù)據(jù)和內(nèi)存。

信任根:保護(hù)關(guān)鍵的安全參數(shù);包括唯一 ID、證書、密鑰和安全存儲(chǔ)。

安全啟動(dòng):阻止未經(jīng)授權(quán)的操作系統(tǒng)和應(yīng)用程序運(yùn)行。

靜態(tài)數(shù)據(jù)安全性:以加密/模糊的形式存儲(chǔ)數(shù)據(jù),具有可靠的訪問控制以防止泄漏。

傳輸中的數(shù)據(jù)安全性:在傳輸前利用密鑰對(duì)數(shù)據(jù)進(jìn)行加密,以防止被截取。

安全 OTA 更新:確保現(xiàn)場(chǎng)的固件或軟件更新以加密密文形式提供,并且不允許降級(jí)。

僅靠 CPU 無法達(dá)到這六個(gè)安全因素。芯片的設(shè)計(jì)需要一個(gè)密鑰存儲(chǔ)單元和一組密碼算法來幫助 CPU 執(zhí)行安全功能,包括身份驗(yàn)證、加密、解密和完整性檢查,以實(shí)現(xiàn)這些功能。此外,安全操作(與非安全操作分開)需要一個(gè)隔離且可信的安全執(zhí)行環(huán)境。還應(yīng)實(shí)施防篡改設(shè)計(jì),以保護(hù)安全環(huán)境免受攻擊。

考慮到這些風(fēng)險(xiǎn),經(jīng)驗(yàn)豐富的設(shè)計(jì)人員通常會(huì)使用帶有硬件信任根和防篡改設(shè)計(jì)的安全協(xié)處理器,以支持 CPU 執(zhí)行應(yīng)用程序和服務(wù)的所有必要安全功能。

彌補(bǔ)現(xiàn)有協(xié)處理器的不足

安全協(xié)處理器負(fù)責(zé)系統(tǒng)內(nèi)與安全相關(guān)的事務(wù),并允許 CPU 安全地執(zhí)行其主要功能。實(shí)施后,硬件加速的安全協(xié)處理器將保護(hù)敏感信息并比 CPU 更有效地執(zhí)行安全功能,而不會(huì)影響其計(jì)算能力。這不僅簡化了系統(tǒng)設(shè)計(jì),而且提高了整體性能。

在其架構(gòu)中,ARM 提供與其 CPU 集成的 CryptoCell-312 作為安全協(xié)處理器來處理安全操作。相比之下,RISC-V 生態(tài)系統(tǒng)仍在成熟,還沒有適合安全協(xié)處理器的解決方案。RISC-V 用戶必須自行開發(fā)或采用合作伙伴的 IP 才能獲得上述安全功能。如果他們選擇內(nèi)部開發(fā),可能會(huì)出現(xiàn)一些挑戰(zhàn)。他們有足夠能力的安全開發(fā)團(tuán)隊(duì)嗎?它將如何影響上市時(shí)間?自主研發(fā)的安全功能能否獲得認(rèn)證?當(dāng)技術(shù)問題出現(xiàn)時(shí),他們處理的能力如何?最后,成本是多少?所有這些挑戰(zhàn)都可以通過采用來自有能力的合作伙伴的集成 IP 來避免。

現(xiàn)有解決方案缺乏全面的硬件信任根,也沒有提供穩(wěn)固的安全邊界,因此容易受到攻擊。市場(chǎng)上的大多數(shù)安全協(xié)處理器可能涵蓋一到兩個(gè)關(guān)鍵功能,但不足。例如,一些協(xié)處理器不支持某些加密算法,容易受到攻擊,或者沒有通過第 3 方認(rèn)證。有些沒有為密鑰提供安全存儲(chǔ),導(dǎo)致協(xié)處理器從安全邊界之外檢索密鑰(想象將您的密鑰留在前門的保險(xiǎn)庫)。即使包括安全密鑰存儲(chǔ)在內(nèi)的選項(xiàng)也存在不可避免的缺點(diǎn),需要在生產(chǎn)過程中將密鑰一一注入芯片,這使得制造或操作成本高昂且難以操作。一些協(xié)處理器對(duì)所有產(chǎn)品都有相同的激活密鑰,

所有這些不足之處最終都可能成為物聯(lián)網(wǎng)設(shè)備中的漏洞,這將不可避免地成為黑客入侵網(wǎng)絡(luò)的目標(biāo)。因此,即使是僅傳輸非敏感數(shù)據(jù)的微型物聯(lián)網(wǎng)設(shè)備,如果被黑客操縱也可能造成巨大傷害。類似的事件數(shù)不勝數(shù),最近的一次是 2021 年 5 月,當(dāng)時(shí)最大的輸油管道系統(tǒng) Colonial Pipeline 遭到攻擊。他們不僅關(guān)閉了整個(gè)管道,政府甚至還發(fā)布了區(qū)域緊急聲明。僅支付的贖金就損失了420萬美元。

PUFiot 支持 RISC-V 架構(gòu)的片上安全性

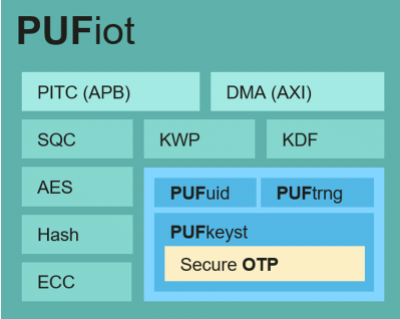

為了解決 RISC-V 生態(tài)系統(tǒng)中缺乏完整的安全協(xié)處理器的問題,PUFsecurity 的集成 IP 解決方案之一 PUFiot,是終極答案。它受到多層設(shè)計(jì)的保護(hù),利用了一整套完全集成的硬件安全 IP。與純粹基于軟件的設(shè)計(jì)不同,PUFiot 的安全邊界基于硬件的物理分離,因此建立了完善的可信執(zhí)行環(huán)境 (TEE)。圖 1 展示了 PUFiot 的設(shè)計(jì)架構(gòu)。PUFiot 的核心是模擬硬件信任根設(shè)計(jì)。硬件信任根包含 eMemory 的專利 NeoPUF,為每個(gè)芯片提供唯一的芯片指紋 (UID),并提供 Riscure 認(rèn)證的防篡改安全 OTP 用于密鑰存儲(chǔ),防止對(duì)關(guān)鍵安全參數(shù)的物理/電氣攻擊。硬件信任根還帶有一個(gè)真隨機(jī)數(shù)生成器 (TRNG),

圖1:PUFiot的設(shè)計(jì)架構(gòu)

PUFiot 支持一整套 NIST CAVP 認(rèn)證和第 3 方認(rèn)證的中國 OSCCA 硬件密碼算法。由于模塊化設(shè)計(jì),PUFiot 加密算法的定制仍然很靈活。這意味著用戶的要求,例如在 SM4 和 AES 之間進(jìn)行選擇,可以在一個(gè)簡單的過程中得到滿足。因此,PUFiot 可以滿足 RISC-V 當(dāng)前和未來的安全要求。除了安全功能外,眾多的數(shù)字和模擬防篡改設(shè)計(jì)進(jìn)一步加強(qiáng)了 PUFiot,使其成為可靠的安全協(xié)處理器。同樣,為了降低整個(gè) SoC 系統(tǒng)設(shè)計(jì)的復(fù)雜性,PUFiot 支持用于寄存器訪問控制的標(biāo)準(zhǔn) APB 控制接口和具有標(biāo)準(zhǔn) AXI4 控制接口的 DMA,以快速訪問存儲(chǔ)在系統(tǒng)內(nèi)存中的大量數(shù)據(jù)。

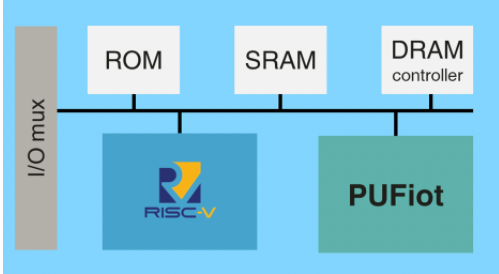

連同 NIST 標(biāo)準(zhǔn)的密鑰包裝 (KWP) 和密鑰派生函數(shù) (KDF) 以保護(hù)密鑰的使用和導(dǎo)出,PUFiot 可以為 RISC-V 物理內(nèi)存保護(hù) (PMP) 按需生成多個(gè)密鑰,以分別保護(hù)每個(gè)應(yīng)用程序。此外,PUF 的特性非常適用于安全啟動(dòng)和安全 OTA 更新,因?yàn)椴煌锫?lián)網(wǎng)設(shè)備上的相同軟件每個(gè)都有其密鑰。因此,我們可以為即將進(jìn)入市場(chǎng)的數(shù)十億新物聯(lián)網(wǎng)設(shè)備奠定堅(jiān)實(shí)的安全基礎(chǔ)。圖 2 顯示了以 PUFiot 作為其安全協(xié)處理器的 RISC-V SoC 設(shè)計(jì)。

圖 2:包含 PUFiot 的 RISC-V SoC 設(shè)計(jì)

結(jié)論

為了保護(hù) IoT 應(yīng)用程序,PUFsecurity 利用芯片指紋技術(shù)來強(qiáng)化信任根,并開發(fā)了 PUFiot,這是一種具有廣泛安全邊界的安全協(xié)處理器,可以輕松集成到安全的 RISC-V 系統(tǒng)中。PUFiot 支持物聯(lián)網(wǎng)世界所需的零接觸部署。通過硬件加速的安全功能和訪問控制,PUFiot 還滿足云應(yīng)用中的零信任安全要求。因此,PUFiot 作為一種安全解決方案非常適合配備 RISC-V 處理器的物聯(lián)網(wǎng)設(shè)備。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19799瀏覽量

233434 -

芯片

+關(guān)注

關(guān)注

459文章

52145瀏覽量

435734 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2927文章

45847瀏覽量

387577

發(fā)布評(píng)論請(qǐng)先 登錄

HPM5E31IGN單核 32 位 RISC-V 處理器

HXS320F28027數(shù)字信號(hào)處理器(32位RISC-V DSP)

新思科技RISC-V處理器助力低功耗嵌入式應(yīng)用

關(guān)于RISC-V芯片的應(yīng)用學(xué)習(xí)總結(jié)

RISC-V MCU技術(shù)

Imagination放棄RISC-V處理器內(nèi)核開發(fā)

Andes晶心科技推出D45-SE RISC-V處理器

Rivos全新產(chǎn)品采用Andes晶心科技NX45 RISC-V處理器

《RISC-V能否復(fù)制Linux 的成功?》

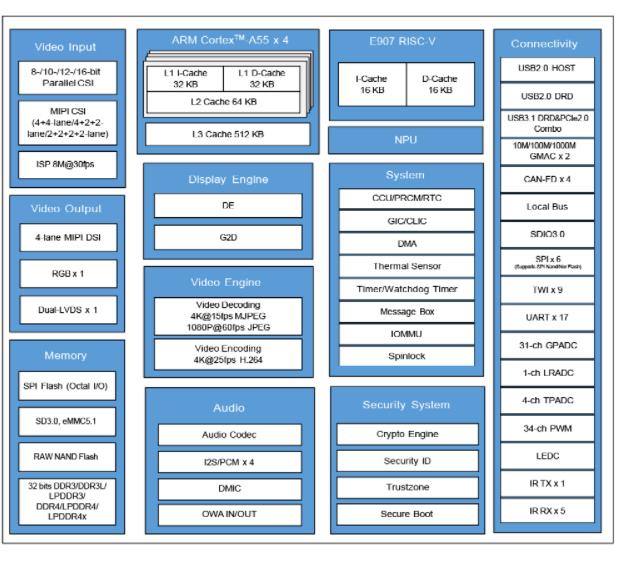

全志T536系列處理器特性概述 集成RISC-V E907協(xié)處理器

RISC-V設(shè)計(jì)的基本安全協(xié)處理器PUFiot

RISC-V設(shè)計(jì)的基本安全協(xié)處理器PUFiot

評(píng)論