(signal integrity)及時(shí)間延遲(timing

delay)。

8、如何處理實(shí)際布線中的一些理論沖突的問(wèn)題

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內(nèi)容有幫助可以關(guān)注、點(diǎn)贊、評(píng)論支持一下哦

發(fā)表于 05-21 17:21

在電子設(shè)計(jì)領(lǐng)域,原理圖和PCB設(shè)計(jì)是產(chǎn)品開(kāi)發(fā)的基石,但設(shè)計(jì)過(guò)程中難免遇到各種問(wèn)題,若不及時(shí)排查可能影響電路板的性能及可靠性,本文將列出原理圖和PCB設(shè)計(jì)

![的頭像]() 發(fā)表于

發(fā)表于 05-15 14:34

?174次閱讀

不要在耳機(jī)座子、功放芯片以及喇叭座子下面穿過(guò) ,以影響信號(hào)質(zhì)量。

四、AUDIO音頻接口PCB可制造性設(shè)計(jì)

1、阻抗線

在制造過(guò)程中阻抗線

發(fā)表于 03-19 14:31

。

2. 差分走線差分信號(hào)(Differential Signal)在高速電路設(shè)計(jì)中的應(yīng)用越來(lái)越

發(fā)表于 03-13 11:35

一、LVDS連接器:高速傳輸?shù)年P(guān)鍵組件

在現(xiàn)代設(shè)計(jì)電子中,數(shù)據(jù)傳輸?shù)乃俣群头€(wěn)定性至關(guān)重要。LVDS(低電壓差分信號(hào))連接器憑借其高速、低功耗、抗干擾能力強(qiáng)等特點(diǎn),成為眾多應(yīng)用領(lǐng)域的首選

發(fā)表于 02-18 18:18

,說(shuō)回正題吧。下面我們舉一個(gè)例子來(lái)體會(huì)一下射頻信號(hào)的設(shè)計(jì)卷度。下面的某個(gè)我們合作客戶的射頻項(xiàng)目,鏈路中含有各種衰減、放大、匹配、開(kāi)關(guān)鏈路,通過(guò)表層走線進(jìn)行連接,實(shí)現(xiàn)最終的功能。鏈路工作的頻率超過(guò)

發(fā)表于 02-17 14:41

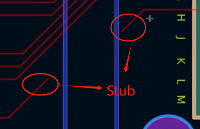

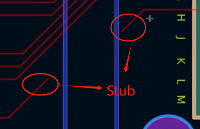

PCB設(shè)計(jì)中應(yīng)盡量減少Stub的存在,或者在無(wú)法完全避免Stub的情況下,通過(guò)優(yōu)化Stub的長(zhǎng)度和幾何形狀來(lái)降低它們對(duì)信號(hào)的影響。

![的頭像]() 發(fā)表于

發(fā)表于 12-20 18:28

?215次閱讀

ad,cadense 阻抗匹配計(jì)算和差分走線設(shè)置

發(fā)表于 10-17 16:59

?2次下載

過(guò)程中產(chǎn)生的電磁場(chǎng)對(duì)其他設(shè)備或系統(tǒng)造成的干擾,而EMS則是指設(shè)備或系統(tǒng)對(duì)外部電磁場(chǎng)的敏感程度。以下將從多個(gè)方面詳細(xì)探討在PCB設(shè)計(jì)中如何有效降低EMC問(wèn)題。

![的頭像]() 發(fā)表于

發(fā)表于 10-09 11:47

?802次閱讀

一站式PCBA智造廠家今天為大家講講什么是PCB設(shè)計(jì)爬電距離?PCB設(shè)計(jì)爬電距離的重要性。在電子制造業(yè)中,

![的頭像]() 發(fā)表于

發(fā)表于 09-26 09:39

?953次閱讀

詳細(xì)探討差分信號(hào)的幾個(gè)顯著優(yōu)點(diǎn),這些特點(diǎn)使其在許多高端電子設(shè)計(jì)中成為首選的信號(hào)傳輸方式。 強(qiáng)大的抗干擾能力:在充滿電磁噪聲的環(huán)境

![的頭像]() 發(fā)表于

發(fā)表于 09-10 10:30

?1057次閱讀

射頻(RF)電路的PCB設(shè)計(jì)是一個(gè)復(fù)雜且要求精確的過(guò)程,涉及到信號(hào)完整性、電磁兼容性、熱管理、材料選擇等多個(gè)方面。 射頻電路PCB設(shè)計(jì)概述 1. 信號(hào)完整性(SI) 阻抗匹配 :確保傳輸線

![的頭像]() 發(fā)表于

發(fā)表于 09-07 10:02

?1086次閱讀

在PCB設(shè)計(jì)中,坐標(biāo)原點(diǎn)是一個(gè)非常重要的概念,它決定了PCB布局的起始位置和方向。 一、坐標(biāo)原點(diǎn)

![的頭像]() 發(fā)表于

發(fā)表于 09-02 14:45

?4103次閱讀

一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)與PCB制板有什么關(guān)系?PCB設(shè)計(jì)與PCB制板的關(guān)系。PC

![的頭像]() 發(fā)表于

發(fā)表于 08-12 10:04

?917次閱讀

/O接口,信號(hào)走線和參考平面都是將信號(hào)從PCB上的一個(gè)位置傳輸?shù)搅?b class='flag-5'>一個(gè)位置所必需的。對(duì)于差分I/O接口,傳輸

發(fā)表于 07-19 16:56

探討一下在PCB設(shè)計(jì)中的差分走線

探討一下在PCB設(shè)計(jì)中的差分走線

評(píng)論