信號反射現象

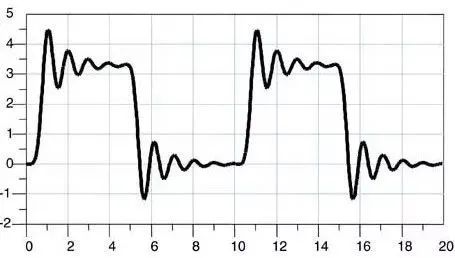

信號傳輸過程中感受到阻抗的變化,就會發生信號的反射。這個信號可能是驅動端發出的信號,也可能是遠端反射回來的反射信號。根據反射系數的公式,當信號感受到阻抗變小,就會發生負反射,反射的負電壓會使信號產生下沖。信號在驅動端和遠端負載之間多次反射,其結果就是信號振鈴。大多數芯片的輸出阻抗都很低,如果輸出阻抗小于PCB走線的特性阻抗,那么在沒有源端端接的情況下,必然產生信號振鈴。

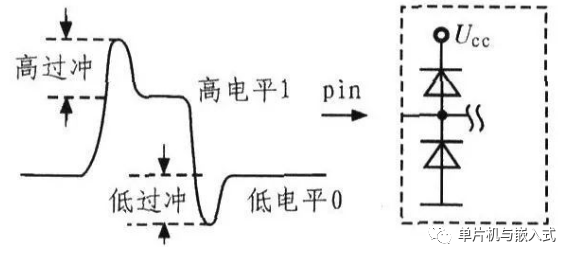

什么是過沖(overshoot):過沖就是第一個峰值或谷值超過設定電壓——對于上升沿是指最高電壓而對于下降沿是指最低電壓。

什么是下沖(undershoot):下沖是指下一個谷值或峰值。過分的過沖能夠引起保護二極管工作,導致過早地失效。過分的下沖能夠引起假的時鐘或數據錯誤(誤作)。

過沖非常相關的是振鈴,它緊隨過沖發生,信號會跌落到低于穩態值,然后可能會反彈到高于穩態,這個過程可能持續一段時間,直到穩定接近于穩態。振鈴持續的時間也叫做安定時間。振蕩(ringing)和環繞振蕩(rounding)的現象是反復出現過沖和下沖。

抑制信號反射等電路設計技巧

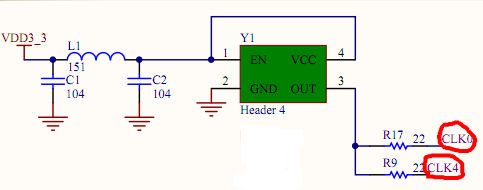

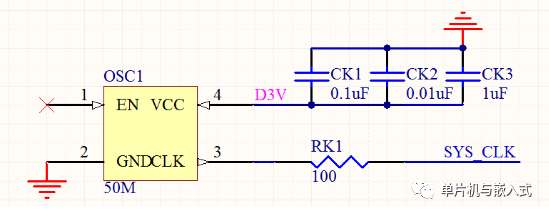

如果時鐘信號鏈路比較長,為了解決信號反射問題,會在時鐘輸出信號上串接一個比如22或者33歐姆的小電阻。相關文章推薦:認識傳輸線的三個特性,特性阻抗、反射、阻抗匹配。

而且隨著電阻的加大,振鈴會消失,然而信號上升沿不再那么陡峭了,串聯電阻是為了減小反射波,避免反射波疊加引起過沖。

這個解決方法叫阻抗匹配,阻抗在信號完整性問題中占據著極其重要的地位。

編輯:jq

-

電阻

+關注

關注

87文章

5606瀏覽量

174314 -

電路設計

+關注

關注

6697文章

2518瀏覽量

210563 -

歐姆

+關注

關注

0文章

82瀏覽量

21441

原文標題:信號反射問題與相關電路設計技巧

文章出處:【微信號:c-stm32,微信公眾號:STM32嵌入式開發】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于運算放大器和模擬集成電路的電路設計(第3版)

【「典型電子電路設計與測試」閱讀體驗】信號隔離電路

時域反射計的技術原理和應用場景

ADS1294 RLD相關的外圍電路設計和每個引腳代表的意義?

TechWiz LCD 3D應用:表面反射(底面)

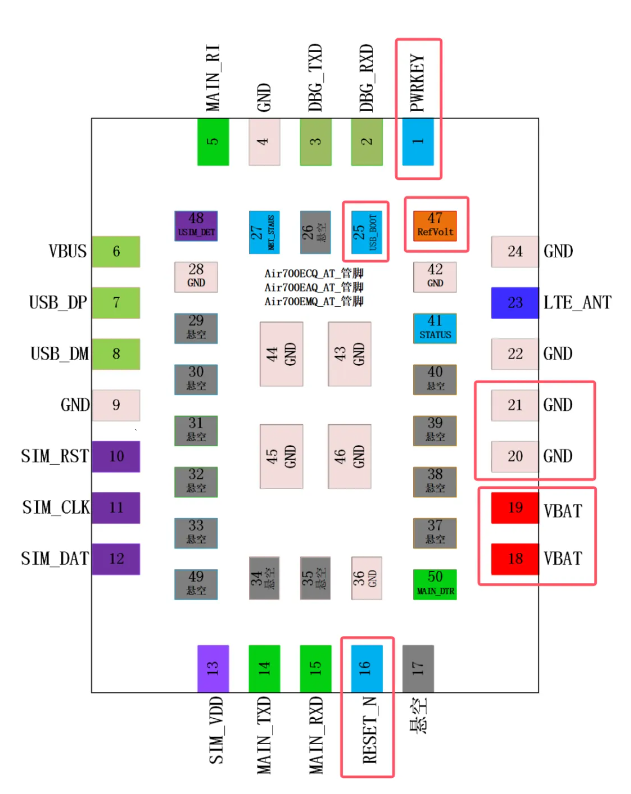

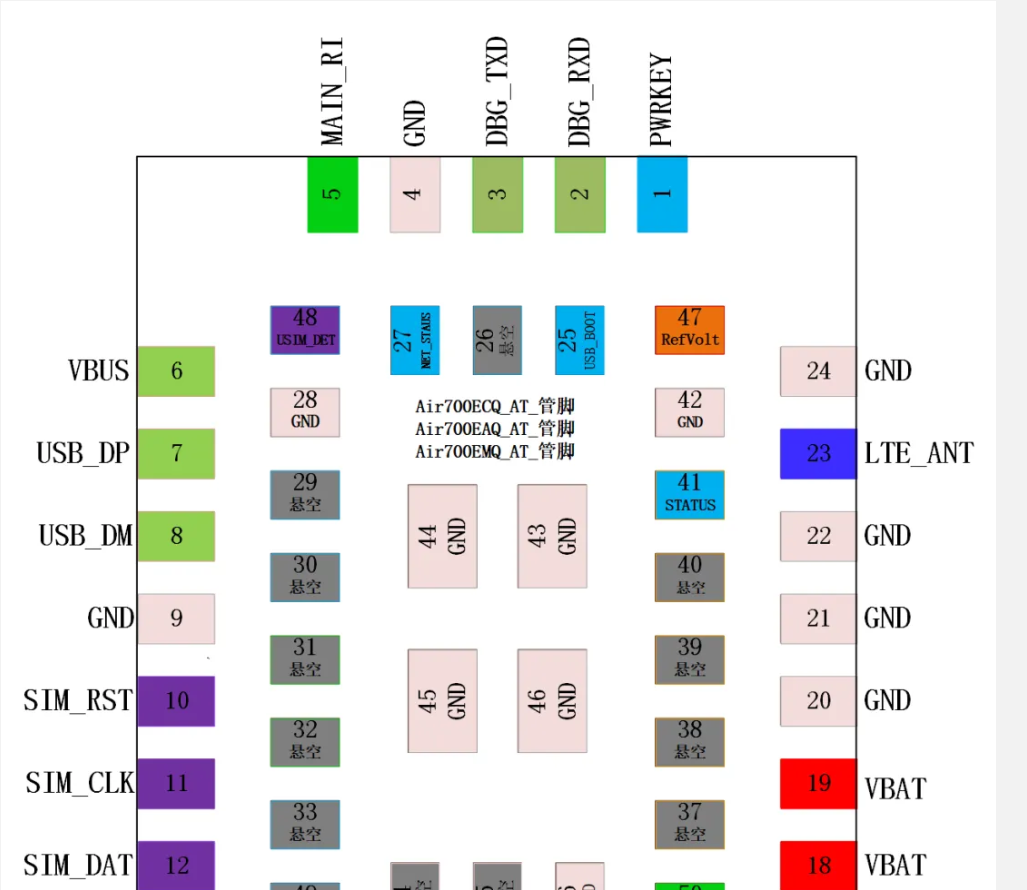

技術分享!蜂窩模組開機電路設計

信號反射問題與相關電路設計相關技巧分享

信號反射問題與相關電路設計相關技巧分享

評論